- 您现在的位置:买卖IC网 > PDF目录15531 > EVAL-ADUC842QS (Analog Devices Inc)KIT DEV FOR ADUC842 QUICK START PDF资料下载

参数资料

| 型号: | EVAL-ADUC842QS |

| 厂商: | Analog Devices Inc |

| 文件页数: | 10/88页 |

| 文件大小: | 0K |

| 描述: | KIT DEV FOR ADUC842 QUICK START |

| 标准包装: | 1 |

| 系列: | QuickStart™ 套件 |

| 类型: | MCU |

| 适用于相关产品: | ADuC842 |

| 所含物品: | 评估板、电源、缆线、软件和说明文档 |

| 产品目录页面: | 739 (CN2011-ZH PDF) |

第1页第2页第3页第4页第5页第6页第7页第8页第9页当前第10页第11页第12页第13页第14页第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页第29页第30页第31页第32页第33页第34页第35页第36页第37页第38页第39页第40页第41页第42页第43页第44页第45页第46页第47页第48页第49页第50页第51页第52页第53页第54页第55页第56页第57页第58页第59页第60页第61页第62页第63页第64页第65页第66页第67页第68页第69页第70页第71页第72页第73页第74页第75页第76页第77页第78页第79页第80页第81页第82页第83页第84页第85页第86页第87页第88页

ADuC841/ADuC842/ADuC843

Rev. 0 | Page 18 of 88

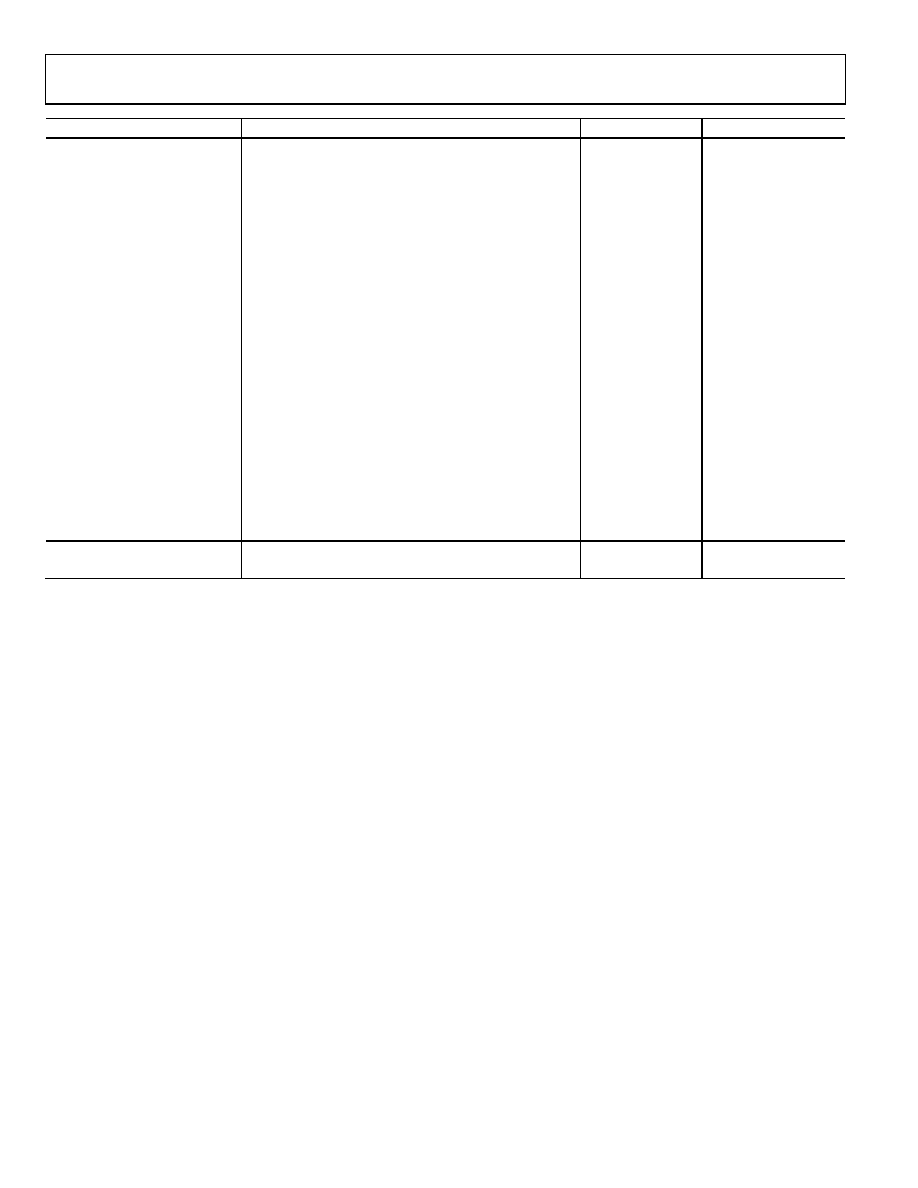

Mnemonic

Description

Bytes

Cycles

Branching

JMP @A+DPTR

Jump indirect relative to DPTR

1

3

RET

Return from subroutine

1

4

RETI

Return from interrupt

1

4

ACALL addr11

Absolute jump to subroutine

2

3

AJMP addr11

Absolute jump unconditional

2

3

SJMP rel

Short jump (relative address)

2

3

JC rel

Jump on carry equal to 1

2

3

JNC rel

Jump on carry equal to 0

2

3

JZ rel

Jump on accumulator = 0

2

3

JNZ rel

Jump on accumulator not equal to 0

2

3

DJNZ Rn,rel

Decrement register, JNZ relative

2

3

LJMP

Long jump unconditional

3

4

LCALL addr16

Long jump to subroutine

3

4

JB bit,rel

Jump on direct bit = 1

3

4

JNB bit,rel

Jump on direct bit = 0

3

4

JBC bit,rel

Jump on direct bit = 1 and clear

3

4

CJNE A,dir,rel

Compare A, direct JNE relative

3

4

CJNE A,#data,rel

Compare A, immediate JNE relative

3

4

CJNE Rn,#data,rel

Compare register, immediate JNE relative

3

4

CJNE @Ri,#data,rel

Compare indirect, immediate JNE relative

3

4

DJNZ dir,rel

Decrement direct byte, JNZ relative

3

4

Miscellaneous

NOP

No operation

1

1. One cycle is one clock.

2. Cycles of MOVX instructions are four cycles when they have 0 wait state. Cycles of MOVX instructions are 4 + n cycles when they have n wait states.

3. Cycles of LCALL instruction are three cycles when the LCALL instruction comes from interrupt.

OTHER SINGLE-CYCLE CORE FEATURES

Timer Operation

Timers on a standard 8052 increment by 1 with each machine

cycle. On the ADuC841/ADuC842/ADuC843, one machine

cycle is equal to one clock cycle; therefore the timers increment

at the same rate as the core clock.

ALE

The output on the ALE pin on a standard 8052 part is a clock at

1/6th of the core operating frequency. On the ADuC841/

ADuC842/ADuC843 the ALE pin operates as follows. For a

single machine cycle instruction,ALE is high for the first half of

the machine cycle and low for the second half. The ALE output

is at the core operating frequency. For a two or more machine

cycle instruction, ALE is high for the first half of the first

machine cycle and low for the rest of the machine cycles.

External Memory Access

There is no support for external program memory access on the

parts. When accessing external RAM, the EWAIT register may

need to be programmed to give extra machine cycles to MOVX

commands. This is to account for differing external RAM access

speeds.

EWAIT SFR

SFR Address

9FH

Power-On Default

00H

Bit Addressable

No

This special function register (SFR) is programmed with the

number of wait states for a MOVX instruction. This value can

range from 0H to 7H.

相关PDF资料 |

PDF描述 |

|---|---|

| V110C8C75BL | CONVERTER MOD DC/DC 8V 75W |

| AIUR-09-821K | INDUCTOR POWER 820UH 10% T/H |

| V110C8C75B3 | CONVERTER MOD DC/DC 8V 75W |

| V110C8C75B2 | CONVERTER MOD DC/DC 8V 75W |

| BQ2057PDGK | IC ADV LINEAR CHRG MGMT 8-MSOP |

相关代理商/技术参数 |

参数描述 |

|---|---|

| EVAL-ADUC842QS1 | 制造商:AD 制造商全称:Analog Devices 功能描述:MicroConverter 12-Bit ADCs and DACs with Embedded High Speed 62-kB Flash MCU |

| EVAL-ADUC842QSP1 | 制造商:AD 制造商全称:Analog Devices 功能描述:MicroConverter 12-Bit ADCs and DACs with Embedded High Speed 62-kB Flash MCU |

| EVAL-ADUC842QSP2 | 制造商:AD 制造商全称:Analog Devices 功能描述:MicroConverter 12-Bit ADCs and DACs with Embedded High Speed 62-kB Flash MCU |

| EVAL-ADUC842QSPZ | 功能描述:KIT DEV QUICK START ADUC842 RoHS:是 类别:编程器,开发系统 >> 通用嵌入式开发板和套件(MCU、DSP、FPGA、CPLD等) 系列:QuickStart™ PLUS 套件 标准包装:1 系列:PICDEM™ 类型:MCU 适用于相关产品:PIC10F206,PIC16F690,PIC16F819 所含物品:板,线缆,元件,CD,PICkit 编程器 产品目录页面:659 (CN2011-ZH PDF) |

| EVAL-ADUC842QS-U | 制造商:Analog Devices 功能描述:TOOLS:DEVELOPMENT BOARDS H/W 制造商:Analog Devices 功能描述:QUICK START DEVELOPMENT SYSTEM - Bulk |

发布紧急采购,3分钟左右您将得到回复。