- 您现在的位置:买卖IC网 > PDF目录16530 > EVAL-ADV7179EBZ (Analog Devices Inc)BOARD EVALUATION FOR ADV7179 PDF资料下载

参数资料

| 型号: | EVAL-ADV7179EBZ |

| 厂商: | Analog Devices Inc |

| 文件页数: | 19/52页 |

| 文件大小: | 0K |

| 描述: | BOARD EVALUATION FOR ADV7179 |

| 设计资源: | ADV7174/79 Eval Brd Docs |

| 标准包装: | 1 |

| 主要目的: | 视频,视频处理 |

| 嵌入式: | 否 |

| 已用 IC / 零件: | ADV7179 |

| 主要属性: | NTSC/PAL 数字视频编码器 |

| 次要属性: | I²C 接口 |

| 已供物品: | 板 |

第1页第2页第3页第4页第5页第6页第7页第8页第9页第10页第11页第12页第13页第14页第15页第16页第17页第18页当前第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页第29页第30页第31页第32页第33页第34页第35页第36页第37页第38页第39页第40页第41页第42页第43页第44页第45页第46页第47页第48页第49页第50页第51页第52页

ADV7174/ADV7179

Rev. B | Page 26 of 52

Frequency Registers 1, 2, and 3. The subcarrier frequency

registers should not be accessed independently.

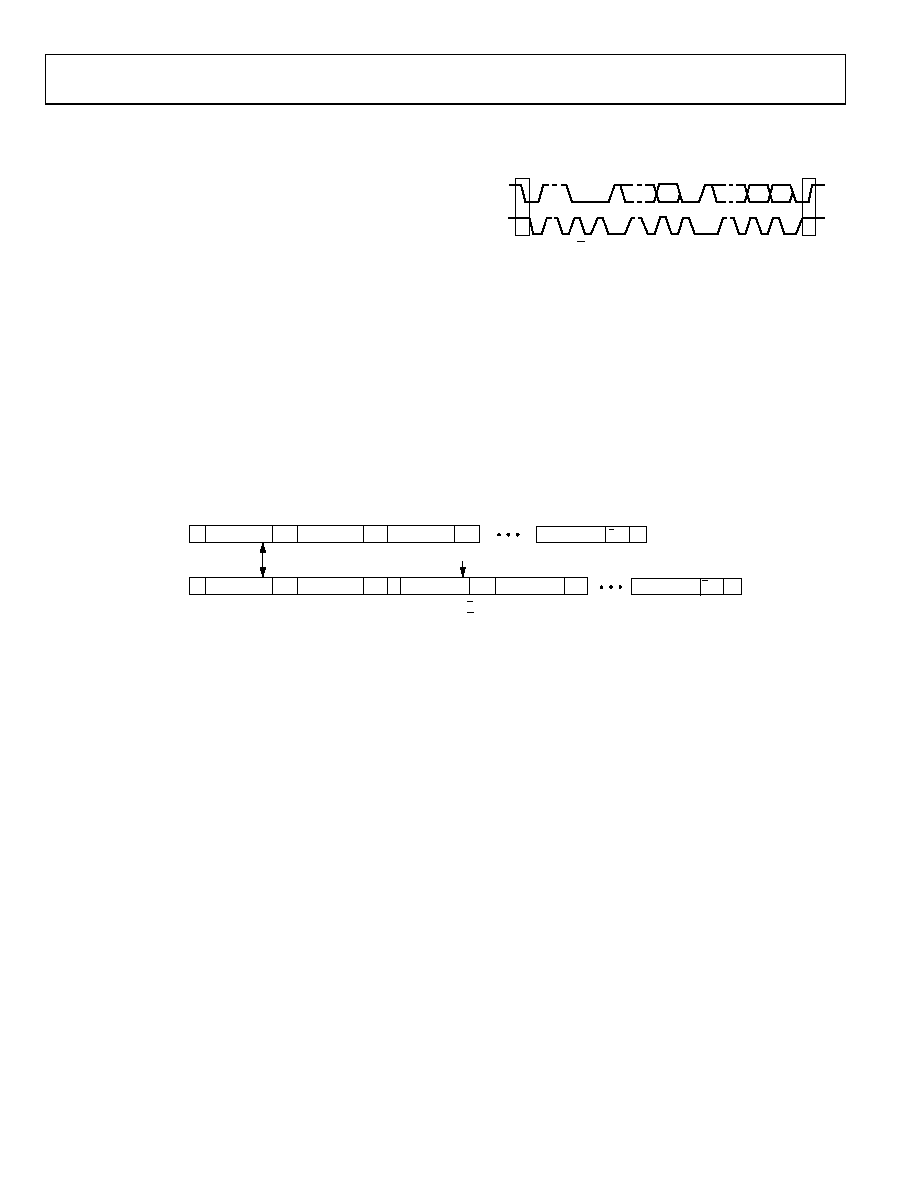

Figure 35 illustrates an example of data transfer for a read

sequence and the start and stop conditions.

Figure 36 shows bus write and read sequences.

Stop and start conditions can be detected at any stage during the

data transfer. If these conditions are asserted out of sequence with

normal read and write operations, they cause an immediate

jump to the idle condition. During a given SCLOCK high period,

the user should issue only one start condition, one stop condition,

or a single stop condition followed by a single start condition. If

an invalid subaddress is issued by the user, the ADV7174/

ADV7179 cannot issue an acknowledge and returns to the idle

condition. If in auto-increment mode the user exceeds the

highest subaddress, the following action is taken:

1–7

8

9

1–7

8

9

1–7

8

9

P

S

START ADDR R/W ACK SUBADDRESS ACK

DATA

ACK

STOP

SDATA

SCLOCK

02980-A-034

Figure 35. Bus Data Transfer

REGISTER ACCESSES

The MPU can write to or read from all of the ADV7174/

ADV7179 registers except the subaddress register, which is a

write-only register. The subaddress register determines which

register the next read or write operation accesses. All commu-

nications with the part through the bus start with an access to

the subaddress register. A read/write operation is performed

from to the target address, which then increments to the next

address until a stop command on the bus is performed.

1.

In read mode, the highest subaddress register contents

continues to be output until the master device issues a no-

acknowledge. This indicates the end of a read. A no-

acknowledge condition is when the SDATA line is not

pulled low on the ninth pulse.

2.

In write mode, the data for the invalid byte is not loaded

into any subaddress register, a no-acknowledge is issued by

the ADV7174/ADV7179, and the part returns to the idle

condition.

DATA

A(S)

S

SLAVE ADDR A(S)

SUB ADDR

A(S)

LSB = 0

LSB = 1

DATA

P

S

SLAVE ADDR A(S)

SUB ADDR

A(S) S

SLAVE ADDR

A(S)

DATA

A(M)

DATA

P

WRITE

SEQUENCE

READ

SEQUENCE

A(S) = NO-ACKNOWLEDGE BY SLAVE

A(M) = NO-ACKNOWLEDGE BY MASTER

A(S) = ACKNOWLEDGE BY SLAVE

A(M) = ACKNOWLEDGE BY MASTER

S = START BIT

P = STOP BIT

A(S)

A(M)

02980-A

-035

Figure 36. Write and Read Sequences

相关PDF资料 |

PDF描述 |

|---|---|

| CK21251R5M-T | INDUCTOR 1.5UH LAYER 0805 |

| VE-J0N-EZ-S | CONVERTER MOD DC/DC 18.5V 25W |

| H1AXH-6436G | IDC CABLE - HSC64H/AE64G/X |

| SP1812R-334K | INDUCTOR PWR SHIELDED 330UH SMD |

| UPJ1H820MPD1TD | CAP ALUM 82UF 50V 20% RADIAL |

相关代理商/技术参数 |

参数描述 |

|---|---|

| EVAL-ADV7180-32EBZ | 功能描述:BOARD EVAL FOR ADV7180 RoHS:是 类别:编程器,开发系统 >> 评估演示板和套件 系列:Advantiv® 标准包装:1 系列:- 主要目的:电信,线路接口单元(LIU) 嵌入式:- 已用 IC / 零件:IDT82V2081 主要属性:T1/J1/E1 LIU 次要属性:- 已供物品:板,电源,线缆,CD 其它名称:82EBV2081 |

| EVAL-ADV7180-48EBZ | 制造商:AD 制造商全称:Analog Devices 功能描述:10-Bit, 4?? Oversampling SDTV Video Decoder |

| EVAL-ADV7180-48EBZ-8P-CAL | 制造商:Analog Devices 功能描述: |

| EVAL-ADV7180LFEB | 制造商:Analog Devices 功能描述:ADV7180 EVAL BOARD - Bulk |

| EVAL-ADV7180LFEBZ | 功能描述:BOARD EVAL FOR ADV7180 LFCSP RoHS:是 类别:编程器,开发系统 >> 评估演示板和套件 系列:Advantiv® 标准包装:1 系列:PSoC® 主要目的:电源管理,热管理 嵌入式:- 已用 IC / 零件:- 主要属性:- 次要属性:- 已供物品:板,CD,电源 |

发布紧急采购,3分钟左右您将得到回复。