- 您现在的位置:买卖IC网 > PDF目录383012 > GM72V66841ELT-7J (HYNIX SEMICONDUCTOR INC) 2,097,152 WORD x 8 BIT x 4 BANK SYNCHRONOUS DYNAMIC RAM PDF资料下载

参数资料

| 型号: | GM72V66841ELT-7J |

| 厂商: | HYNIX SEMICONDUCTOR INC |

| 元件分类: | DRAM |

| 英文描述: | 2,097,152 WORD x 8 BIT x 4 BANK SYNCHRONOUS DYNAMIC RAM |

| 中文描述: | 8M X 8 SYNCHRONOUS DRAM, 6 ns, PDSO54 |

| 封装: | 0.400 INCH, TSOP2-54 |

| 文件页数: | 13/57页 |

| 文件大小: | 592K |

| 代理商: | GM72V66841ELT-7J |

第1页第2页第3页第4页第5页第6页第7页第8页第9页第10页第11页第12页当前第13页第14页第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页第29页第30页第31页第32页第33页第34页第35页第36页第37页第38页第39页第40页第41页第42页第43页第44页第45页第46页第47页第48页第49页第50页第51页第52页第53页第54页第55页第56页第57页

LG Semicon

GM72V66841CT/CLT

From [Precharge]

To [DESL], [NOP] or [BST]:

When these

commands are executed, the synchronous

DRAM enters the IDLE state after

t

RP

has

elapsed from the completion of Precharge

From [IDLE]

To [DESL], [NOP], [BST], [PRE] or

[PALL]:

These commands result in no

operation.

To [ACTV]:

The bank specified by the

address pins and the ROW address is

activated.

To [REF], [SELF]:

The synchronous

DRAM enters refresh mode (auto-refresh or

self-refresh).

To [MRS]:

The synchronous DRAM enters

the mode register set cycle.

From [ROW ACTIVE]

To [DESL], [NOP] or [BST]:

These

commands result in no operation.

To [READ], [READ A]:

A read operation

starts. (However, an interval of

t

RCD

is

required.)

To [WRIT], [WRIT A]:

A write operation

starts. (However, an interval of

t

RCD

is

required.)

To [ACTV]:

This command makes the

other bank active. (However, an interval of

t

RRD

is required.) Attempting to make the

currently active bank active results in an

illegal command.

To [PRE], [PALL]:

These commands set

the synchronous DRAM to Precharge

mode. (However, an interval of

t

RAS

is

required.)

12

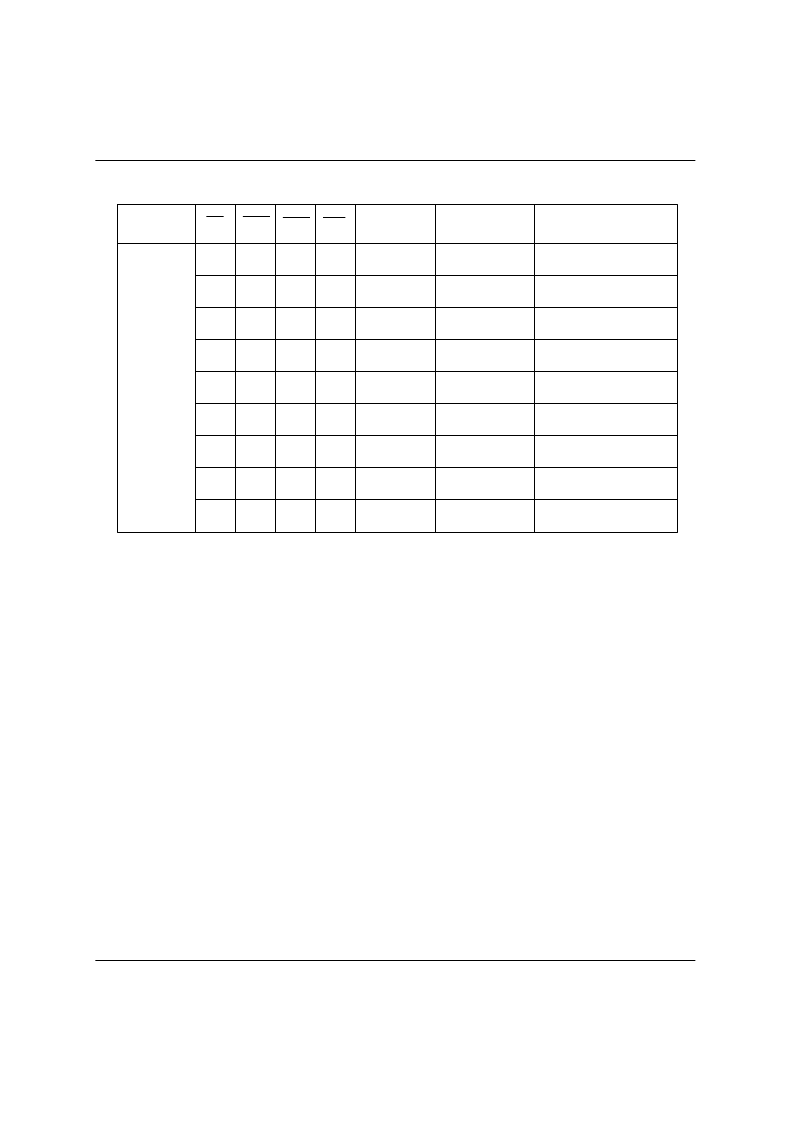

Function Truth Table (Continued)

Current

state

Refresh

(auto-refresh)

CS

RAS

CAS

WE

Address

L

H

H

H

X

L

H

H

L

X

L

H

L

H

BA, CA, A10

L

H

L

L

BA, CA, A10

L

L

H

H

BA, RA

L

L

H

L

BA, A10

L

L

L

H

X

L

L

L

L

MODE

Command

Operation

NOP

BST

READ/READ A

WRIT/WRIT A

ACTV

PRE, PALL

REF, SELF

MRS

Enter IDLE after

t

RC

Enter IDLE after

t

RC

ILLEGAL

ILLEGAL

ILLEGAL

H

X

X

X

X

DESL

Enter IDLE after

t

RC

ILLEGAL

ILLEGAL

ILLEGAL

* Notes : 1. H: V

IH

, L: V

IL

, X: V

IH

or V

IL

.

The other combinations are inhibit.

2. An interval of

t

RWL

is required between the final valid data input and the Precharge command.

3. If

t

RRD

is not satisfied, this operation is illegal.

4. BA:Bank Address, RA:Row Address, CA:Column Address

相关PDF资料 |

PDF描述 |

|---|---|

| GM72V66841ELT-7K | 2,097,152 WORD x 8 BIT x 4 BANK SYNCHRONOUS DYNAMIC RAM |

| GM72V66841ELT-8 | 2,097,152 WORD x 8 BIT x 4 BANK SYNCHRONOUS DYNAMIC RAM |

| GM72V66841ET | 2,097,152 WORD x 8 BIT x 4 BANK SYNCHRONOUS DYNAMIC RAM |

| GM72V66841Exx | 2,097,152 WORD x 8 BIT x 4 BANK SYNCHRONOUS DYNAMIC RAM |

| GM72V66841ELT-7 | 2,097,152 WORD x 8 BIT x 4 BANK SYNCHRONOUS DYNAMIC RAM |

相关代理商/技术参数 |

参数描述 |

|---|---|

| GM72V66841ELT-7K | 制造商:HYNIX 制造商全称:Hynix Semiconductor 功能描述:2,097,152 WORD x 8 BIT x 4 BANK SYNCHRONOUS DYNAMIC RAM |

| GM72V66841ELT-8 | 制造商:HYNIX 制造商全称:Hynix Semiconductor 功能描述:2,097,152 WORD x 8 BIT x 4 BANK SYNCHRONOUS DYNAMIC RAM |

| GM72V66841ET | 制造商:HYNIX 制造商全称:Hynix Semiconductor 功能描述:2,097,152 WORD x 8 BIT x 4 BANK SYNCHRONOUS DYNAMIC RAM |

| GM72V66841ET-7 | 制造商:HYNIX 制造商全称:Hynix Semiconductor 功能描述:2,097,152 WORD x 8 BIT x 4 BANK SYNCHRONOUS DYNAMIC RAM |

| GM72V66841ET-75 | 制造商:未知厂家 制造商全称:未知厂家 功能描述:x8 SDRAM |

发布紧急采购,3分钟左右您将得到回复。