参数资料

| 型号: | HD3-6408-9Z |

| 厂商: | Intersil |

| 文件页数: | 5/11页 |

| 文件大小: | 0K |

| 描述: | IC ASMA ADT CMOS 1.25MHZ 24DIP |

| 标准包装: | 90 |

| 类型: | Manchester 编码器/解码器 |

| 应用: | 安全系统 |

| 电压 - 电源,模拟: | 4.5 V ~ 5.5 V |

| 电压 - 电源,数字: | 4.5 V ~ 5.5 V |

| 安装类型: | 通孔 |

| 封装/外壳: | 24-DIP(0.600",15.24mm) |

| 供应商设备封装: | 24-PDIP |

| 包装: | 管件 |

3

FN2952.2

March 7, 2006

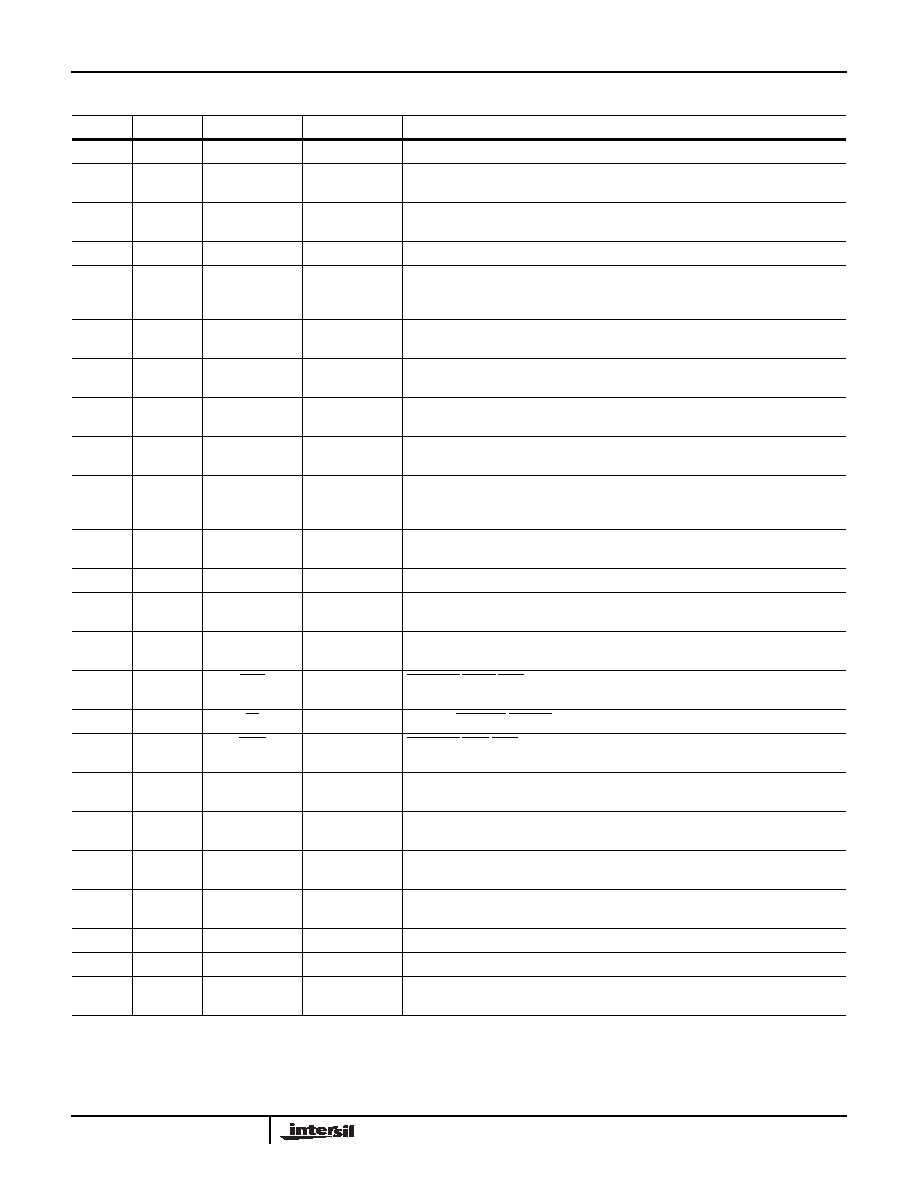

Pin Description

PIN

TYPE

SYMBOL

SECTION

DESCRIPTION

1

O

VW

Decoder

Output high indicates receipt of a VALID WORD.

2

O

ESC

Encoder

ENCODER SHIFT CLOCK is an output for shifting data into the Encoder. The

Encoder samples SDI on the low-to-high transition of ESC.

3

O

TD

Decoder

TAKE DATA output is high during receipt of data after identification of a sync pulse

and two valid Manchester data bits.

4

O

SDO

Decoder

SERIAL DATA OUT delivers received data in correct NRZ format.

5

I

DC

Decoder

DECODER CLOCK input drives the transition finder, and the synchronizer which in

turn supplies the clock to the balance of the Decoder. Input a frequency equal to

12X the data rate.

6

I

BZI

Decoder

A high input should be applied to BIPOLAR ZERO IN when the bus is in its negative

state. This pin must be held high when the Unipolar input is used.

7

I

BOI

Decoder

A high input should be applied to BIPOLAR ONE IN when the bus is in its positive

state, this pin must be held low when the Unipolar input is used.

8

I

UDI

Decoder

With pin 6 high and pin 7 low, this pin enters UNIPOLAR DATA IN to the transition

finder circuit. If not used this input must be held low.

9

O

DSC

Decoder

DECODER SHIFT CLOCK output delivers a frequency (DECODER CLOCK

÷ 12),

synchronized by the recovered serial data stream.

10

O

CDS

Decoder

COMMAND/DATA SYNC output high occurs during output of decoded data which

was preceded by a Command synchronizing character. A low output indicates a

Data synchronizing character.

11

I

DR

Decoder

A high input to DECODER RESET during a rising edge of DECODER SHIFT

CLOCK resets the decoder bit counting logic to a condition ready for a new word.

12

I

GND

Both

GROUND supply pin.

13

I

MR

Both

A high on MASTER RESET clears the 2:1 counters in both the encoder and

decoder and the

÷ 6 counter.

14

O

DBS

Encoder

DIVIDE BY SIX is an output from 6:1 divider which is driven by the ENCODER

CLOCK.

15

O

BZO

Encoder

BIPOLAR ZERO OUT is a active low output designed to drive the zero or negative

sense of a bipolar line driver.

16

I

OI

Encoder

A low on OUTPUT INHIBIT forces pin 15 and 17 high, their inactive states.

17

O

BOO

Encoder

BIPOLAR ONE OUT is an active low output designed to drive the one or positive

sense of a bipolar line driver.

18

I

SDI

Encoder

SERIAL DATA IN accepts a serial data stream at a data rate equal to ENCODER

SHIFT CLOCK.

19

I

EE

Encoder

A high on ENCODER ENABLE initiates the encode cycle. (Subject to the preceding

cycle being completed).

20

I

SS

Encoder

SYNC SELECT actuates a Command sync for an input high and data sync for an

input low.

21

O

SD

Encoder

SEND DATA is an active high output which enables the external source of serial

data.

22

I

SCI

Encoder

SEND CLOCK IN is 2X the Encoder data rate.

23

I

EC

Encoder

ENCODER CLOCK is the input to the 6:1 divider.

24

I

VCC

Both

VCC is the +5V power supply pin. A 0.1F decoupling capacitor from VCC (pin 24)

to GND (pin 12) is recommended.

HD-6408

相关PDF资料 |

PDF描述 |

|---|---|

| HI1-565AJD-5 | CONV D/A 12BIT 6.7MHZ 24-DIP |

| HI1171JCB-T | CONV D/A 8BIT 40MSPS HS 24-SOIC |

| HI1175JCB-T | CONV A/D 8BIT 20MSPS 24-SOIC |

| HI1178JCQ | CONV D/A 8BIT TRPL 40MHZ 48-PQFP |

| HI3-674AKN-5 | IC ADC 12BIT 67KSPS 28-SBDIP |

相关代理商/技术参数 |

参数描述 |

|---|---|

| HD3-6409-2 | 制造商:未知厂家 制造商全称:未知厂家 功能描述:Logic IC |

| HD3-6409-9 | 功能描述:编码器、解码器、复用器和解复用器 MANCHESTER 1MHZ 20PDIP IND RoHS:否 制造商:Micrel 产品:Multiplexers 逻辑系列:CMOS 位数: 线路数量(输入/输出):2 / 12 传播延迟时间:350 ps, 400 ps 电源电压-最大:2.625 V, 3.6 V 电源电压-最小:2.375 V, 3 V 最大工作温度:+ 85 C 安装风格:SMD/SMT 封装 / 箱体:QFN-44 封装:Tray |

| HD3-6409-9+ | 制造商:未知厂家 制造商全称:未知厂家 功能描述:Encoder/Decoder |

| HD3-6409-9Z | 功能描述:编码器、解码器、复用器和解复用器 W/ANNEAL MANCHESTER 1MHZ 20PDIP IND RoHS:否 制造商:Micrel 产品:Multiplexers 逻辑系列:CMOS 位数: 线路数量(输入/输出):2 / 12 传播延迟时间:350 ps, 400 ps 电源电压-最大:2.625 V, 3.6 V 电源电压-最小:2.375 V, 3 V 最大工作温度:+ 85 C 安装风格:SMD/SMT 封装 / 箱体:QFN-44 封装:Tray |

| HD3-6409C-9 | 制造商:Rochester Electronics LLC 功能描述:- Bulk |

发布紧急采购,3分钟左右您将得到回复。