- 您现在的位置:买卖IC网 > PDF目录371807 > HFA3842BIN-TK (INTERSIL CORP) PCMCIA/USB Wireless LAN Medium Access Controller PDF资料下载

参数资料

| 型号: | HFA3842BIN-TK |

| 厂商: | INTERSIL CORP |

| 元件分类: | 微控制器/微处理器 |

| 英文描述: | PCMCIA/USB Wireless LAN Medium Access Controller |

| 中文描述: | 1 CHANNEL(S), 11M bps, LOCAL AREA NETWORK CONTROLLER, PQFP128 |

| 封装: | 14 X 20 MM, PLASTIC, LQFP-128 |

| 文件页数: | 25/26页 |

| 文件大小: | 519K |

| 代理商: | HFA3842BIN-TK |

25

both USB+ and USB- inputs are low continuously for more

than 2.5 microseconds. This condition resets the USB core

and certain other hardware, but does not perform a complete

soft reset. Hardware and software reset leave the

HFA3842B in the same state except in the case of soft reset

from the PC Card Host Interface, in which case the COR and

HCR registers come into play.

The MD[15:8] pin values are sampled during HRESET or

SRESET. These pins have internal 50K pull-down resistors.

External pull-up resistors (typically 10k

) are used for bits

that should be read as high at reset.

Table 12 summarizes the effect per pin. Table 13 provides

the MD15 and MD14 bit values required by the HFA3842B to

allow usage of Serial EEPROM Devices.

References

For Intersil documents available on the internet, see web site

www.intersil.com/

[1] IEEE Std 802.11-1999 Wireless LAN Medium Access

Control (MAC) and Physical Layer (PHY) Specification.

[2]

HFA3860B Data Sheet

, Direct Sequence Spread

Spectrum Baseband Processor, Intersil Corporation,

FN4594.

[3]

HFA3861 Data Sheet

, Direct Sequence Spread

Spectrum Baseband Processor, Intersil Corporation,

FN4699.

[4]

HFA3783 Data Sheet

, Quad IF, Intersil Corporation,

FN4633.

[5]

HFA3683 Data Sheet

, Direct Sequence Spread

Spectrum Baseband Processor, Intersil Corporation,

FN4634.

[6] PC Card Standard 1996, PCMCIA/JEIDA.

[7]

AN9844 Application Note,

Intersil Corporation,

“HFA3841 to PRISM II Connections”, AN9844.

[8]

AN9926 Application Note,

Intersil Corporation,

“HFA3842 and HFA3841 Differences”, AN9926.

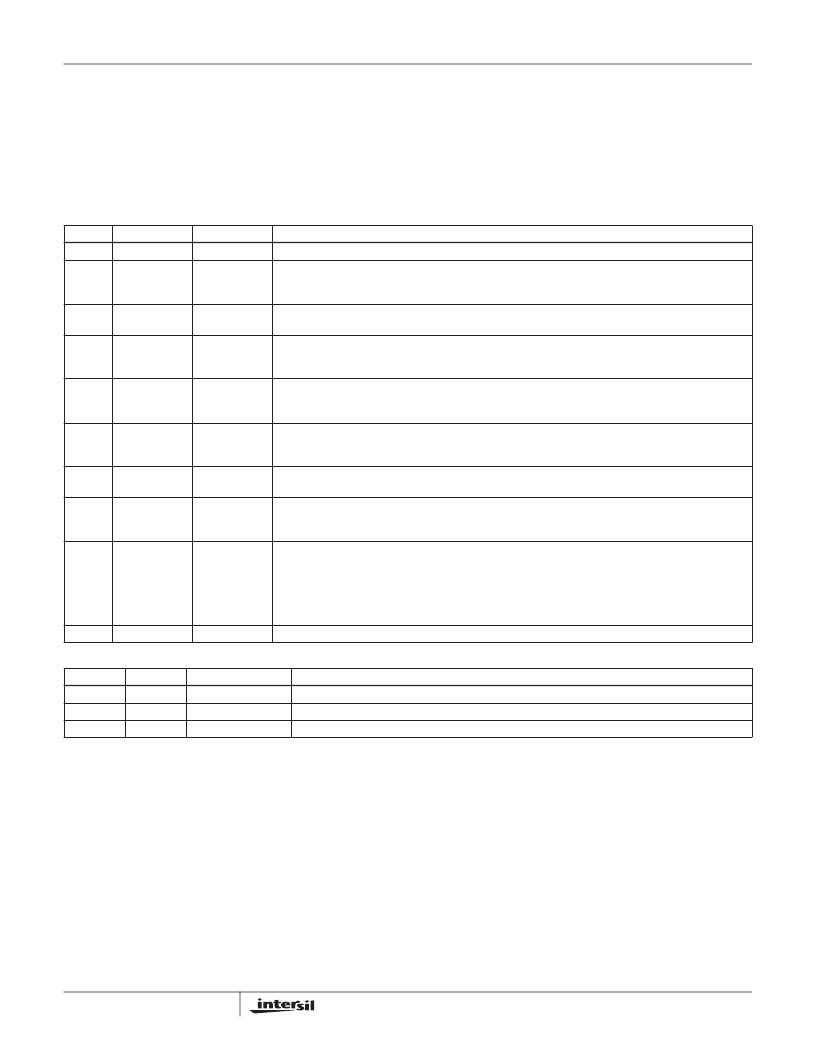

TABLE 12. INITIALIZATION STRAPPING OPTIONS ON MBUS DATA PINS

BITS

15:14

13

NAME

NVtype[1:01]

SHI_ENABLE

DEFAULT

0

0

FUNCTION

Indicates type of serial NV memory to be read by initialization firmware in on-chip ROM.

Use a Serial Host Interface (PC Card or ISA). When = 1 use a Serial Host Interlace (USB), and disable

all PC Card functions except Attribute space, for access to the COR and HCR Registers (see Section

4.3) for firmware debugging support.

Use 4-wire interface to SRAM (CS-, OE-, WEH-, WEL-) as appropriate when using x8 SRAMs. When

0 = selects 5-wire interface for use with x16 SRAM (CS-, OE-, WE-, UBE-, LBE-).

Start Idle. If ROMds = 0, then the “hardware” ignores this bit, but it is examined by the lCSROM boot

code which will halt after loading the serial NV. If ROMds = 1, then setting this bit will cause the

processor to wait for download of data From the AuxPort.

RAM and NV space at startup is 516. When = 0 RAM and NV space at startup is x8. IF starting from

off-chip NV memory this setting must indicate the width of the startup Flash EPROM. During

initialization, firmware can set separate widthsfor RAM and NV space in the Memory Control Register.

Disable mapping of off-chip control store to NV, space hence map off-chip control store to RAM

space). When = 0 off-chip control store is mapped to NV memory. This bit is used only to set initial

values in the MOR and CSCR registers. It controls the setting of the NVRE and MAPxx bits therein.

Disable on-chip ICSROM (Internal Control Store ROM - bootstrap code). When = 0 enable on-chip

ICS-ROM.

Set host interface control signals and address decoding For PC Card. When = 1 set host interface

signals and address decoding is for ISA bus, with all registers in I/O space and Attribute space

disabled. To use ISA mode, PHlenable must be = I to enable a Parallel Host Interface.

Enable I/O space decoding for the physical FCRs. When = 1, the COR. CSR, and PRR registers (see

Section 4.3) are accessible at I/O space offsets 0 x 40, 0 x 42, and 0 x 44 respectively. When = 0 these

registers are only accessible in Attribute space. This bit is ignored when PHIenable = 0, and is

overridden (forced = 1) when ISA mode = 1. FCRinIO = 1 is useful For PC Card operation PHIenable

= 1 lSA mode = 0 to allow non OS software to access the COR/HCR in OS environments where the

system software does not permit application software to access Attribute space.

a

Not assigned.

I 2

4wire

1

11

Strldle

0

10

Mem16

0

9

NVds

0

8

ROMds

1

7

ISA Mode

0

6

FCRinIO

0

5:0

Spare

00

TABLE 13. SERIAL EEPROM SELECTION

MD15

0

0

1

MD14

0

1

X

DEVICE TYPE

AT45DB011

24C08 (Note)

None

FUNCTION

Large Serial Device used to transfer firmware to SRAM

Small Serial Device which contains only CIS. MAC goes idle after loading CIS and waits for host.

Modes not supported in firmware at this time. Consult factory for additional device types added.

NOTE: The operating frequency of the serial port is 400kHz with a voltage of 3.3V.

HFA3842B

相关PDF资料 |

PDF描述 |

|---|---|

| HFA3842IN96 | Wireless LAN Medium Access Controller |

| HFA3842 | Wireless LAN Medium Access Controller |

| HFA3842IN | Wireless LAN Medium Access Controller |

| HFA3860AIV96 | Circular Connector; No. of Contacts:5; Series:MS27473; Body Material:Aluminum; Connecting Termination:Crimp; Connector Shell Size:10; Circular Contact Gender:Pin; Circular Shell Style:Straight Plug; Insert Arrangement:10-5 RoHS Compliant: No |

| HFA3860A | Direct Sequence Spread Spectrum Baseband |

相关代理商/技术参数 |

参数描述 |

|---|---|

| HFA3842IN | 制造商:Rochester Electronics LLC 功能描述:- Bulk |

| HFA3842IN96 | 制造商:INTERSIL 制造商全称:Intersil Corporation 功能描述:Wireless LAN Medium Access Controller |

| HFA3860 | 制造商:INTERSIL 制造商全称:Intersil Corporation 功能描述:11 Mbps Direct Sequence Spread Spectrum Baseband Processor |

| HFA3860A | 制造商:INTERSIL 制造商全称:Intersil Corporation 功能描述:Direct Sequence Spread Spectrum Baseband |

| HFA3860AEVAL1 | 制造商:Rochester Electronics LLC 功能描述:- Bulk 制造商:Harris Corporation 功能描述: |

发布紧急采购,3分钟左右您将得到回复。