- 您现在的位置:买卖IC网 > PDF目录371807 > HFA3842IN96 (INTERSIL CORP) Wireless LAN Medium Access Controller PDF资料下载

参数资料

| 型号: | HFA3842IN96 |

| 厂商: | INTERSIL CORP |

| 元件分类: | 微控制器/微处理器 |

| 英文描述: | Wireless LAN Medium Access Controller |

| 中文描述: | 1 CHANNEL(S), 11M bps, LOCAL AREA NETWORK CONTROLLER, PQFP128 |

| 封装: | 14 X 20 MM, PLASTIC, MS-026BHB, LQFP-128 |

| 文件页数: | 20/26页 |

| 文件大小: | 512K |

| 代理商: | HFA3842IN96 |

20

In transmit mode, the HFA386X is used in the mode where it

generates the PLCP header internally and only the MPDU is

passed from HFA3842. In receive, the HFA386X is used in

the mode where it passes the PLCP header and the MPDU

to the HFA3842.

BBP Packet Reception

There are 4 signals associated with the BBP Receive Port:

RX_PE (Receive Enable), MDRDY (Receive Ready), RXD

(Receive Data), and RXCLK (Receive Clock). These

connect to the HFA3842 on pins PL1, PK5, RXD, and RXC,

respectively.

The receive demodulator in the BBP is activated via RX_PE.

When RX_PE goes active the demodulator scrutinizes I and

Q for packet activity. When a packet arrives at a valid signal

level the demodulator acquires and tracks the incoming

signal. It then sifts through the demodulator data for the Start

Frame Delimiter (SFD). Normally, MDRDY is programmed to

go active after SFD is detected. This signals the HFA3842,

allowing it to pick off the needed header fields from the real-

time demodulated bitstream rather than having to read these

fields through the BBP Control Port.

Assuming all is well with the header, the BBP decodes the

signal field in the header and switches to the appropriate

data rate. If the signal field is not recognized, or the CRC16

is in error, then MDRDY will go inactive shortly after CRC16

and the demodulator will return to acquisition mode looking

for another packet. If all is well with the header, and after the

demodulator has switched to the appropriate data rate, then

the demodulator will continue to provide data to the

HFA3842 indefinitely.

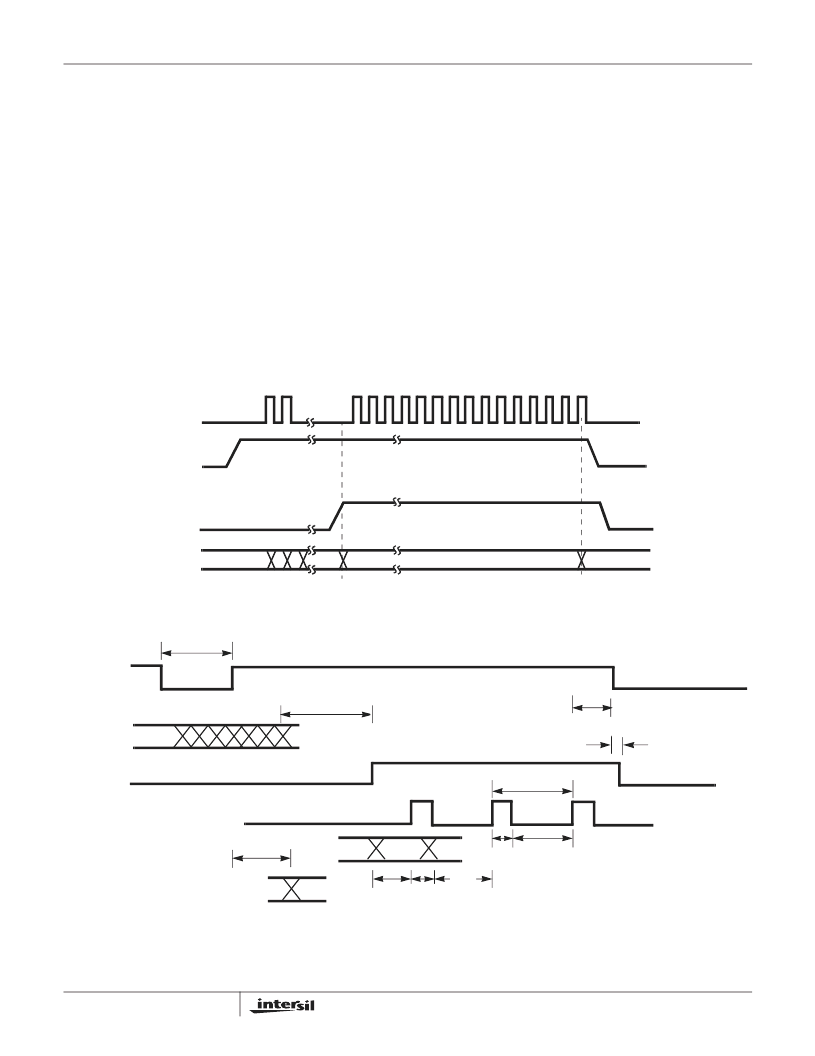

Receive Port exchange details are depicted in Figure 21.

Detailed timing is related in Figure 22 and Table 8.

For more detailed information concerning BBP packet

reception see the HFA386x data sheets.

FIGURE 21. BBP RECEIVE PORT TIMING

LSB

MSB

DATA PACKET

RXC

RX_PE

MDRDY

RXD

HEADER

FIELDS

PROCESSING

PREAMBLE/HEADER

DATA

RX_PE

I

IN

, Q

IN

t

RLP

MDRDY

RXC

RXD

CCA, RSSI

t

CCA

t

RD3

t

RDI

t

RCD

t

RCP

t

REH

t

RD2

FIGURE 22. BBP RECEIVE PORT SIGNAL TIMING

NOTE: RXD, MDRDY is output two MCLK after RXC rising to provide hold time. RSSI output on TEST (5:0).

t

RCD

t

RDD

t

RDS

HFA3842

相关PDF资料 |

PDF描述 |

|---|---|

| HFA3842 | Wireless LAN Medium Access Controller |

| HFA3842IN | Wireless LAN Medium Access Controller |

| HFA3860AIV96 | Circular Connector; No. of Contacts:5; Series:MS27473; Body Material:Aluminum; Connecting Termination:Crimp; Connector Shell Size:10; Circular Contact Gender:Pin; Circular Shell Style:Straight Plug; Insert Arrangement:10-5 RoHS Compliant: No |

| HFA3860A | Direct Sequence Spread Spectrum Baseband |

| HFA3860AIV | 3.3V 288-mc CPLD |

相关代理商/技术参数 |

参数描述 |

|---|---|

| HFA3860 | 制造商:INTERSIL 制造商全称:Intersil Corporation 功能描述:11 Mbps Direct Sequence Spread Spectrum Baseband Processor |

| HFA3860A | 制造商:INTERSIL 制造商全称:Intersil Corporation 功能描述:Direct Sequence Spread Spectrum Baseband |

| HFA3860AEVAL1 | 制造商:Rochester Electronics LLC 功能描述:- Bulk 制造商:Harris Corporation 功能描述: |

| HFA3860AIV | 制造商:INTERSIL 制造商全称:Intersil Corporation 功能描述:Direct Sequence Spread Spectrum Baseband |

| HFA3860AIV WAF | 制造商:Harris Corporation 功能描述: |

发布紧急采购,3分钟左右您将得到回复。