- 您现在的位置:买卖IC网 > PDF目录371821 > HIP4081IB (HARRIS SEMICONDUCTOR) System Basic Chips (SBC); Package: PG-DSO-28; Transceiver: Fault-tollerant CAN ISO 11898 - 3; Voltage Regulator Output: 120 mA; Watchdog: Window Watchdog; Quiescent Current<sub> (max.): < 85 µA (5V on); Standby current: < 500 µA (5V on) PDF资料下载

参数资料

| 型号: | HIP4081IB |

| 厂商: | HARRIS SEMICONDUCTOR |

| 元件分类: | MOSFETs |

| 英文描述: | System Basic Chips (SBC); Package: PG-DSO-28; Transceiver: Fault-tollerant CAN ISO 11898 - 3; Voltage Regulator Output: 120 mA; Watchdog: Window Watchdog; Quiescent Current<sub> (max.): < 85 µA (5V on); Standby current: < 500 µA (5V on) |

| 中文描述: | 2.6 A FULL BRDG BASED MOSFET DRIVER, PDSO20 |

| 文件页数: | 6/18页 |

| 文件大小: | 216K |

| 代理商: | HIP4081IB |

6

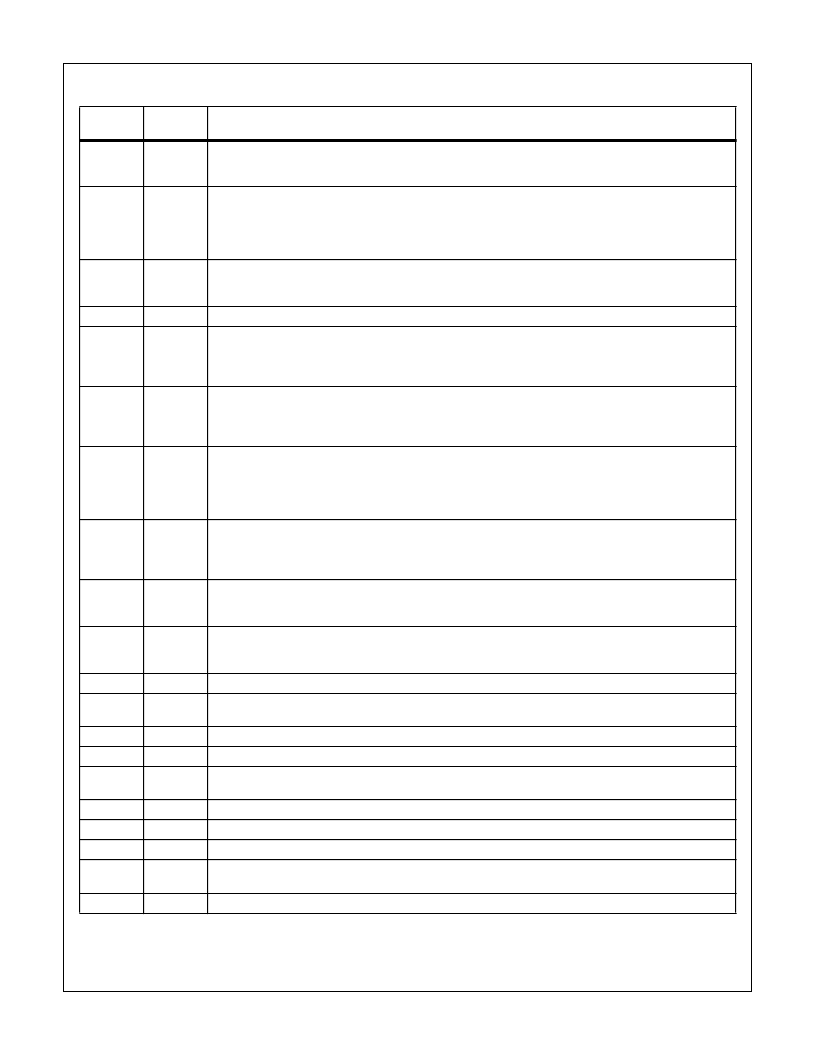

Pin Descriptions

PIN

NUMBER

SYMBOL

DESCRIPTION

1

BHB

B High-side Bootstrap supply. External bootstrap diode and capacitor are required. Connect cathode of boot-

strap diode and positive side of bootstrap capacitor to this pin. Internal charge pump supplies 30

μ

A out of this

pin to maintain bootstrap supply. Internal circuitry clamps the bootstrap supply to approximately 12.8V.

2

BHI

B High-side Input. Logic level input that controls BHO driver (Pin 20). BLI (Pin 5) high level input overrides BHI

high level input to prevent half-bridge shoot-through, see Truth Table. DIS (Pin 3) high level input overrides BHI

high level input. The pin can be driven by signal levels of 0V to 15V (no greater than V

DD

). An internal 100

μ

A

pull-up to V

DD

will hold BHI high, so no connection is required if high-side and low-side outputs are to be con-

trolled by the low-side input.

3

DIS

Disable input. Logic level input that when taken high sets all four outputs low. DIS high overrides all other inputs.

When DIS is taken low the outputs are controlled by the other inputs. The pin can be driven by signal levels of

0V to 15V (no greater than V

DD

). An internal 100

μ

A pull-up to V

DD

will hold DIS high if this pin is not driven.

Chip negative supply, generally will be ground.

4

V

SS

BLI

5

B Low-side Input. Logic level input that controls BLO driver (Pin 18). If BHI (Pin 2) is driven high or not connected

externally then BLI controls both BLO and BHO drivers, with dead time set by delay currents at HDEL and LDEL

(Pin 8 and 9). DIS (Pin 3) high level input overrides BLI high level input. The pin can be driven by signal levels

of 0V to 15V (no greater than V

DD

). An internal 100

μ

A pull-up to V

DD

will hold BLI high if this pin is not driven.

A Low-side Input. Logic level input that controls ALO driver (Pin 13). If AHI (Pin 7) is driven high or not connected

externally then ALI controls both ALO and AHO drivers, with dead time set by delay currents at HDEL and LDEL

(Pin 8 and 9). DIS (Pin 3) high level input overrides ALI high level input. The pin can be driven by signal levels

of 0V to 15V (no greater than V

DD

). An internal 100

μ

A pull-up to V

DD

will hold ALI high if this pin is not driven.

A High-side Input. Logic level input that controls AHO driver (Pin 11). ALI (Pin 6) high level input overrides AHI

high level input to prevent half-bridge shoot-through, see Truth Table. DIS (Pin 3) high level input overrides AHI

high level input. The pin can be driven by signal levels of 0V to 15V (no greater than V

DD

). An internal 100

μ

A

pull-up to V

DD

will hold AHI high, so no connection is required if high-side and low-side outputs are to be con-

trolled by the low-side input.

6

ALI

7

AHI

8

HDEL

High-side turn-on DELay. Connect resistor from this pin to V

SS

to set timing current that defines the turn-on de-

lay of both high-side drivers. The low-side drivers turn-off with no adjustable delay, so the HDEL resistor guar-

antees no shoot-through by delaying the turn-on of the high-side drivers. HDEL reference voltage is

approximately 5.1V.

9

LDEL

Low-side turn-on DELay. Connect resistor from this pin to V

SS

to set timing current that defines the turn-on delay

of both low-side drivers. The high-side drivers turn-off with no adjustable delay, so the LDEL resistor guarantees

no shoot-through by delaying the turn-on of the low-side drivers. LDEL reference voltage is approximately 5.1V.

10

AHB

A High-side Bootstrap supply. External bootstrap diode and capacitor are required. Connect cathode of boot-

strap diode and positive side of bootstrap capacitor to this pin. Internal charge pump supplies 30

μ

A out of this

pin to maintain bootstrap supply. Internal circuitry clamps the bootstrap supply to approximately 12.8V.

11

AHO

A High-side Output. Connect to gate of A High-side power MOSFET.

12

AHS

A High-side Source connection. Connect to source of A High-side power MOSFET. Connect negative side of

bootstrap capacitor to this pin.

13

ALO

A Low-side Output. Connect to gate of A Low-side power MOSFET.

14

ALS

A Low-side Source connection. Connect to source of A Low-side power MOSFET.

15

V

CC

Positive supply to gate drivers. Must be same potential as V

DD

(Pin 16). Connect to anodes of two bootstrap

diodes

.

16

V

DD

BLS

Positive supply to lower gate drivers. Must be same potential as V

CC

(Pin 15). De-couple this pin to V

SS

(Pin 4).

B Low-side Source connection. Connect to source of B Low-side power MOSFET.

17

18

BLO

B Low-side Output. Connect to gate of B Low-side power MOSFET.

19

BHS

B High-side Source connection. Connect to source of B High-side power MOSFET. Connect negative side of

bootstrap capacitor to this pin.

20

BHO

B High-side Output. Connect to gate of B High-side power MOSFET.

HIP4081

相关PDF资料 |

PDF描述 |

|---|---|

| HIP4081 | 80V/2.5A Peak, High Frequency Full Bridge FET Driver |

| HIP4081IP | 80V/2.5A Peak, High Frequency Full Bridge FET Driver |

| HIP4082IB | 80V, 1.25A Peak Current H-Bridge FET Driver |

| HIP4082 | 80V, 1.25A Peak Current H-Bridge FET Driver |

| HIP4082IP | 30000 SYSTEM GATE 3.3 VOLT LOGIC CELL AR - NOT RECOMMENDED for NEW DESIGN |

相关代理商/技术参数 |

参数描述 |

|---|---|

| HIP4081IB/IP WAF | 制造商:Harris Corporation 功能描述: |

| HIP4081IP | 制造商:Rochester Electronics LLC 功能描述:- Bulk |

| HIP4081IPR3162 | 制造商:Rochester Electronics LLC 功能描述:- Bulk |

| HIP4082 | 制造商:INTERSIL 制造商全称:Intersil Corporation 功能描述:80V, 1.25A Peak Current H-Bridge FET Driver |

| HIP4082_06 | 制造商:INTERSIL 制造商全称:Intersil Corporation 功能描述:80V, 1.25A Peak Current H-Bridge FET Driver |

发布紧急采购,3分钟左右您将得到回复。