- 您现在的位置:买卖IC网 > PDF目录385381 > HIP5015EVAL2 (Intersil Corporation) () PDF资料下载

参数资料

| 型号: | HIP5015EVAL2 |

| 厂商: | Intersil Corporation |

| 英文描述: | () |

| 中文描述: | () |

| 文件页数: | 2/6页 |

| 文件大小: | 97K |

| 代理商: | HIP5015EVAL2 |

4-109

Current-Sharing

The voltage-programmed DC-DC converters in the Flexible

DC-DC Converter rely upon matched converters and

‘identical’ PWM drive signals for ‘inherent’ load current-

sharing. Complex current-sharing control loops and lossy

current-sense resistors are

not required

with this approach.

The two main sources of current-sharing error with this

method are: (1) impedance mismatches in the converter

power delivery circuits, and (2) pulse-width mismatches of

the Phase Voltages presented to the two converters’ L-C

filters. With careful design and board layout, the current-

sharing error between the two converters is minimized.

Impedance and Pulse-Width Mismatches

The two DC-DC converters are identical other than the

polarity of the SynchroFET devices used and one resistor

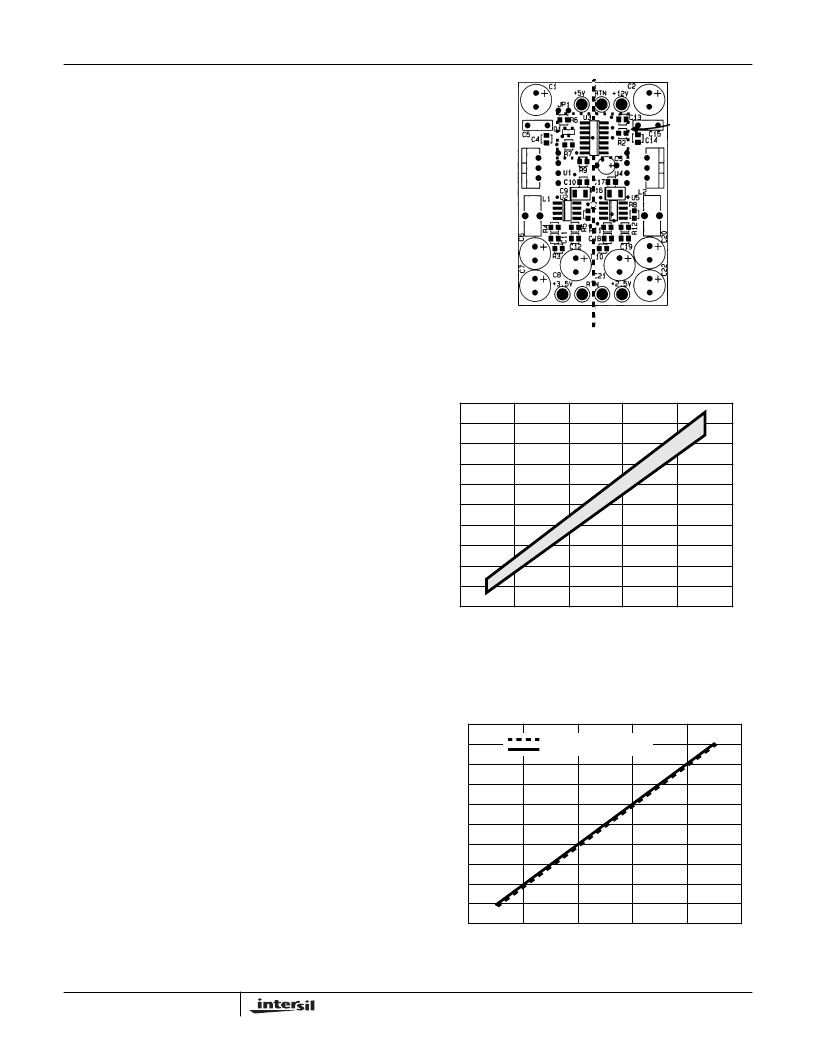

to set the output voltage. Figure 3 shows the layout for the

HIP5015EVAL2 board. The two converters are physically

laid out as nearly mirror images of each other, which helps

minimize wiring impedance differences. With this well-

matched board layout, the main source of impedance

mismatch is the power MOSFET on-resistance (r

DS(ON)

)

variations. The estimated impedance mismatch for the

HIP5015EVAL2 board is 20m

worst-case.

Phase Voltage pulse-width mismatch can arise from two

sources: (1) DR1 and DR2 signal mismatches due to gating

logic propagation delay and threshold mismatches, and (2)

SynchroFET device propagation delay mismatches. The

sum of these errors will typically be no more than 15ns. This

amount of timing mismatch is less than 0.4% of the Phase

Voltage pulse width at the 400kHz switching frequency.

Figure 4 shows a lab-measured envelope for current-sharing

of the two converters. The outer limits of the envelope

represent actual lab data with 20m

impedance mismatch

and 15ns pulse-width mismatch introduced between the two

converters. Figure 5 shows more typical current-sharing

data for the HIP5015EVAL2 board. It displays lab data for a

board without impedance and pulse-width mismatches

introduced and compares it to ‘perfect’ current-sharing. The

percent error from ideal current-sharing is less than 1%.

GATING

LOGIC

CONVERTER

#

2

CONVERTER

#

1

FIGURE 3. FLEXIBLEDC-DCCONVERTERBOARDLAYOUT.

The board dimensions are 1.5 x 2.2 inches (Figure is

actual size).

FIGURE 4. EXPECTED ENVELOPE FOR CURRENT

SHARING.

The outer limits of the envelope are based

on lab data with 15ns Phase Voltage pulse-width

mismatch and 20m

impedance mismatch between

the two converters.

5

4

3

2

1

2

4

6

8

10

TOTAL LOAD CURRENT (A)

3

0

0

FIGURE 5. ACTUAL vs IDEAL CURRENT SHARING

LAB DATA

“PERFECT” SHARING

5

4

3

2

1

0

0

2

4

6

8

10

TOTAL LOAD CURRENT (A)

3

Application Note 9625

SynchroFET is a trademark of Intersil Corporation.

相关PDF资料 |

PDF描述 |

|---|---|

| HIP5060DW | Power Control IC Single Chip PowerSupply |

| HIP5060DY | FPGA 1000000 SYSTEM GATE 1.8 VOLT - NOT RECOMMENDED for NEW DESIGN |

| HIP6003 | Buck Pulse-Width Modulator (PWM) Controller and Output Voltage Monitor |

| HIP6003CB | Buck Pulse-Width Modulator (PWM) Controller and Output Voltage Monitor |

| HIP6004BCB | Buck and Synchronous-Rectifier (PWM) Controller and Output Voltage Monitor |

相关代理商/技术参数 |

参数描述 |

|---|---|

| HIP5015IS | 制造商:Rochester Electronics LLC 功能描述:- Bulk |

| HIP5015IS WAF | 制造商:Harris Corporation 功能描述: |

| HIP5015IS1 | 制造商:Rochester Electronics LLC 功能描述:- Bulk |

| HIP5016 | 制造商:INTERSIL 制造商全称:Intersil Corporation 功能描述:7V, 7A SynchroFET⑩ Complementary Drive Synchronous Half-Bridge |

| HIP5016IS | 制造商:Rochester Electronics LLC 功能描述:- Bulk |

发布紧急采购,3分钟左右您将得到回复。