- 您现在的位置:买卖IC网 > PDF目录371821 > HIP6018CB (HARRIS SEMICONDUCTOR) Advanced PWM and Dual Linear Power Control PDF资料下载

参数资料

| 型号: | HIP6018CB |

| 厂商: | HARRIS SEMICONDUCTOR |

| 元件分类: | 稳压器 |

| 英文描述: | Advanced PWM and Dual Linear Power Control |

| 中文描述: | SWITCHING CONTROLLER, 1000 kHz SWITCHING FREQ-MAX, PDSO24 |

| 封装: | SOIC-24 |

| 文件页数: | 12/14页 |

| 文件大小: | 133K |

| 代理商: | HIP6018CB |

2-235

microprocessor core requires high quality capacitors to

supply the high slew rate (di/dt) current demands.

PWM Output Capacitors

Modern microprocessors produce transient load rates above

10A/ns. High frequency capacitors initially supply the transient

and slow the current load rate seen by the bulk capacitors.

The bulk filter capacitor values are generally determined by

the ESR (effective series resistance) and ESL (effective series

inductance) parameters rather than actual capacitance.

High frequency decoupling capacitors should be placed as

close to the power pins of the load as physically possible. Be

careful not to add inductance in the circuit board wiring that

could cancel the usefulness of these low inductance

components. Consult with the manufacturer of the load on

specific decoupling requirements.

Use only specialized low-ESR capacitors intended for

switching regulator applications for the bulk capacitors. The

bulk capacitor’s ESR determines the output ripple voltage and

the initial voltage drop after a high slew-rate transient. An

aluminum electrolytic capacitor’s ESR value is related to the

case size with lower ESR available in larger case sizes.

However, the equivalent series inductance of these capacitors

increases with case size and can reduce the usefulness of the

capacitor to high slew-rate transient loading. Unfortunately,

ESL is not a specified parameter. Work with your capacitor

supplier and measure the capacitor’s impedance with

frequency to select suitable components. In most cases,

multiple electrolytic capacitors of small case size perform

better than a single large case capacitor. For a given transient

load magnitude, the output voltage transient response due to

the output capacitor characteristics can be approximated by

the following equation:

Linear Output Capacitors

The output capacitors for the linear regulator and the linear

controller provide dynamic load current. The linear controller

uses dominant pole compensation integrated in the error

amplifier and is insensitive to output capacitor selection.

Capacitor, C

OUT3

should be selected for transient load

regulation.

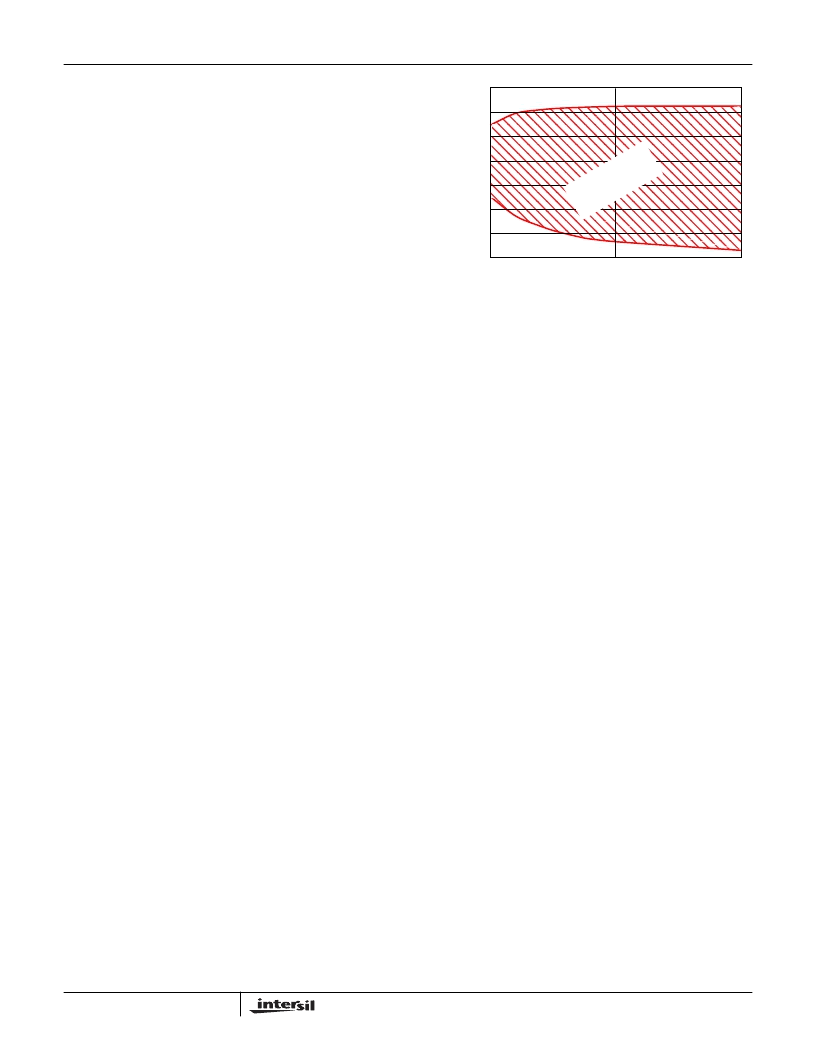

The output capacitor for the linear regulator provides loop

stability. The linear regulator (OUT2) requires an output

capacitor characteristic shown in Figure 13. The upper line

plots the 45 phase margin with 150mA load and the lower

line is the 45 phase margin limit with a 10mA load. Select a

C

OUT2

capacitor with characteristic between the two limits.

Output Inductor Selection

The PWM converter requires an output inductor. The output

inductor is selected to meet the output voltage ripple

requirements and sets the converter’s response time to a

load transient. The inductor value determines the converter’s

ripple current and the ripple voltage is a function of the ripple

current. The ripple voltage and current are approximated by

the following equations:

Increasing the value of inductance reduces the ripple current

and voltage. However, the large inductance values reduce

the converter’s response time to a load transient.

One of the parameters limiting the converter’s response to a

load transient is the time required to change the inductor

current. Given a sufficiently fast control loop design, the

HIP6018 will provide either 0% or 100% duty cycle in

response to a load transient. The response time is the time

interval required to slew the inductor current from an initial

current value to the post-transient current level. During this

interval the difference between the inductor current and the

transient current level must be supplied by the output

capacitors. Minimizing the response time can minimize the

output capacitance required.

The response time to a transient is different for the

application of load and the removal of load. The following

equations give the approximate response time interval for

application and removal of a transient load:

where: I

TRAN

is the transient load current step, t

RISE

is the

response time to the application of load, and t

FALL

is the

response time to the removal of load. With a +5V input

source, the worst case response time can be either at the

application or removal of load, and dependent upon the

output voltage setting. Be sure to check both of these

equations at the minimum and maximum output levels for the

worst case response time.

V

TRAN

ESL

dI

--------------------

×

ESR

I

TRAN

×

+

=

10

1000

100

0.1

0.2

0.3

0.4

0.5

0.6

0.7

CAPACITANCE (

μ

F)

ESR (

)

FIGURE 13. C

OUT2

OUTPUT CAPACITOR

STABLE

I

V

-------------------------------

V

O

–

S

V

IN

---------------

×

=

V

OUT

I

ESR

×

=

t

RISE

L

IN

I

OUT

×

----------–

=

t

FALL

L

------------------------------

I

OUT

×

=

HIP6018

相关PDF资料 |

PDF描述 |

|---|---|

| HIP6019BCB | Advanced Dual PWM and Dual Linear Power Control |

| HIP6019B | FPGA - 100000 SYSTEM GATE 2.5 VOLT - NOT RECOMMENDED for NEW DESIGN |

| HIP6028EVAL1 | Advanced PWM and Dual Linear Power Control with Integrated ACPI Support Interface |

| HIP6028 | Advanced PWM and Dual Linear Power Control with Integrated ACPI Support Interface |

| HIP6028CB | Advanced PWM and Dual Linear Power Control with Integrated ACPI Support Interface |

相关代理商/技术参数 |

参数描述 |

|---|---|

| HIP6018CB-T | 制造商:Rochester Electronics LLC 功能描述:- Tape and Reel |

| HIP6018EVAL1 | 制造商:INTERSIL 制造商全称:Intersil Corporation 功能描述:Advanced PWM and Dual Linear Power Control |

| HIP6019 | 制造商:IRF 制造商全称:International Rectifier 功能描述:5-BIT PROGRAMMABLE SYNCHRONOUS BUCK, NON-SYNCHRONOUS,ADJUSTABLE LDO AND 200mA ON-BOARD LDO |

| HIP6019B | 制造商:INTERSIL 制造商全称:Intersil Corporation 功能描述:Advanced Dual PWM and Dual Linear Power Control |

| HIP6019B_05 | 制造商:INTERSIL 制造商全称:Intersil Corporation 功能描述:Advanced Dual PWM and Dual Linear Power Control |

发布紧急采购,3分钟左右您将得到回复。