- 您现在的位置:买卖IC网 > PDF目录11649 > HIP9011AB (Intersil)IC SENSOR ENGINE KNOCK 20-SOIC PDF资料下载

参数资料

| 型号: | HIP9011AB |

| 厂商: | Intersil |

| 文件页数: | 7/11页 |

| 文件大小: | 0K |

| 描述: | IC SENSOR ENGINE KNOCK 20-SOIC |

| 标准包装: | 38 |

| 类型: | 引擎敲击信号处理器 |

| 输入类型: | 逻辑 |

| 输出类型: | 逻辑 |

| 接口: | SPI |

| 电流 - 电源: | 8mA |

| 安装类型: | 表面贴装 |

| 封装/外壳: | 20-SOIC(0.295",7.50mm 宽) |

| 供应商设备封装: | 20-SOIC |

| 包装: | 管件 |

5

FN4367.2

January 6, 2006

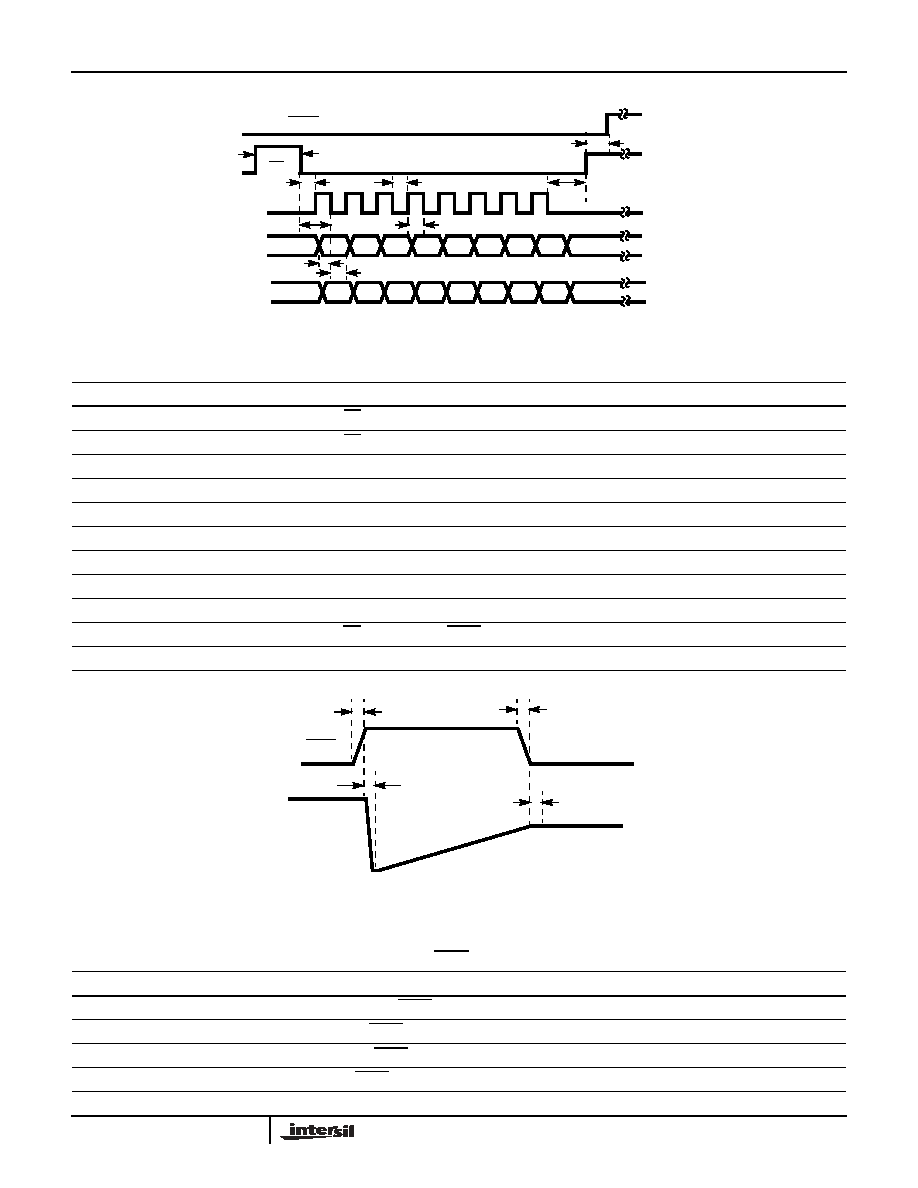

Timing Diagrams

FIGURE 1. SPI TIMING

B7

B6

B5

B4

B3

B2

B1

B0

SI

SCK

CS

tCSCH

tCSCF

tPWH

tPWL

tSCCH

tSUH

tHH

INT/HOLD

tCIH

B7

B6

B5

B4

B3

B2

B1

B0

SO

tCSH

TABLE 1. SPI TIMING REQUIREMENTS

SYMBOL

REQUIREMENT

TIME

tCSCH

Minimum time from CS falling edge to SCK rising edge.

10ns

tCSCF

Minimum time from CS falling edge to SCK falling edge.

80ns

tPWL

Minimum time for the SCK low.

60ns

tPWH

Minimum time for the SCK high.

60ns

tSCCH

Minimum time from SCK falling after 8 bits to CS raising edge.

80ns

tSUH

Minimum time from data high to falling edge of spiclk.

20ns

tSUL

Minimum time from data low to falling edge of spiclk.

20ns

tHH

Minimum time for data high after the falling edge of the spiclk.

10ns

tHL

Minimum time for data low after the falling edge of the spiclk.

10ns

tCIH

Minimum time after CS raises until INT/HOLD goes high.

8

s

tCSH

Minimum time between programming 2 internal registers.

200ns

INT/HOLD

INTOUT

t1

t2

t3

t4

FIGURE 2. INTEGRATOR TIMING

TABLE 2. INTEGRATE/HOLD TIMING REQUIREMENTS

SYMBOL

REQUIREMENT

TIME

t1

Maximum rise time of the INT/HOLD signal.

45ns

t2

Maximum time after INT/HOLD rises for INTOUT to begin to integrate.

20

s

t3

Maximum fall time of INT/HOLD signal.

45ns

t4

Typical time after INT/HOLD goes low before chip goes into hold state.

20

s

HIP9011

相关PDF资料 |

PDF描述 |

|---|---|

| X96012V14IZ | IC SENSOR CONDITION UNIV 14TSSOP |

| D38999/20WJ24PN | CONN RCPT 24POS WALL MNT W/PINS |

| MAX161CCWI+ | IC DAS 8BIT 8-CH 28-SOIC |

| MS27467E25B4S | CONN PLUG 56POS STRAIGHT W/SCKT |

| D38999/20MG11PN | CONN RCPT 11POS WALL MNT W/PINS |

相关代理商/技术参数 |

参数描述 |

|---|---|

| HIP9011ABR4682 | 制造商:Rochester Electronics LLC 功能描述:- Bulk |

| HIP9011ABR4745 | 制造商:Rochester Electronics LLC 功能描述:- Bulk |

| HIP9011ABR4745A | 制造商:Rochester Electronics LLC 功能描述:- Bulk |

| HIP9011ABR4818 | 制造商:Intersil Corporation 功能描述: |

| HIP9011ABS2667 | 制造商:Intersil Corporation 功能描述: |

发布紧急采购,3分钟左右您将得到回复。