- 您现在的位置:买卖IC网 > PDF目录370643 > HMN12816D-85 (Electronic Theatre Controls, Inc.) Non-Volatile SRAM MODULE 2Mbit (128K x 16-Bit), 40pin-Dip, 5V PDF资料下载

参数资料

| 型号: | HMN12816D-85 |

| 厂商: | Electronic Theatre Controls, Inc. |

| 英文描述: | Non-Volatile SRAM MODULE 2Mbit (128K x 16-Bit), 40pin-Dip, 5V |

| 中文描述: | 非易失性SRAM模块即可移植(128K的x 16位),40pin浸,5V的 |

| 文件页数: | 2/9页 |

| 文件大小: | 143K |

| 代理商: | HMN12816D-85 |

HANBit

HMN12816D

URL : www.hbe.co.kr 2 HANBit Electronics Co.,Ltd

Rev. 0.0 (April, 2002)

FUNCTIONAL DESCRIPTION

The HMN12816D devices execute a read cycle whenever /WE (Write Enable) is inactive (high) and either/both of /CEU or

/CEL (Chip Enables) are active (low) and /OE (Output Enable) is active (low). The unique address specified by the 17

address inputs (A0-A16) defines which of the 131,072 words of data is accessed. The status of /CEU and /CEL

determines whether all or part of the addressed word is accessed. If /CEU is active with /CEL inactive, then only the upper

byte of the addressed word is accessed. If /CEU is inactive with /CEL active, then only the lower byte of the addressed

word is accessed. If both the /CEU and /CEL inputs are active (low), then the entire 16-bit word is accessed. Valid data will

be available to the 16 data output drivers within t

ACC

(Access Time) after the last address input signal is stable, providing

that /CEU, /CEL and /OE access times are also satisfied. If /CEU, /CEL, and /OE access times are not satisfied, then data

access must be measured from the later occurring signal, and the limiting parameter is either t

CO

for /CEU, /CEL, or t

OE

for

/OE rather than address access.

The HMN12816D devices execute a write cycle whenever /WE and either/both of /CEU or /CEL are active (low) after

address inputs are stable. The unique address specified by the 17 address inputs (A0-A16) defines which of the 131,072

words of data is accessed. The status of /CEU and /CEL determines whether all or part of the addressed word is

accessed. If /CEU is active with /CEL inactive, then only the upper byte of the addressed word is accessed. If /CEU is

inactive with /CEL active, then only the lower byte of the addressed word is accessed. If both the /CEU and /CEL inputs

are active (low), then the entire 16-bit word is accessed. The write cycle is terminated by the earlier rising edge of /CEU

and/or /CEL, or WE. All address inputs must be kept valid throughout the write cycle. /WE must return to the high state for

a minimum recovery time (t

WR

) before another cycle can be initiated. The /OE control signal should be kept inactive (high)

during write cycles to avoid bus contention. However, if the output drivers are enabled (/CEU and/or /CEL, and /OE active)

then /WE will disable the outputs in t

ODW

from its falling edge.

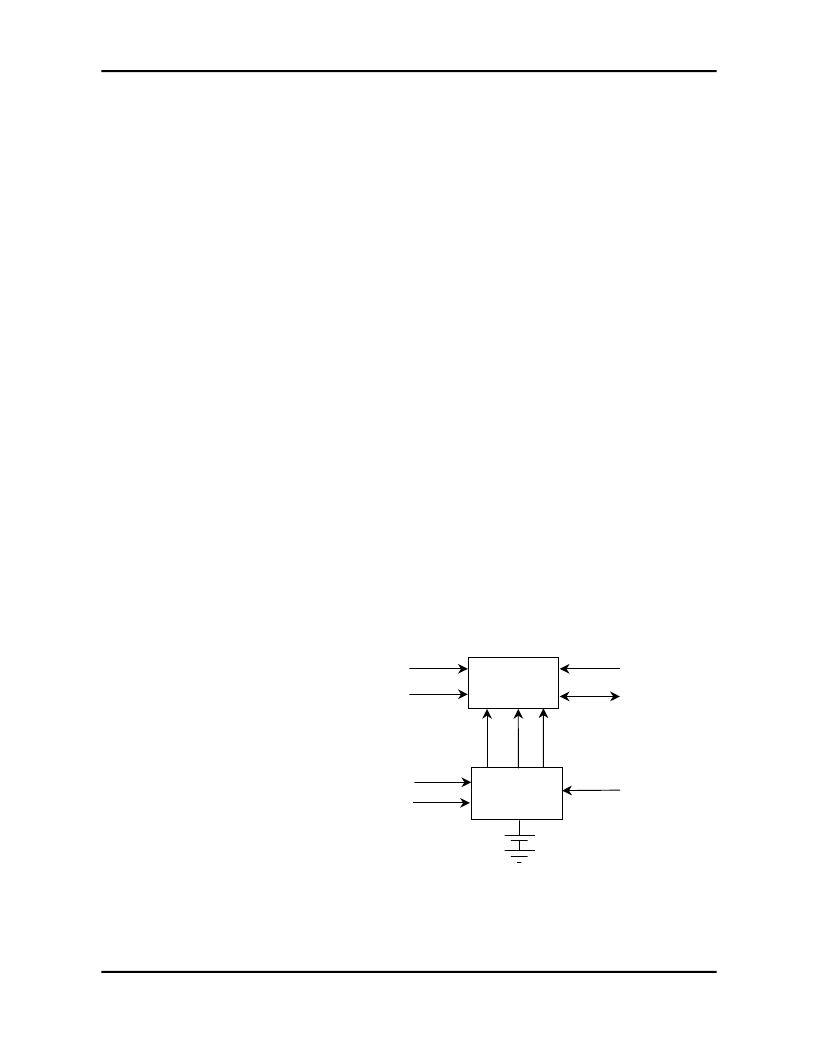

PIN DESCRIPTION BLOCK DIAGRAM

A

0

-A

16

: Address Inputs

/CEU : Chip enable upper byte

/CEL : Chip enable lower byte

DQ

0

-DQ

15

: Data input / Data output

/WE : Write enable

/OE : Output enable

V

CC

: +5V power supply

V

ss

: Ground

DQ

0

-DQ15

A

0

-A

16

/OE

/WE

/CEL

Power

V

CC

Lithium

Cell

2 x 128K x 8

SRAM

Block

/CEL

Power

–

Fail

Control

/CEU

/CEU

相关PDF资料 |

PDF描述 |

|---|---|

| HMN12816D-85I | Non-Volatile SRAM MODULE 2Mbit (128K x 16-Bit), 40pin-Dip, 5V |

| HMN1288D | Non-Volatile SRAM MODULE 1Mbit (128K x 8-Bit), 32Pin-DIP, 5V |

| HMN1288D-120 | Non-Volatile SRAM MODULE 1Mbit (128K x 8-Bit), 32Pin-DIP, 5V |

| HMN1288D-120I | Non-Volatile SRAM MODULE 1Mbit (128K x 8-Bit), 32Pin-DIP, 5V |

| HMN1288D-150 | Non-Volatile SRAM MODULE 1Mbit (128K x 8-Bit), 32Pin-DIP, 5V |

相关代理商/技术参数 |

参数描述 |

|---|---|

| HMN12816D-85I | 制造商:HANBIT 制造商全称:Hanbit Electronics Co.,Ltd 功能描述:Non-Volatile SRAM MODULE 2Mbit (128K x 16-Bit), 40pin-Dip, 5V |

| HMN1288D | 制造商:HANBIT 制造商全称:Hanbit Electronics Co.,Ltd 功能描述:Non-Volatile SRAM MODULE 1Mbit (128K x 8-Bit), 32Pin-DIP, 5V |

| HMN1288D-120 | 制造商:未知厂家 制造商全称:未知厂家 功能描述:Non-Volatile SRAM MODULE 1Mbit (128K x 8-Bit), 32Pin-DIP, 5V |

| HMN1288D-120I | 制造商:HANBIT 制造商全称:Hanbit Electronics Co.,Ltd 功能描述:Non-Volatile SRAM MODULE 1Mbit (128K x 8-Bit), 32Pin-DIP, 5V |

| HMN1288D-150 | 制造商:未知厂家 制造商全称:未知厂家 功能描述:Non-Volatile SRAM MODULE 1Mbit (128K x 8-Bit), 32Pin-DIP, 5V |

发布紧急采购,3分钟左右您将得到回复。