- 您现在的位置:买卖IC网 > PDF目录370643 > HMP8156EVAL1 (Intersil Corporation) NTSC/PAL Encoders PDF资料下载

参数资料

| 型号: | HMP8156EVAL1 |

| 厂商: | Intersil Corporation |

| 英文描述: | NTSC/PAL Encoders |

| 中文描述: | 的NTSC / PAL编码器 |

| 文件页数: | 17/40页 |

| 文件大小: | 563K |

| 代理商: | HMP8156EVAL1 |

第1页第2页第3页第4页第5页第6页第7页第8页第9页第10页第11页第12页第13页第14页第15页第16页当前第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页第29页第30页第31页第32页第33页第34页第35页第36页第37页第38页第39页第40页

17

9 - 8

Horizontal AGC

Pulse Programmable

Start Time

This register provides a programmable delay for the HAGC pulse that control the sync

tip AGC in the A/D converters. The start time of the HAGC pulse is set from the detection

of horizontal sync in the video data. HAGC is programmable in CLK increments and has

a fixed 1 clock delay following the falling edge of horizontal sync. This is the upper byte

of the 10-bit word.

11

B

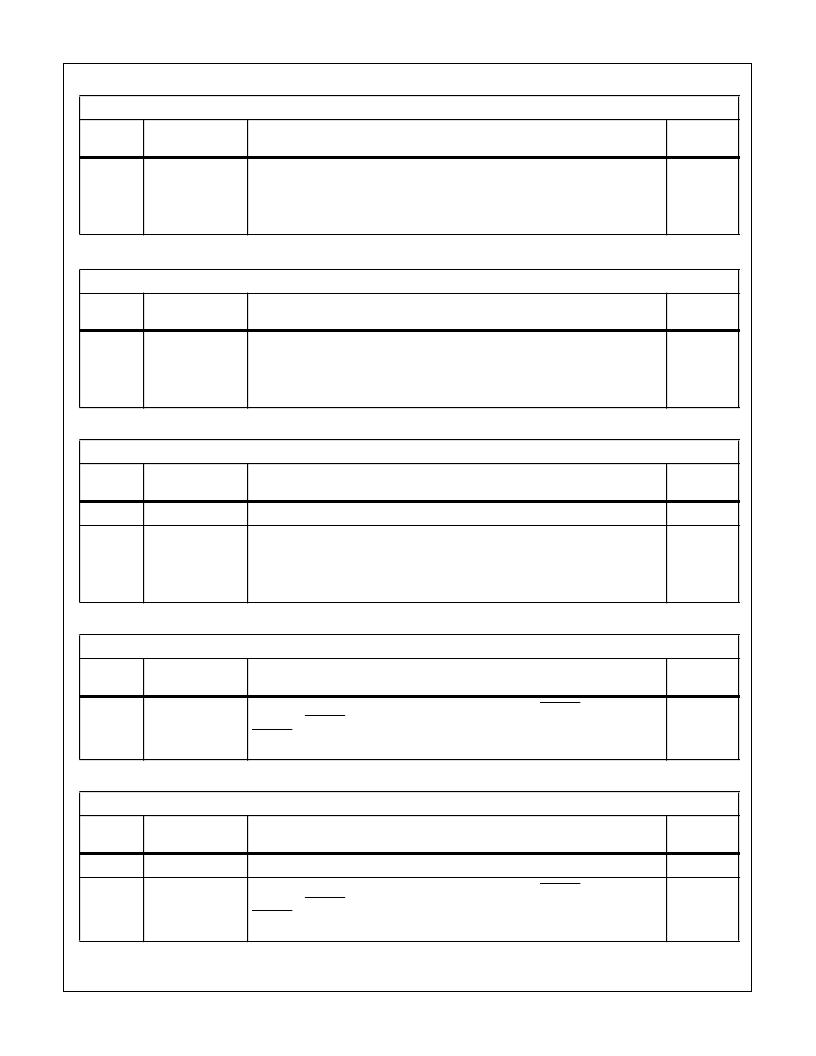

TABLE 16. HORIZONTAL AGC END TIME REGISTER

DESTINATION ADDRESS = 0A

H

BIT

NUMBER

FUNCTION

DESCRIPTION

RESET

STATE

7 - 0

Horizontal AGC

Pulse Programmable

End Time

This register provides a programmable delay for the HAGC pulse that control the sync

tip AGC in the A/D converters. The end time of the HAGC pulse is set from the detection

of horizontal sync in the video data. HAGC is programmable in CLK increments and has

a fixed 1 clock delay following the falling edge of horizontal sync. This is the lower byte

of the 10-bit word.

0000 0000

B

TABLE 17. HORIZONTAL AGC END TIME REGISTER

DESTINATION ADDRESS = 0B

H

BIT

NUMBER

FUNCTION

DESCRIPTION

RESET

STATE

15 - 10

Not Used

Write Ignored, Read 0’s

XXXX XX

9 - 8

Horizontal AGC

Pulse Programmable

End Time

This register provides a programmable delay for the HAGC pulse that control the sync

tip AGC in the A/D converters. The end time of the HAGC pulse is set from the detection

of horizontal sync in the video data. HAGC is programmable in CLK increments and has

a fixed 1 clock delay following the falling edge of horizontal sync. This is the upper byte

of the 10-bit word.

00

B

TABLE 18. HORIZONTAL SYNC START TIME REGISTER

DESTINATION ADDRESS = 0C

H

BIT

NUMBER

FUNCTION

DESCRIPTION

RESET

STATE

7 - 0

Horizontal Drive

Programmable Start

Time

This register provides a programmable delay for the external HDRIVE signal. The start

time of the HDRIVE pulse is set from the detection of horizontal sync in the video data.

HDRIVE is programmable in CLK increments and has a fixed 1 clock delay following the

falling edge of horizontal sync. This is the lower byte of the 10-bit word.

0011 1011

B

TABLE 19. HORIZONTAL SYNC START TIME REGISTER

DESTINATION ADDRESS = 0D

H

BIT

NUMBER

FUNCTION

DESCRIPTION

RESET

STATE

15 - 10

Not Used

Write Ignored, Read 0’s

XXXX XX

9 - 8

Horizontal Drive

Programmable Start

Time

This register provides a programmable delay for the external HDRIVE signal. The start

time of the HDRIVE pulse is set from the detection of horizontal sync in the video data.

HDRIVE is programmable in CLK increments and has a fixed 1 clock delay following the

falling edge of horizontal sync. This is the upper byte of the 10-bit word.

11

B

TABLE 15. HORIZONTAL AGC START TIME REGISTER (Continued)

DESTINATION ADDRESS = 09

H

BIT

NUMBER

FUNCTION

DESCRIPTION

RESET

STATE

HMP8112

相关PDF资料 |

PDF描述 |

|---|---|

| HMP8156EVAL2 | NTSC/PAL Encoders |

| HMP8156 | NTSC/PAL Encoder |

| HMP8156ACN | NTSC/PAL Encoders |

| HMP8156CN | NTSC/PAL Encoder |

| HMS30C7110 | Multipurpose Network Processor |

相关代理商/技术参数 |

参数描述 |

|---|---|

| HMP8156EVAL2 | 制造商:Rochester Electronics LLC 功能描述:- Bulk |

| HMP8170 | 制造商:INTERSIL 制造商全称:Intersil Corporation 功能描述:NTSC/PAL Video Encoder |

| HMP8170_03 | 制造商:INTERSIL 制造商全称:Intersil Corporation 功能描述:NTSC/PAL Video Encoder |

| HMP8170CN | 制造商:INTERSIL 制造商全称:Intersil Corporation 功能描述:NTSC/PAL Video Encoder |

| HMP8170EVAL1 | 制造商:INTERSIL 制造商全称:Intersil Corporation 功能描述:NTSC/PAL Video Encoder |

发布紧急采购,3分钟左右您将得到回复。