- 您现在的位置:买卖IC网 > PDF目录296194 > HMT351V7BFR8C-H9 (HYNIX SEMICONDUCTOR INC) DDR DRAM MODULE, DMA240 PDF资料下载

参数资料

| 型号: | HMT351V7BFR8C-H9 |

| 厂商: | HYNIX SEMICONDUCTOR INC |

| 元件分类: | DRAM |

| 英文描述: | DDR DRAM MODULE, DMA240 |

| 封装: | ROHS COMPLIANT, DIMM-240 |

| 文件页数: | 40/61页 |

| 文件大小: | 1050K |

| 代理商: | HMT351V7BFR8C-H9 |

第1页第2页第3页第4页第5页第6页第7页第8页第9页第10页第11页第12页第13页第14页第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页第29页第30页第31页第32页第33页第34页第35页第36页第37页第38页第39页当前第40页第41页第42页第43页第44页第45页第46页第47页第48页第49页第50页第51页第52页第53页第54页第55页第56页第57页第58页第59页第60页第61页

Rev. 0.1 / Feb. 2010

45

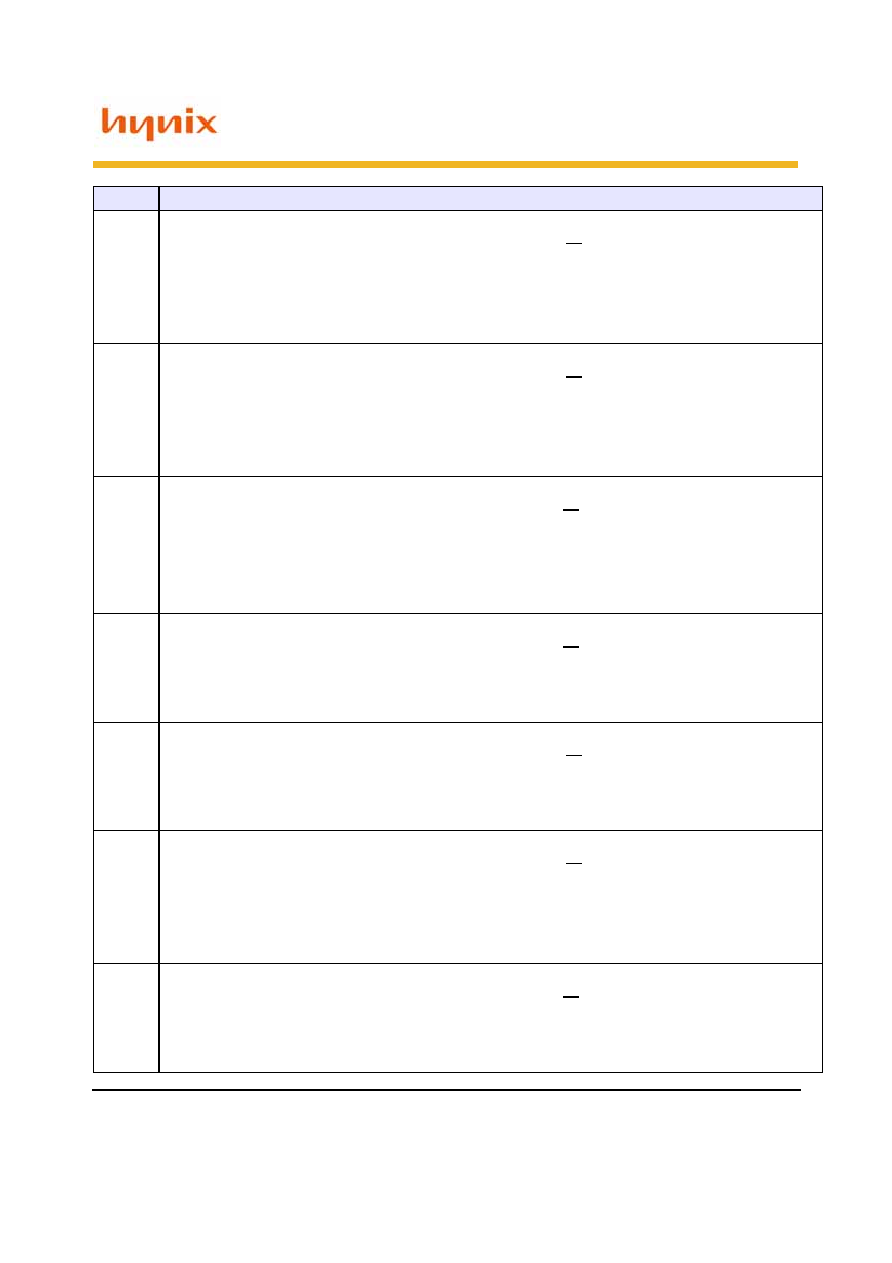

IDD2N

Precharge Standby Current

CKE: High; External clock: On; tCK, CL: see Table 1; BL: 8a); AL: 0; CS: stable at 1; Command, Address, Bank

Address Inputs: partially toggling according to Table 5; Data IO: MID_LEVEL; DM: stable at 0; Bank Activity: all

banks closed; Output Buffer and RTT: Enabled in Mode Registersb); ODT Signal: stable at 0; Pattern Details:

see Table 5.

IDD2NT

Precharge Standby ODT Current

CKE: High; External clock: On; tCK, CL: see Table 1; BL: 8a); AL: 0; CS: stable at 1; Command, Address, Bank

Address Inputs: partially toggling according to Table 6; Data IO: MID_LEVEL; DM: stable at 0; Bank Activity: all

banks closed; Output Buffer and RTT: Enabled in Mode Registersb); ODT Signal: toggling according to Table 6;

Pattern Details: see Table 6.

IDD2P0

Precharge Power-Down Current Slow Exit

CKE: Low; External clock: On; tCK, CL: see Table 1; BL: 8a); AL: 0; CS: stable at 1; Command, Address, Bank

Address Inputs: stable at 0; Data IO: MID_LEVEL; DM: stable at 0; Bank Activity: all banks closed; Output

Buffer and RTT: Enabled in Mode Registersb); ODT Signal: stable at 0; Precharge Power Down Mode: Slow

Exitc)

IDD2P1

Precharge Power-Down Current Fast Exit

CKE: Low; External clock: On; tCK, CL: see Table 1; BL: 8a); AL: 0; CS: stable at 1; Command, Address, Bank

Address Inputs: stable at 0; Data IO: MID_LEVEL; DM: stable at 0; Bank Activity: all banks closed; Output

Buffer and RTT: Enabled in Mode Registersb); ODT Signal: stable at 0; Precharge Power Down Mode: Fast Exitc)

IDD2Q

Precharge Quiet Standby Current

CKE: High; External clock: On; tCK, CL: see Table 1; BL: 8a); AL: 0; CS: stable at 1; Command, Address, Bank

Address Inputs: stable at 0; Data IO: MID_LEVEL; DM: stable at 0; Bank Activity: all banks closed; Output

Buffer and RTT: Enabled in Mode Registersb); ODT Signal: stable at 0

IDD3N

Active Standby Current

CKE: High; External clock: On; tCK, CL: see Table 1; BL: 8a); AL: 0; CS: stable at 1; Command, Address, Bank

Address Inputs: partially toggling according to Table 5; Data IO: MID_LEVEL; DM: stable at 0; Bank Activity: all

banks open; Output Buffer and RTT: Enabled in Mode Registersb); ODT Signal: stable at 0; Pattern Details: see

Table 5.

IDD3P

Active Power-Down Current

CKE: Low; External clock: On; tCK, CL: see Table 1; BL: 8a); AL: 0; CS: stable at 1; Command, Address, Bank

Address Inputs: stable at 0; Data IO: MID_LEVEL; DM: stable at 0; Bank Activity: all banks open; Output Buffer

and RTT: Enabled in Mode Registersb); ODT Signal: stable at 0

Symbol

Description

相关PDF资料 |

PDF描述 |

|---|---|

| HN4400 | NPN EXPITAXIAL SILICON TRANSISTOR |

| HN5400 | PNP Silicon Expitaxial Planar Transistor for general purpose, high voltage amplifier applications |

| HN5401 | PNP Silicon Expitaxial Planar Transistor for general purpose, high voltage amplifier applications |

| HN546 | NPN Silicon Epitaxial Planar Transistor |

| HN547 | NPN Silicon Epitaxial Planar Transistor |

相关代理商/技术参数 |

参数描述 |

|---|---|

| HMT351V7BMR4C-G7 | 制造商:HYNIX 制造商全称:Hynix Semiconductor 功能描述:240pin DDR3 SDRAM VLP Registered DIMM |

| HMT351V7BMR4C-H9 | 制造商:HYNIX 制造商全称:Hynix Semiconductor 功能描述:240pin DDR3 SDRAM VLP Registered DIMM |

| HMT351V7BMR8C-G7 | 制造商:HYNIX 制造商全称:Hynix Semiconductor 功能描述:240pin DDR3 SDRAM VLP Registered DIMM |

| HMT351V7BMR8C-H9 | 制造商:HYNIX 制造商全称:Hynix Semiconductor 功能描述:240pin DDR3 SDRAM VLP Registered DIMM |

| HMT351V7CFR4A | 制造商:HYNIX 制造商全称:Hynix Semiconductor 功能描述:DDR3L SDRAM VLP Registered DIMM Based on 2Gb C-die |

发布紧急采购,3分钟左右您将得到回复。