- 您现在的位置:买卖IC网 > PDF目录367308 > HY512260TC-50 x16 Fast Page Mode DRAM PDF资料下载

参数资料

| 型号: | HY512260TC-50 |

| 英文描述: | x16 Fast Page Mode DRAM |

| 中文描述: | x16快速页面模式的DRAM |

| 文件页数: | 8/8页 |

| 文件大小: | 100K |

| 代理商: | HY512260TC-50 |

HY512260

NOTE

1. An initial pause of 200

μ

s

is required after power-up followed by 8 /RAS only refresh cycles before proper

device operation is achieved. In case of using internal refresh counter, a minimum of 8 CBR refresh cycles instead of

8 /RAS-only refresh cycles are required.

2. If /RAS=Vss during power-up,the HY512264 could begin an active cycle. This condition results in higher current than

necessary current which is demanded from the power supply during power-up. It is recommended that /RAS and /CAS

track with Vcc during power-up or be held at a valid VIH in other to minimize the power-up current.

3. VIH(min.) and VIL(max.) are reference levels for measuring timing of input signals. Transition times are measured

between VIH(min.) and VIL(max.),and are assumed to be 2ns for all inputs.

4. Measured at V

OH

=2.0V and V

OL

=0.8V with a load equivalent to 2TTL loads and 30pF.

5. tCEZ(max.) and tOEZ define the time at which the output achieves the open circuit conditions and is not referenced to

output voltage levels.

6. Either tRCD or tRRH must be satisfied for a read cycle.

7 These parameters are referenced to /LCAS or /UCAS leading edge in early write cycles and to /WE leading edge in

read-modify-write cycles

8. t

WCS

, t

RWD

, t

CWD

, t

AWD

and t

CPWD

are not restrictive operating parameters. They are included in the data sheet as

electrical characteristics only. If t

WCS

≥

t

WCS(min.)

, the cycle is an early write cycle and data out pin will remain open

circuit (high impedance) through the entire cycle. If t

RWD

≥

t

RWD(min.)

, t

CWD

≥

t

CWD(min.)

, t

AWD

≥

t

AWD(min)

, and t

CPWD

≥

t

CPWD(min.)

, the cycle is a read-modify-write cycle and data out will contain data read from the selected cell. If neither

of the above sets of conditions is satisfied, the condition of the data out (at access time) is indeterminate.

9. Operation within the t

RCD(max.)

limit ensures that t

RAC(max.)

can be met. t

RCD(max.)

is specified as a reference point only.

If t

RCD

is greater than the specified t

RCD(max.)

limit, then access time is controlled by t

CAC

.

10.Operation within the t

RAD(max.)

limit ensures that t

RAC(max.)

can be met. t

RAD(max.)

is specified as a reference point only.

If t

RAD

is greater than the specified t

RAD(max.)

limit, then access time is controlled by t

AA

.

11.t

REF(

max.)=128ms is aren;t to L-parts and SL-parts.

12.A burst of 512 CBR refresh cycles must be executed within 8ms (128ms for SL-part) after exiting self refresh.

13.When both /LCAS and /UCAS go low at the same time, all 16-bits data are written into the device. /LCAS and /UCAS

must be transited simultaneously withen a same read or write cycle.

14.These parameters are determined by the earlier falling edge of /LCAS and /UCAS.

15.These parameters are determined by the later rising edge of /LCAS or /UCAS.

16.tCWL must be satisfied by both /LCAS and /UCAS for 16-bits access cycles.

17.tCP and tCPT are measured when both /LCAS and /UCAS are high state.

18.Operating condition for 50ns part is Vcc=5V

5%, Cout=30pF.

8

128Kx16,FP DRAM

Rev.10 / Jan.97

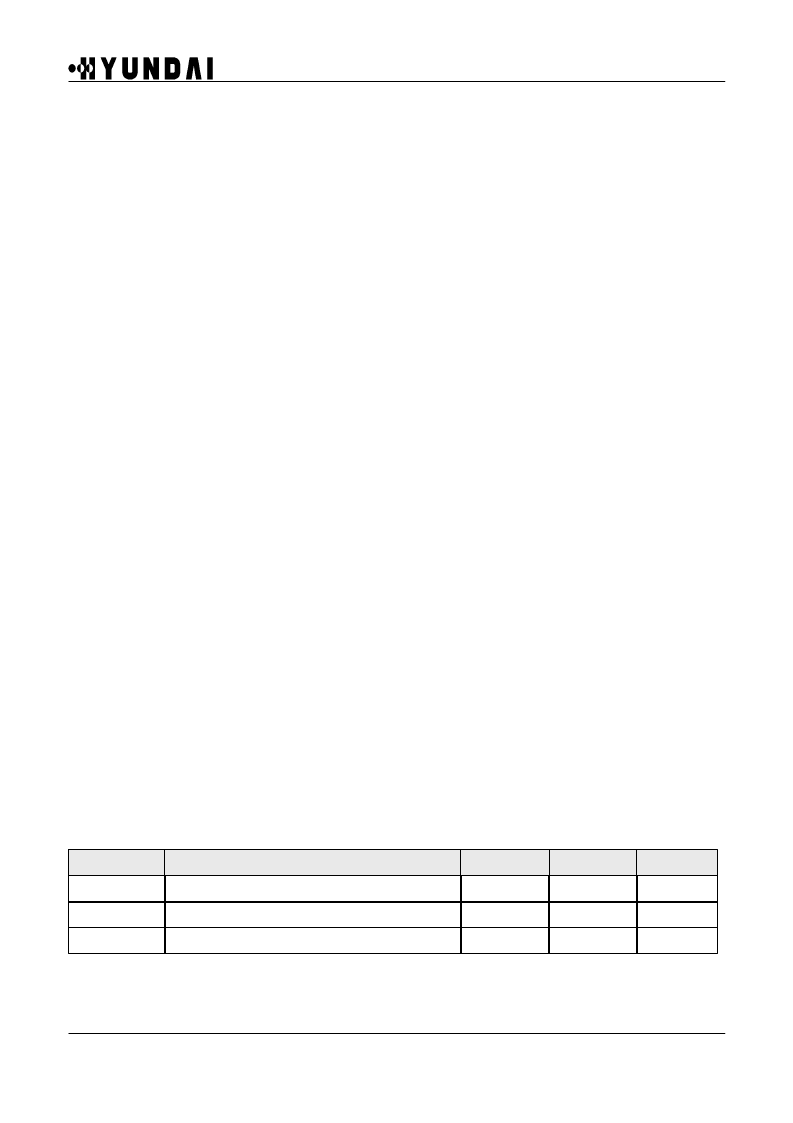

CAPACITANCE

(T

A

= 25

°

C,

V

CC

= 5V

±

10%,

V

SS

= 0V and f=1MHz, unless otherwise noted.)

Symbol

C

IN1

Parameter

Input Capacitance (A0~A8)

Max

5

Unit

pF

C

IN2

Input Capacitance (/RAS, /LCAS,/UCAS, /WE, /OE)

7

pF

C

DQ

Data Input / Output Capacitance (DQ0~DQ15)

7

pF

Typ.

-

-

-

相关PDF资料 |

PDF描述 |

|---|---|

| HY512260TC-60 | x16 Fast Page Mode DRAM |

| HY512260TC-70 | x16 Fast Page Mode DRAM |

| HY512264JC-50 | x16 EDO Page Mode DRAM |

| HY512264JC-60 | x16 EDO Page Mode DRAM |

| HY512264JC-70 | x16 EDO Page Mode DRAM |

相关代理商/技术参数 |

参数描述 |

|---|---|

| HY512260TC-60 | 制造商:未知厂家 制造商全称:未知厂家 功能描述:x16 Fast Page Mode DRAM |

| HY512260TC-70 | 制造商:未知厂家 制造商全称:未知厂家 功能描述:x16 Fast Page Mode DRAM |

| HY512264JC-50 | 制造商:未知厂家 制造商全称:未知厂家 功能描述:x16 EDO Page Mode DRAM |

| HY512264JC-60 | 制造商:未知厂家 制造商全称:未知厂家 功能描述:x16 EDO Page Mode DRAM |

| HY512264JC-70 | 制造商:未知厂家 制造商全称:未知厂家 功能描述:x16 EDO Page Mode DRAM |

发布紧急采购,3分钟左右您将得到回复。