- 您现在的位置:买卖IC网 > PDF目录367308 > HY512264LTC-50 x16 EDO Page Mode DRAM PDF资料下载

参数资料

| 型号: | HY512264LTC-50 |

| 英文描述: | x16 EDO Page Mode DRAM |

| 中文描述: | x16 EDO公司页面模式的DRAM |

| 文件页数: | 1/8页 |

| 文件大小: | 100K |

| 代理商: | HY512264LTC-50 |

HY512260

128Kx16, CMOS DRAM with /2CAS

This family is a 2M bit dynamic RAM organized 131,072 x 16-bit configuration with CMOS DRAMs. The circuit and process

design allow this device to achieve high performance and low power dissipation. Independent read and write of upper and

lower byte is controlled by 2 separate CAS inputs. Optional features are access time(50, 60 or 70ns) and power onsumption

(Normal or Low power with self refresh). Hyundai’s advanced circuit design and process technology allow this device to

achieve high bandwidth, low power consumption and high reliability.

DESCRIPTION

FEATURES

Fast page mode operation

Read-modify-write Capability

2/CAS inputs for upper and lower byte control

TTL compatible inputs and outputs

/CAS-before-/RAS, /RAS-only, Hidden and

Self refresh capability

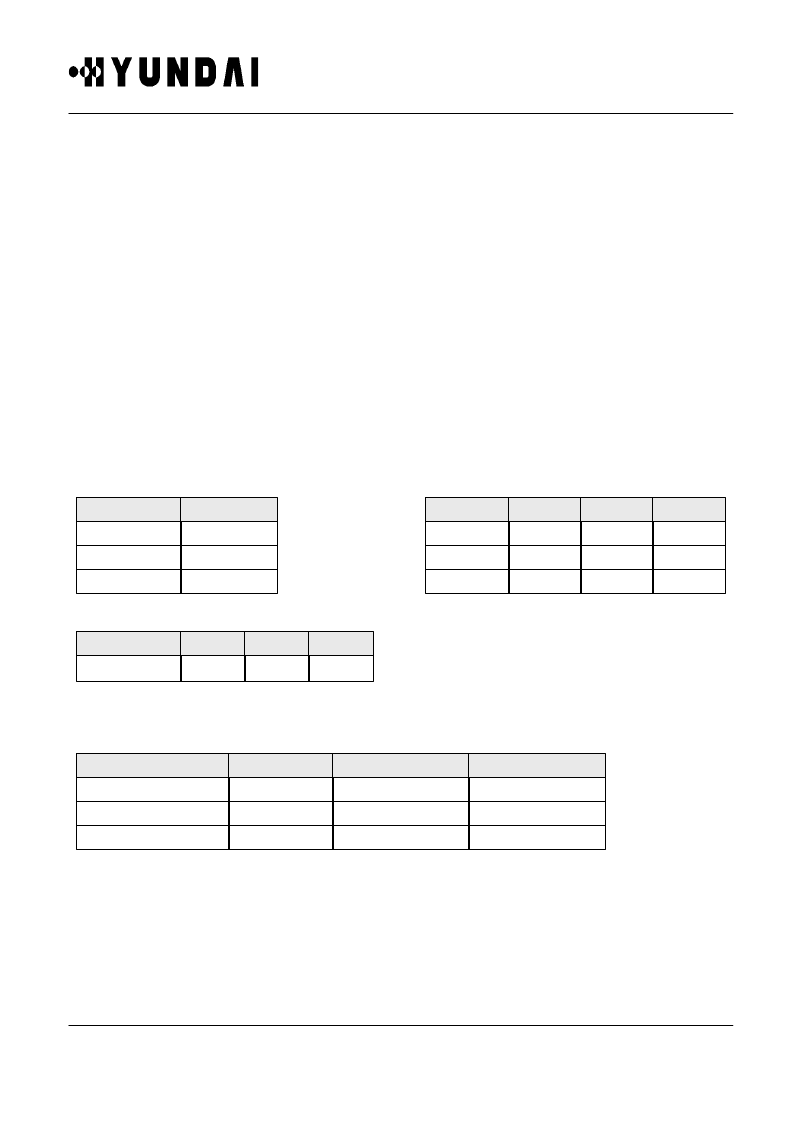

Max. Active power dissipation

Speed

50

Power

605mW

Fast access time and cycle time

Speed

50

60

tRAC

50ns

60ns

tCAC

15ns

15ns

tPC

35ns

40ns

Refresh cycle

Part number

HY512260

Refresh

512

Normal

8ms

SL-part

128ms

This document is a general product description and is subject to change without notice. Hyundai electronics does not assume any responsibility for use of

circuits described. No patent licences are implied

Rev.10 / Jan.97

1

ORDERING INFORMATION

Part Name

HY512260JC

Refresh

512

Power

Package

40Pin SOJ

HY512260LJC

512

L-part

40Pin SOJ

60

550mW

Hyundai Semiconductor

JEDEC standard pinout

40-pin Plastic SOJ (400mil)

Single power supply of 5V

±

10%

Early Write or output enable controlled write

*SL : Low power with self refresh

70

495mW

70

70ns

20ns

45ns

HY512260SLJC

512

SL-part

40Pin SOJ

相关PDF资料 |

PDF描述 |

|---|---|

| HY512264LTC-60 | x16 EDO Page Mode DRAM |

| HY512264LTC-70 | x16 EDO Page Mode DRAM |

| HY512264RC-50 | x16 EDO Page Mode DRAM |

| HY512264RC-60 | x16 EDO Page Mode DRAM |

| HY512264RC-70 | x16 EDO Page Mode DRAM |

相关代理商/技术参数 |

参数描述 |

|---|---|

| HY512264LTC-60 | 制造商:未知厂家 制造商全称:未知厂家 功能描述:x16 EDO Page Mode DRAM |

| HY512264LTC-70 | 制造商:未知厂家 制造商全称:未知厂家 功能描述:x16 EDO Page Mode DRAM |

| HY512264RC-50 | 制造商:未知厂家 制造商全称:未知厂家 功能描述:x16 EDO Page Mode DRAM |

| HY512264RC-60 | 制造商:未知厂家 制造商全称:未知厂家 功能描述:x16 EDO Page Mode DRAM |

| HY512264RC-70 | 制造商:未知厂家 制造商全称:未知厂家 功能描述:x16 EDO Page Mode DRAM |

发布紧急采购,3分钟左右您将得到回复。