- 您现在的位置:买卖IC网 > PDF目录67684 > ICS1524AMT (INTEGRATED DEVICE TECHNOLOGY INC) 250 MHz, OTHER CLOCK GENERATOR, PDSO24 PDF资料下载

参数资料

| 型号: | ICS1524AMT |

| 厂商: | INTEGRATED DEVICE TECHNOLOGY INC |

| 元件分类: | 时钟产生/分配 |

| 英文描述: | 250 MHz, OTHER CLOCK GENERATOR, PDSO24 |

| 封装: | 0.300INCH, SOIC-24 |

| 文件页数: | 1/24页 |

| 文件大小: | 354K |

| 代理商: | ICS1524AMT |

Integrated

Circuit

Systems, Inc.

General Description

Features

ICS1524A

ICS1524A Rev D 12/23/2005

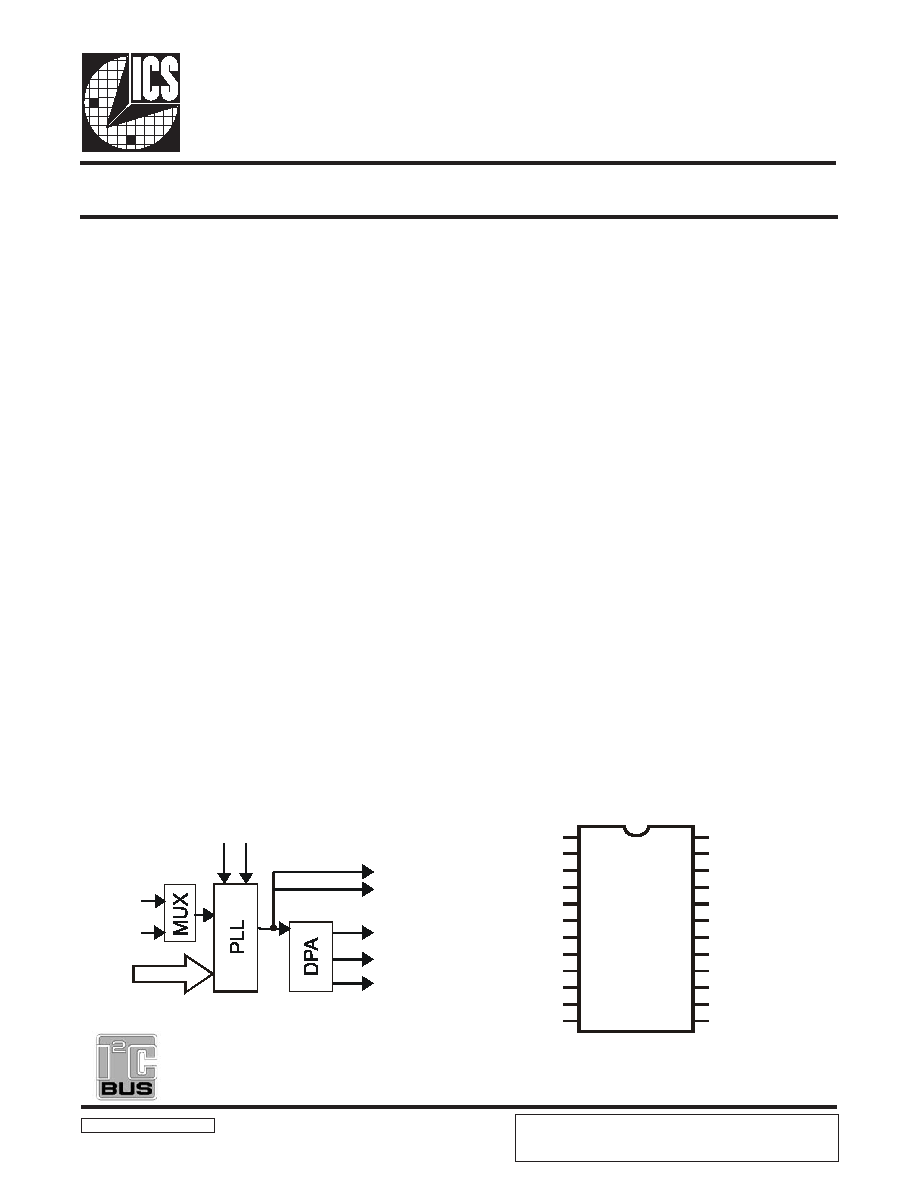

Block Diagram

Dual Output Phase Controlled SSTL_3/PECL Clock Generator

Wide input frequency range

8 kHz to 100 MHz

250 MHz balanced PECL differential outputs

150 MHz single-ended SSTL_3 clock outputs

Dynamic Phase Adjust (DPA) for DPACLK

outputs

Software controlled phase adjustment

360

o Adjustment down to 1/64 clock

increments

External or internal loop filter selection

Uses 3.3 VDC Inputs are 5 volt tolerant.

I

2C-bus serial interface runs at either low speed

(100 kHz) or high speed (400 kHz).

Hardware and Software PLL Lock detection

The ICS1524A is a low-cost, very high-performance

frequency generator and phase controlled clock synthe-

sizer. It is perfectly suited to phase controlled clock

synthesis and distribution as well as line-locked and

genlocked applications.

The ICS1524A offers two channels of clock phase con-

trolled outputs; CLK and DPACLK. These two output

channels have both 250 MHz PECL differential and 150

MHz SSTL_3 single-ended output pins. The CLK output

channel has a fixed phase relationship to the PLL’s input

and the DPACLK uses the Dynamic Phase Adjust cir-

cuitry to allow control of the clock phase relative to input

signal.

Optionally, the CLK outputs can operate at half the clock

rate and phase aligned with the DPACLK channel, en-

abling deMUXing of multiplexed analog-to-digital

converters. The FUNC pin provides either the regener-

ated input from the phase-locked loop (PLL) divider

chain output or a re-synchronized and sharpened input

HSYNC.

The advanced PLL uses either its internal program-

mable feedback divider or an external divider and is

programmed by a standard I

2C-bus serial interface.

I

2

C-bus is a trademark of Philips Corporation.

ICS reserves the right to make changes in the device data identified in this

publication without further notice. ICS advises its customers to obtain the

latest version of all device data to verify that any information being relied

upon by the customer is current and accurate.

Applications

Generic Frequency Synthesis

LCD Monitors and Projectors

Genlocking Multiple Video Systems

HSYNC

OSC

IC

2

DPACLK+/-

FUNC

DPACLK

Loop

Filter

CLK+/-

CLK

Pin Configuration

24 Pin 300-mil SOIC

IC

S

1

5

2

4

A

1

2

3

4

5

6

7

8

9

10

11

12

24

23

22

21

20

19

18

17

16

15

14

13

VDDD

VSSD

SDA

SCL

PDEN

EXTFB

HSYNC

EXTFIL

XFILRET

VDDA

VSSA

OSC

IREF

CLK+

(PECL)

C

VSSQ

VDDQ

CLK

(SSTL)

CLK

(SSTL)

FUNC

(SSTL)

LOCK/REF (SSTL)

ICADR

LK–

(PECL)

DPACLK+ (PECL)

DPACLK– (PECL)

DPA

2

相关PDF资料 |

PDF描述 |

|---|---|

| ICS1524AM | 250 MHz, OTHER CLOCK GENERATOR, PDSO24 |

| ICS1524AMT | 250 MHz, OTHER CLOCK GENERATOR, PDSO24 |

| ICS1527G-60LFTR | PLL BASED CLOCK DRIVER, 2 TRUE OUTPUT(S), 0 INVERTED OUTPUT(S), PDSO16 |

| ICS1562BM-001LF | 260 MHz, VIDEO CLOCK GENERATOR, PDSO16 |

| ICS1567M-XXX-LF | 180 MHz, VIDEO CLOCK GENERATOR, PDSO16 |

相关代理商/技术参数 |

参数描述 |

|---|---|

| ICS1524M | 制造商:ICS 制造商全称:ICS 功能描述:Dual Output Phase Controlled SSTL-3/PECL Clock Generator |

| ICS1524MT | 制造商:ICS 制造商全称:ICS 功能描述:Dual Output Phase Controlled SSTL-3/PECL Clock Generator |

| ICS1526 | 制造商:ICS 制造商全称:ICS 功能描述:Video Clock Synthesizer |

| ICS1526G | 功能描述:IC VIDEO CLK SYNTHESIZER 16TSSOP RoHS:否 类别:集成电路 (IC) >> 时钟/计时 - 时钟发生器,PLL,频率合成器 系列:- 产品变化通告:Product Discontinuation 04/May/2011 标准包装:96 系列:- 类型:时钟倍频器,零延迟缓冲器 PLL:带旁路 输入:LVTTL 输出:LVTTL 电路数:1 比率 - 输入:输出:1:8 差分 - 输入:输出:无/无 频率 - 最大:133.3MHz 除法器/乘法器:是/无 电源电压:3 V ~ 3.6 V 工作温度:0°C ~ 70°C 安装类型:表面贴装 封装/外壳:16-TSSOP(0.173",4.40mm 宽) 供应商设备封装:16-TSSOP 包装:管件 其它名称:23S08-5HPGG |

| ICS1526GILF | 功能描述:IC VIDEO CLK SYNTHESIZER 16TSSOP RoHS:是 类别:集成电路 (IC) >> 时钟/计时 - 时钟发生器,PLL,频率合成器 系列:- 标准包装:1,000 系列:Precision Edge® 类型:时钟/频率合成器 PLL:无 输入:CML,PECL 输出:CML 电路数:1 比率 - 输入:输出:2:1 差分 - 输入:输出:是/是 频率 - 最大:10.7GHz 除法器/乘法器:无/无 电源电压:2.375 V ~ 3.6 V 工作温度:-40°C ~ 85°C 安装类型:表面贴装 封装/外壳:16-VFQFN 裸露焊盘,16-MLF? 供应商设备封装:16-MLF?(3x3) 包装:带卷 (TR) 其它名称:SY58052UMGTRSY58052UMGTR-ND |

发布紧急采购,3分钟左右您将得到回复。