- 您现在的位置:买卖IC网 > PDF目录1923 > ICS1893BFILF (IDT, Integrated Device Technology Inc)PHYCEIVER LOW PWR 3.3V 48-SSOP PDF资料下载

参数资料

| 型号: | ICS1893BFILF |

| 厂商: | IDT, Integrated Device Technology Inc |

| 文件页数: | 102/133页 |

| 文件大小: | 0K |

| 描述: | PHYCEIVER LOW PWR 3.3V 48-SSOP |

| 标准包装: | 30 |

| 系列: | PHYceiver™ |

| 类型: | PHY 收发器 |

| 规程: | MII |

| 电源电压: | 3.14 V ~ 3.47 V |

| 安装类型: | 表面贴装 |

| 封装/外壳: | 48-BSSOP(0.295",7.50mm 宽) |

| 供应商设备封装: | 48-SSOP |

| 包装: | 管件 |

| 其它名称: | 1893BFILF |

第1页第2页第3页第4页第5页第6页第7页第8页第9页第10页第11页第12页第13页第14页第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页第29页第30页第31页第32页第33页第34页第35页第36页第37页第38页第39页第40页第41页第42页第43页第44页第45页第46页第47页第48页第49页第50页第51页第52页第53页第54页第55页第56页第57页第58页第59页第60页第61页第62页第63页第64页第65页第66页第67页第68页第69页第70页第71页第72页第73页第74页第75页第76页第77页第78页第79页第80页第81页第82页第83页第84页第85页第86页第87页第88页第89页第90页第91页第92页第93页第94页第95页第96页第97页第98页第99页第100页第101页当前第102页第103页第104页第105页第106页第107页第108页第109页第110页第111页第112页第113页第114页第115页第116页第117页第118页第119页第120页第121页第122页第123页第124页第125页第126页第127页第128页第129页第130页第131页第132页第133页

ICS1893BF, Rev. F, 5/13/10

May, 2010

70

Chapter 7 Management Register Set

ICS1893BF Data Sheet - Release

Copyright 2009, IDT, Inc.

All rights reserved.

7.8 Register 6: Auto-Negotiation Expansion Register

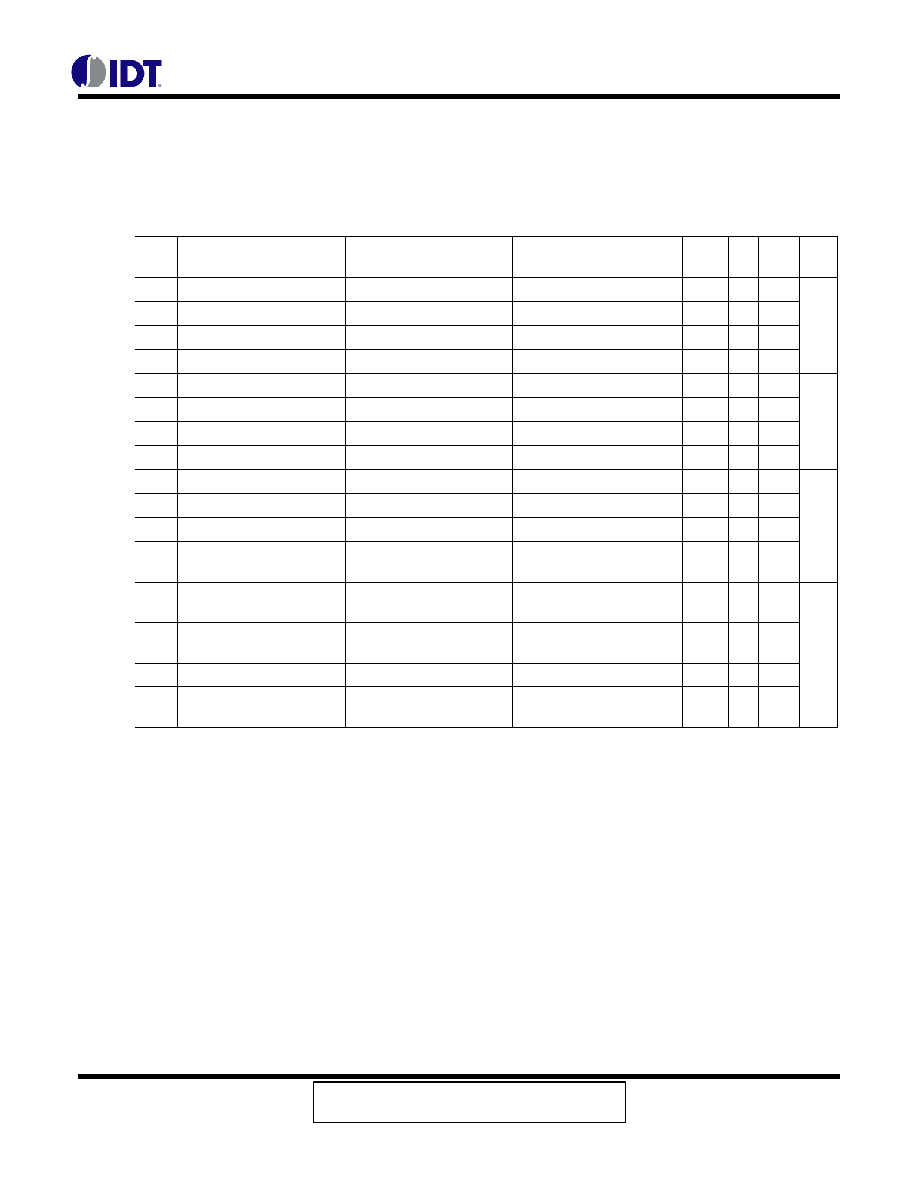

Table 7-13 lists the bits for the Auto-Negotiation Expansion Register, which indicates the status of the

Auto-Negotiation process.

Note: For an explanation of acronyms used in Table 7-13, see Chapter 1, “Abbreviations and Acronyms”.

As per the IEEE Std 802.3u, during any write operation to any bit in this register, the STA must write the default value

to all Reserved bits.

7.8.1 IEEE Reserved Bits (bits 6.15:5)

The ISO/IEC specification reserves these bits for future use. When an STA:

Reads a reserved bit, the ICS1893BF returns a logic zero.

Writes to a reserved bit, the STA must use the default value specified in this data sheet.

ICS uses some reserved bits to invoke auxiliary functions. To ensure proper operation of the ICS1893BF,

an STA must maintain the default value of these bits. Therefore, IDT recommends that an STA always write

the default value of any reserved bits during all management register write operations.

Reserved bits 5.15:5 are Command Override Write (CW) bits. When the Command Register Override bit

(bit 16.15) is logic:

Zero, the ICS1893BF isolates all STA writes to CW bits.

One, an STA can modify the value of these bits

Table 7-13. Auto-Negotiation Expansion Register (register 6 [0x06])

Bit

Definition

When Bit = 0

When Bit = 1

Ac-

cess

SF

De-

fault

Hex

6.15

IEEE reserved

Always 0

N/A

CW

–

0

6.14

IEEE reserved

Always 0

N/A

CW

–

0

6.13

IEEE reserved

Always 0

N/A

CW

–

0

6.12

IEEE reserved

Always 0

N/A

CW

–

0

6.11

IEEE reserved

Always 0

N/A

CW

–

0

6.10

IEEE reserved

Always 0

N/A

CW

–

0

6.9

IEEE reserved

Always 0

N/A

CW

–

0

6.8

IEEE reserved

Always 0

N/A

CW

–

0

6.7

IEEE reserved

Always 0

N/A

CW

–

0

6.6

IEEE reserved

Always 0

N/A

CW

–

0

6.5

IEEE reserved

Always 0

N/A

CW

–

0

6.4

Parallel detection fault

No Fault

Multiple technologies

detected

RO

LH

0

6.3

Link partner Next Page

able

Link partner is not Next

Page able

Link partner is Next Page

able

RO

–

0

4

6.2

Next Page able

Local device is not Next

Page able

Local device is Next Page

able

RO

–

1

6.1

Page received

Next Page not received

Next Page received

RO

LH

0

6.0

Link partner

Auto-Negotiation able

Link partner is not

Auto-Negotiation able

Link partner is

Auto-Negotiation able

RO

–

0

相关PDF资料 |

PDF描述 |

|---|---|

| ICS1894KI-32LF | PHYCEIVER LOW PWR 3.3V 32QFN |

| ICS1894KI-40LFT | PHYCEIVER LOW PWR 3.3V 40QFN |

| ID82C55A | IC I/O EXPANDER 24B 40DIP |

| ID82C82 | IC DRIVER BUS OCT LATCHING 20DIP |

| ID82C86H | IC TRANSCEIVER OCT BUS 20-DIP |

相关代理商/技术参数 |

参数描述 |

|---|---|

| ICS1893BFILFT | 功能描述:PHYCEIVER LOW PWR 3.3V 48-SSOP RoHS:是 类别:集成电路 (IC) >> 接口 - 驱动器,接收器,收发器 系列:PHYceiver™ 标准包装:250 系列:- 类型:收发器 驱动器/接收器数:2/2 规程:RS232 电源电压:3 V ~ 5.5 V 安装类型:表面贴装 封装/外壳:16-TSSOP(0.173",4.40mm 宽) 供应商设备封装:16-TSSOP 包装:带卷 (TR) |

| ICS1893BFIT | 功能描述:PHYCEIVER LOW PWR 3.3V 48-SSOP RoHS:否 类别:集成电路 (IC) >> 接口 - 驱动器,接收器,收发器 系列:PHYceiver™ 标准包装:1,000 系列:- 类型:收发器 驱动器/接收器数:2/2 规程:RS232 电源电压:3 V ~ 5.5 V 安装类型:表面贴装 封装/外壳:16-SOIC(0.295",7.50mm 宽) 供应商设备封装:16-SOIC 包装:带卷 (TR) |

| ICS1893BFLF | 功能描述:PHYCEIVER LOW PWR 3.3V 48-SSOP RoHS:是 类别:集成电路 (IC) >> 接口 - 驱动器,接收器,收发器 系列:PHYceiver™ 标准包装:250 系列:- 类型:收发器 驱动器/接收器数:2/2 规程:RS232 电源电压:3 V ~ 5.5 V 安装类型:表面贴装 封装/外壳:16-TSSOP(0.173",4.40mm 宽) 供应商设备封装:16-TSSOP 包装:带卷 (TR) |

| ICS1893BFLFT | 功能描述:PHYCEIVER LOW PWR 3.3V 48-SSOP RoHS:是 类别:集成电路 (IC) >> 接口 - 驱动器,接收器,收发器 系列:PHYceiver™ 标准包装:250 系列:- 类型:收发器 驱动器/接收器数:2/2 规程:RS232 电源电压:3 V ~ 5.5 V 安装类型:表面贴装 封装/外壳:16-TSSOP(0.173",4.40mm 宽) 供应商设备封装:16-TSSOP 包装:带卷 (TR) |

| ICS1893BFT | 功能描述:PHYCEIVER LOW PWR 3.3V 48-SSOP RoHS:是 类别:集成电路 (IC) >> 接口 - 驱动器,接收器,收发器 系列:PHYceiver™ 标准包装:1,000 系列:- 类型:收发器 驱动器/接收器数:2/2 规程:RS232 电源电压:3 V ~ 5.5 V 安装类型:表面贴装 封装/外壳:16-SOIC(0.295",7.50mm 宽) 供应商设备封装:16-SOIC 包装:带卷 (TR) |

发布紧急采购,3分钟左右您将得到回复。