- 您现在的位置:买卖IC网 > PDF目录9208 > ICS307M-02LFT (IDT, Integrated Device Technology Inc)IC CLOCK SOURCE PROGR 16-SOIC PDF资料下载

参数资料

| 型号: | ICS307M-02LFT |

| 厂商: | IDT, Integrated Device Technology Inc |

| 文件页数: | 7/10页 |

| 文件大小: | 0K |

| 描述: | IC CLOCK SOURCE PROGR 16-SOIC |

| 产品培训模块: | Clock Distibution and Generation 1.0 |

| 标准包装: | 1 |

| 类型: | 时钟发生器 |

| PLL: | 带旁路 |

| 输入: | 时钟,晶体 |

| 输出: | LVCMOS |

| 电路数: | 1 |

| 比率 - 输入:输出: | 2:2 |

| 差分 - 输入:输出: | 无/无 |

| 频率 - 最大: | 200MHz |

| 除法器/乘法器: | 是/无 |

| 电源电压: | 3 V ~ 5.5 V |

| 工作温度: | 0°C ~ 70°C |

| 安装类型: | 表面贴装 |

| 封装/外壳: | 16-SOIC(0.154",3.90mm 宽) |

| 供应商设备封装: | 16-SOIC |

| 包装: | 标准包装 |

| 产品目录页面: | 1251 (CN2011-ZH PDF) |

| 其它名称: | 800-1798-6 |

ICS307-01/-02

SERIALLY PROGRAMMABLE CLOCK SOURCE

SER PROG CLOCK SYNTHESIZER

IDT / ICS SERIALLY PROGRAMMABLE CLOCK SOURCE

6

ICS307-01/-02 REV J 051310

Programming Example

To generate 66.66 MHz from a 14.31818 MHz input, the RDW should be 59, the VDW should be 276, and

the Output Divide is 2. Selecting the minimum internal load capacitance, CMOS duty cycle, and CLK2 to be

OFF means that the following three bytes are sent to the ICS307:

As show in Figure 2, after these 24 bits are clocked into the ICS307, taking STROBE high will send this

data to the internal latch and the CLK output will lock within 10 ms.

Note: If STROBE is in the high state and SCLK is pulsed, DATA is clocked directly to the internal latch and

the output conditions will change accordingly. Although this will not damage the ICS307, it is recommended

that STROBE be kept low while DATA is being clocked into the ICS307 in order to avoid unintended

changes on the output clocks.

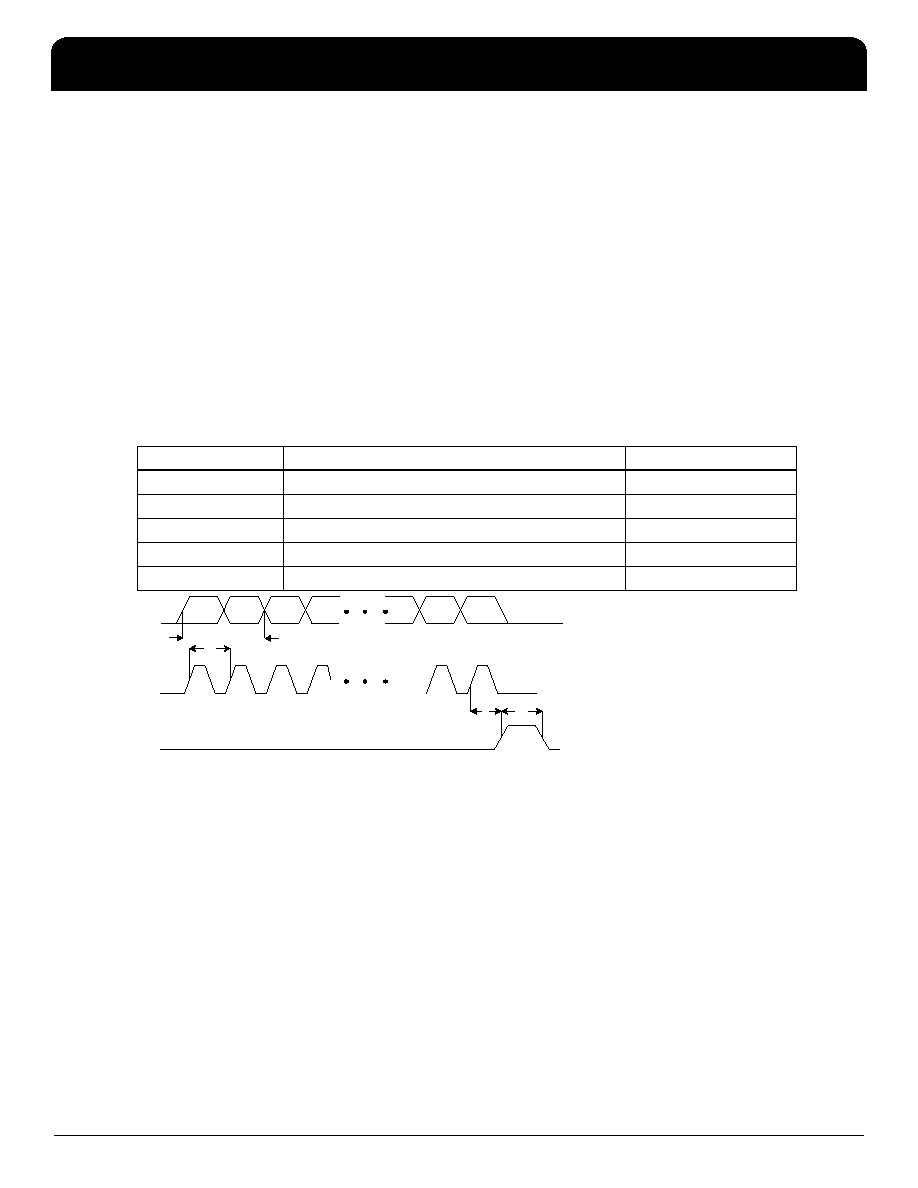

AC Parameters for Writing to the ICS307

External Components/Crystal Selection

The ICS307 requires a 0.01

F decoupling capacitor to be connected between VDD and GND. It must be connected

close to the ICS307 to minimize lead inductance. A 33

terminating resistor can be used in series with CLK1 and

CLK2 outputs. A parallel resonant, fundamental mode crystal with a load (correlation) capacitance of C should be

used, where C is the value calculated from Table 4. For crystals with a specified load capacitance greater than C,

additional crystal capacitors may be connected from each of the pins X1 and X2 to ground as shown in the Block

Diagram on page 1. The value (in pF) of these crystal caps should be = (CL-C)*2, where CL is the crystal load

capacitance in pF and C is the capacitance value from Table 4. These external capacitors are only required for

applications where the exact frequency is critical. For a clock input, connect to X1 and leave X2 unconnected (no

capacitors on either pin).

00110001

10001010

00111011

Byte 1

Byte 2

Byte 3

Parameter

Condition

Min.

Max.

Units

tSETUP

Setup time

10

ns

tHOLD

Hold time after SCLK

10

ns

tW

Data wait time

10

ns

tS

Strobe pulse width

40

ns

SCLK Frequency

50

MHz

DATA

F1

TTL

C0

C1

R1

R0

t

hold

t

setup

SCLK

STROBE

t

s

t

w

Figure 2. Timing Diagram for Programming the ICS307

相关PDF资料 |

PDF描述 |

|---|---|

| X9268TS24Z-2.7T1 | IC XDCP DUAL 256TAP 100K 24-SOIC |

| VE-2W0-MW | CONVERTER MOD DC/DC 5V 100W |

| X9241AMSZ | IC XDCP QUAD 2/10/10/50K 20-S |

| X9418WS24IZ-2.7T1 | IC XDCP DUAL 64TAP 10K 24-SOIC |

| VE-2VP-MX-B1 | CONVERTER MOD DC/DC 13.8V 75W |

相关代理商/技术参数 |

参数描述 |

|---|---|

| ICS307M-02T | 功能描述:IC SRL PROGR CLK SOURCE 16-SOIC RoHS:否 类别:集成电路 (IC) >> 时钟/计时 - 时钟发生器,PLL,频率合成器 系列:- 产品变化通告:Product Discontinuation 04/May/2011 标准包装:96 系列:- 类型:时钟倍频器,零延迟缓冲器 PLL:带旁路 输入:LVTTL 输出:LVTTL 电路数:1 比率 - 输入:输出:1:8 差分 - 输入:输出:无/无 频率 - 最大:133.3MHz 除法器/乘法器:是/无 电源电压:3 V ~ 3.6 V 工作温度:0°C ~ 70°C 安装类型:表面贴装 封装/外壳:16-TSSOP(0.173",4.40mm 宽) 供应商设备封装:16-TSSOP 包装:管件 其它名称:23S08-5HPGG |

| ICS308 | 制造商:ICS 制造商全称:ICS 功能描述:SERIAL PROGRAMMABLE QUAD PLL VERSACLOCK SYNTHESIZER |

| ICS-308-AGG | 制造商:Samtec Inc 功能描述:CONN DIP SCKT SKT 8 POS 2.54MM SLDR ST TH - Bulk |

| ICS-308-AGT | 制造商:Samtec Inc 功能描述:CONN DIP SCKT SKT 8 POS 2.54MM SLDR ST TH - Bulk |

| ICS-308-ATT | 制造商:Samtec Inc 功能描述:CONN DIP SCKT SKT 8 POS 2.54MM SLDR ST TH - Bulk |

发布紧急采购,3分钟左右您将得到回复。