- 您现在的位置:买卖IC网 > PDF目录175707 > ICS5342-3 Analog IC PDF资料下载

参数资料

| 型号: | ICS5342-3 |

| 英文描述: | Analog IC |

| 中文描述: | 模拟IC |

| 文件页数: | 3/36页 |

| 文件大小: | 1017K |

| 代理商: | ICS5342-3 |

第1页第2页当前第3页第4页第5页第6页第7页第8页第9页第10页第11页第12页第13页第14页第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页第29页第30页第31页第32页第33页第34页第35页第36页

ICS5342

GENDAC

11

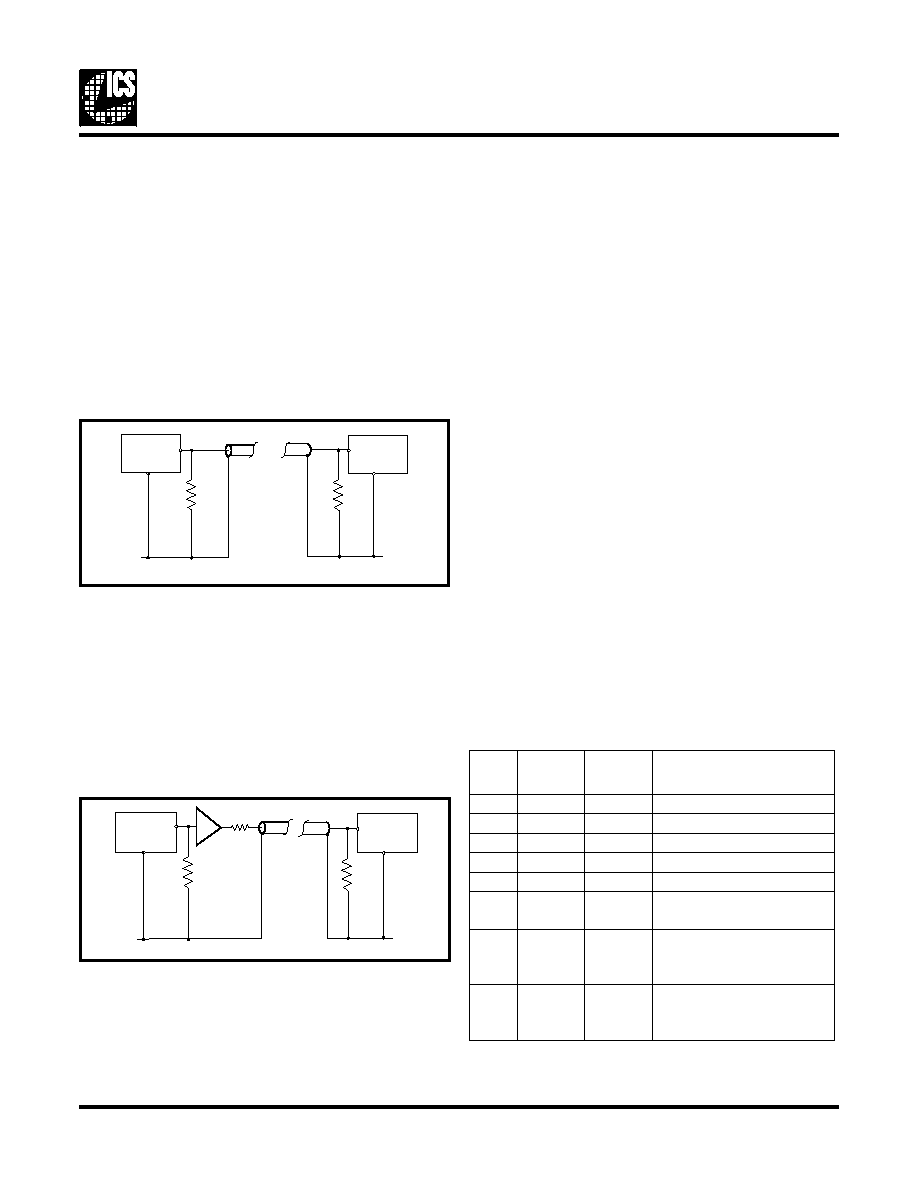

Double Termination (Figure 1)

For this termination scheme, a load resistor is placed at both

the DAC output and the monitor input. The resistor values

should be equal to the characteristic impedance of the line.

Double termination of the DAC output allows both ends of the

transmission line between the DAC outputs and the monitor

inputs to be correctly matched.The result should be an ideal

reflection-free system.

This arrangement is relatively tolerant of variations in trans-

mission line impedance (e.g. a mismatched connector) since

no reflections occur from either end of the line. A doubly ter-

minated DAC output will rise faster than any singly terminat-

ed output because the rise time of the DAC outputs is

dependent on the RC time constant of the load.

Double Termination

If the GENDAC drives large capacitive loads (for instance

long cable runs), it may be necessary to buffer the DAC out-

puts. The buffer will have a relatively high input impedance.

The connection between the DAC outputs and the buffer in-

puts should also be considered as a transmission line. The

buffer output will have a relatively low impedance. It should

be matched to the transmission line between it and the monitor

with a series terminating resistor. The transmission line

should be terminated at the monitor.

Buffered Signal

SENSE Output

The GENDAC contains three comparators, one for each of the

DAC output R, G and B lines. The reference voltage to the

comparators is proportional to the VREF (internal or external)

and is typically 0.330 for VREF=1.235 Volts. The SENSE*

pin will be driven low when any analog video output is above

0.385 mV. SENSE* output will be high when all analog out-

puts are below 275 mV. This signal is used to detect the type

of (or lack of) monitor connected to the system.

PLL Clock

The ICS5342 has dual PLL frequency generators for generat-

ing the video clock (CLK0) and memory clock (CLK1) need-

ed for graphics subsystems. Both of these clocks are

generated from a single 14.318 MHz crystal or they can be

driven from an external clock source. The chip includes the

capacitors for the crystal and all of the components needed for

the PLL loop filters, minimizing board component count.

There are eight possible video clock, CLK0, frequencies (f0-

f7) which can be selected by the external pins CS1-CS0. All

clocks are software selectable by setting a bit in the PLL con-

trol register. Frequencies f0-f7 can be programmed for any

frequency by writing appropriate parameter values to the PLL

parameter registers. The default frequencies on power up are

commonly used video frequencies (see table “Video Clock

Default Frequency Registers”). At power up, the frequencies

can be selected by pins CS2-CS0. There are two programma-

ble memory clock frequencies (fA, fB). On power up this fre-

quency defaults to the frequency given in the table:

“MemoryClock Default Frequency Registers.” The memory

clock transition between frequencies is smooth and glitch free

if the N2 PLL parameter is not changed from its previous set-

ting.

* With 14.318 MHz input.

R

LOAD

R

LOAD

MONITOR

ICS5342

Ground

5342_05

R

T

R

LOAD

MONITOR

ICS5342

Ground

R

S

5342_06

Video Clock (CLK0) Default Frequency Register *

fn

VCLK

(MHz)

M & N

Code

Comments

f0

25.175

7D 50

VGA0 (VGA Graphics)

f1

28.322

55 49

VGA1 (VGA Text)

f2

31.500

2A 43

VESA 640 x 480 @72 Hz

f3

36.00

77 4A

VESA 800 x 600 @56 Hz

f4

40.00

79 49

VESA 800 x 600 @60 Hz

f5

44.889

6F 47

1024 x 768 @43 Hz Inter-

laced

f6

65.00

74 2B

1024 x 768 @ 60 Hz,

640 x 480 Hi-Color @ 72

Hz

f7

75.00

71 29

VESA 1024 x 768 @ 70

Hz,

True Color 640 x 480

相关PDF资料 |

PDF描述 |

|---|---|

| ICS9111M-06 | Miscellaneous Clock Generator |

| ICS9117M02 | Peripheral IC |

| ICS9118M-02 | Miscellaneous Clock Generator |

| ICS9118M-04 | Miscellaneous Clock Generator |

| ICS9120M-51 | Miscellaneous Clock Generator |

相关代理商/技术参数 |

参数描述 |

|---|---|

| ICS5342ADD | 制造商:ICS 制造商全称:ICS 功能描述:Addendum to ICS5342 Data Sheet |

| ICS5342V | 制造商:未知厂家 制造商全称:未知厂家 功能描述:Peripheral IC |

| ICS541 | 制造商:ICS 制造商全称:ICS 功能描述:PRELIMINARY INFORMATION PLL Clock Divider |

| ICS541M | 制造商:ICS 制造商全称:ICS 功能描述:PRELIMINARY INFORMATION PLL Clock Divider |

| ICS541MT | 制造商:ICS 制造商全称:ICS 功能描述:PRELIMINARY INFORMATION PLL Clock Divider |

发布紧急采购,3分钟左右您将得到回复。