- 您现在的位置:买卖IC网 > PDF目录65530 > ICS558G-01LF (INTEGRATED DEVICE TECHNOLOGY INC) 558 SERIES, LOW SKEW CLOCK DRIVER, 4 TRUE OUTPUT(S), 0 INVERTED OUTPUT(S), PDSO16 PDF资料下载

参数资料

| 型号: | ICS558G-01LF |

| 厂商: | INTEGRATED DEVICE TECHNOLOGY INC |

| 元件分类: | 时钟及定时 |

| 英文描述: | 558 SERIES, LOW SKEW CLOCK DRIVER, 4 TRUE OUTPUT(S), 0 INVERTED OUTPUT(S), PDSO16 |

| 封装: | 4.40 MM, 0.65 MM PITCH, ROHS COMPLIANT, MO-153, TSSOP-16 |

| 文件页数: | 2/6页 |

| 文件大小: | 178K |

| 代理商: | ICS558G-01LF |

ICS558-01

PECL/CMOS TO CMOS CLOCK DRIVER

PECL CLOCK DRIVER

IDT / ICS PECL/CMOS TO CMOS CLOCK DRIVER

2

ICS558-01

REV D 072806

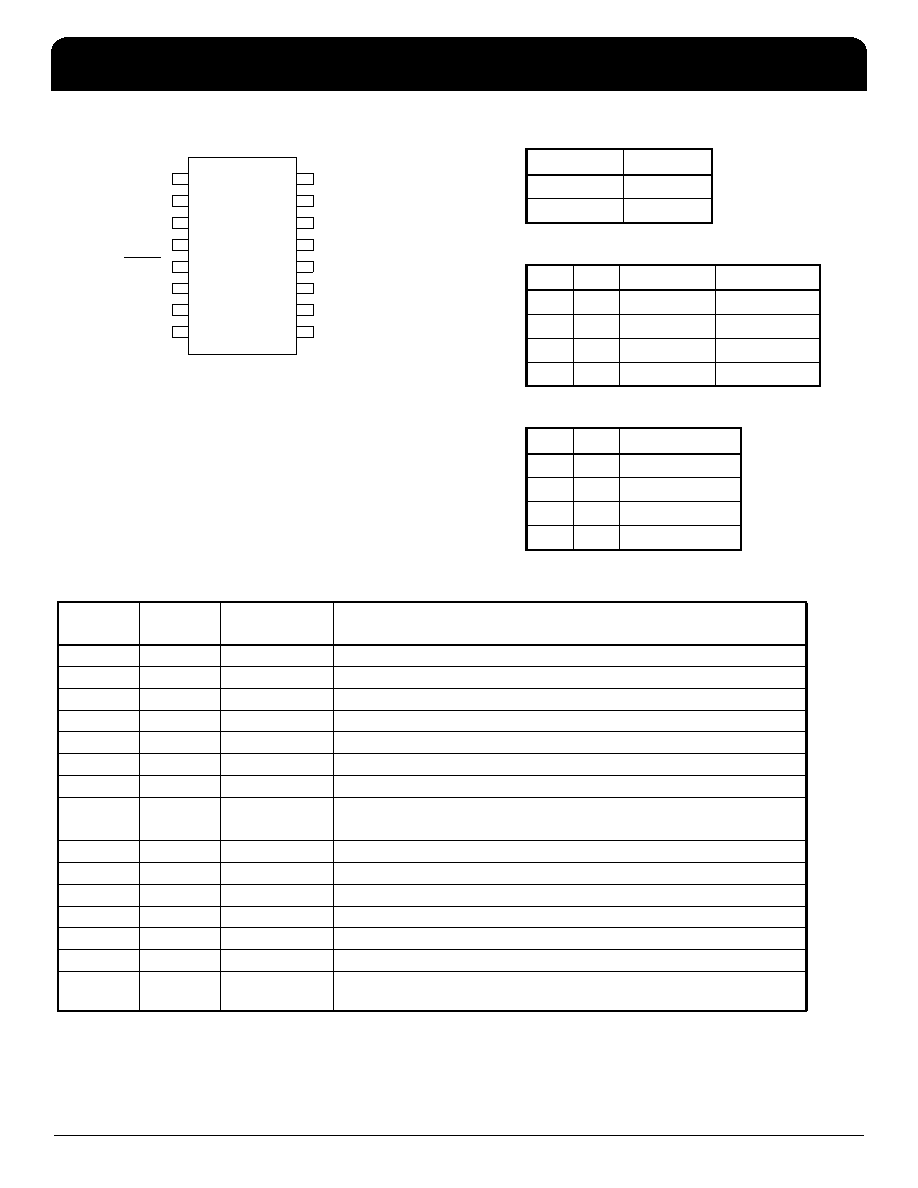

Pin Assignment

Input Clock Selection

Tri-State Table

Output Divide Selection

Pin Descriptions

12

1

11

2

10

3

9

S0

4

S1

5

VDDP

6

VDDC

7

PECLIN

8

PECLIN

CLK1

CLK2

CLK3

GND

CLK4

OE1

CMOSIN

GND

16

15

14

13

OE0

SELPECL

16-pin 173 Mil (0.65mm) TSSOP

SELPECL

Input

0CMOSIN

1

PECLIN

OE1 OE0

CLK 1

CLK 2, 3, 4

0

Tri-state

0

1

Clock ON

Tri-state

1

0

Tri-state

Clock ON

1

Clock ON

S1

S0

Output Divide

00

/1

01

/2

10

/3

11

/4

Pin

Number

Pin

Name

Pin Type

Pin Description

1

S0

Input

Select 0 for output divider. See table above. Internal pull-up to VDDP.

2

S1

Input

Select 1 for output divider. See table above. Internal pull-up to VDDP.

3

VDDP

Power

Connect to +3.3 V or +5 V. Decouple to pin 6.

4

PECLIN

Clock Input

PECL input. Connect to ground if not used.

5

PECLIN

Clock Input

Complimentary PECL input. Connect to ground if not used.

6

GND

Power

Connect to ground.

7

CMOSIN

Clock Input

CMOS input. Connect to ground if not used.

8

OE0

Input

Output Enable 0. See table above. Internal pull-up to VDDP.

9

OE1

Input

Output Enable 1. See table above. Internal pull-up to VDDP.

10

GND

Power

Connect to ground.

11

CLK4

Output

Low skew clock output.

12

CLK3

Output

Low skew clock output.

13

CLK2

Output

Low skew clock output.

14

CLK1

Output

Low skew clock output.

15

VDDC

Power

Connect to +2.5 V, +3.3 V, or +5 V. Decouple to pin 10.

16

SELPECL

Input

Selects PECL or CMOS input. See table above. Internal pull-up to

VDDP.

相关PDF资料 |

PDF描述 |

|---|---|

| ICS558G-02 | LOW SKEW CLOCK DRIVER, 4 TRUE OUTPUT(S), 0 INVERTED OUTPUT(S), PDSO16 |

| ICS558G-02LF | LOW SKEW CLOCK DRIVER, 4 TRUE OUTPUT(S), 0 INVERTED OUTPUT(S), PDSO16 |

| ICS558G-02LFT | LOW SKEW CLOCK DRIVER, 4 TRUE OUTPUT(S), 0 INVERTED OUTPUT(S), PDSO16 |

| ICS570BIT | 570 SERIES, PLL BASED CLOCK DRIVER, 2 TRUE OUTPUT(S), 0 INVERTED OUTPUT(S), PDSO8 |

| ICS570MLFT | 570 SERIES, PLL BASED CLOCK DRIVER, 2 TRUE OUTPUT(S), 0 INVERTED OUTPUT(S), PDSO8 |

相关代理商/技术参数 |

参数描述 |

|---|---|

| ICS558G-01LFT | 功能描述:IC CLK BUFF DVDR MUX 2:4 16TSSOP RoHS:是 类别:集成电路 (IC) >> 时钟/计时 - 时钟缓冲器,驱动器 系列:ClockBlocks™ 标准包装:74 系列:- 类型:扇出缓冲器(分配) 电路数:1 比率 - 输入:输出:1:10 差分 - 输入:输出:是/是 输入:HCSL, LVCMOS, LVDS, LVPECL, LVTTL 输出:HCSL,LVDS 频率 - 最大:400MHz 电源电压:3 V ~ 3.6 V 工作温度:-40°C ~ 85°C 安装类型:表面贴装 封装/外壳:32-VFQFN 裸露焊盘 供应商设备封装:32-QFN(5x5) 包装:管件 |

| ICS558G-01T | 功能描述:IC CLK BUFF DVDR MUX 2:4 16TSSOP RoHS:否 类别:集成电路 (IC) >> 时钟/计时 - 时钟缓冲器,驱动器 系列:ClockBlocks™ 标准包装:1 系列:HiPerClockS™ 类型:扇出缓冲器(分配),多路复用器 电路数:1 比率 - 输入:输出:2:18 差分 - 输入:输出:是/无 输入:CML,LVCMOS,LVPECL,LVTTL,SSTL 输出:LVCMOS,LVTTL 频率 - 最大:250MHz 电源电压:2.375 V ~ 3.465 V 工作温度:0°C ~ 70°C 安装类型:表面贴装 封装/外壳:32-LQFP 供应商设备封装:32-TQFP(7x7) 包装:- 其它名称:800-1923-6 |

| ICS558G-02 | 功能描述:IC CLK BUFF DIVIDER 1:4 16-TSSOP RoHS:否 类别:集成电路 (IC) >> 时钟/计时 - 时钟缓冲器,驱动器 系列:ClockBlocks™ 标准包装:74 系列:- 类型:扇出缓冲器(分配) 电路数:1 比率 - 输入:输出:1:10 差分 - 输入:输出:是/是 输入:HCSL, LVCMOS, LVDS, LVPECL, LVTTL 输出:HCSL,LVDS 频率 - 最大:400MHz 电源电压:3 V ~ 3.6 V 工作温度:-40°C ~ 85°C 安装类型:表面贴装 封装/外壳:32-VFQFN 裸露焊盘 供应商设备封装:32-QFN(5x5) 包装:管件 |

| ICS558G-02T | 功能描述:IC CLK BUFF DIVIDER 1:4 16-TSSOP RoHS:否 类别:集成电路 (IC) >> 时钟/计时 - 时钟缓冲器,驱动器 系列:ClockBlocks™ 标准包装:74 系列:- 类型:扇出缓冲器(分配) 电路数:1 比率 - 输入:输出:1:10 差分 - 输入:输出:是/是 输入:HCSL, LVCMOS, LVDS, LVPECL, LVTTL 输出:HCSL,LVDS 频率 - 最大:400MHz 电源电压:3 V ~ 3.6 V 工作温度:-40°C ~ 85°C 安装类型:表面贴装 封装/外壳:32-VFQFN 裸露焊盘 供应商设备封装:32-QFN(5x5) 包装:管件 |

| ICS570 | 制造商:ICS 制造商全称:ICS 功能描述:Multiplier and Zero Delay Buffer |

发布紧急采购,3分钟左右您将得到回复。