- 您现在的位置:买卖IC网 > PDF目录67110 > ICS650R-01LF (INTEGRATED DEVICE TECHNOLOGY INC) 80 MHz, PROC SPECIFIC CLOCK GENERATOR, PDSO20 PDF资料下载

参数资料

| 型号: | ICS650R-01LF |

| 厂商: | INTEGRATED DEVICE TECHNOLOGY INC |

| 元件分类: | 时钟产生/分配 |

| 英文描述: | 80 MHz, PROC SPECIFIC CLOCK GENERATOR, PDSO20 |

| 封装: | 0.150 INCH, LEAD FREE, SSOP-20 |

| 文件页数: | 2/8页 |

| 文件大小: | 237K |

| 代理商: | ICS650R-01LF |

System Peripheral Clock Source

MDS 650-01 F

2

Revision 082505

Integrated Circuit Systems, Inc.

● 525 Race Street, San Jose, CA 95126 ● tel (408) 297-1201 ● www.icst.com

ICS650-01

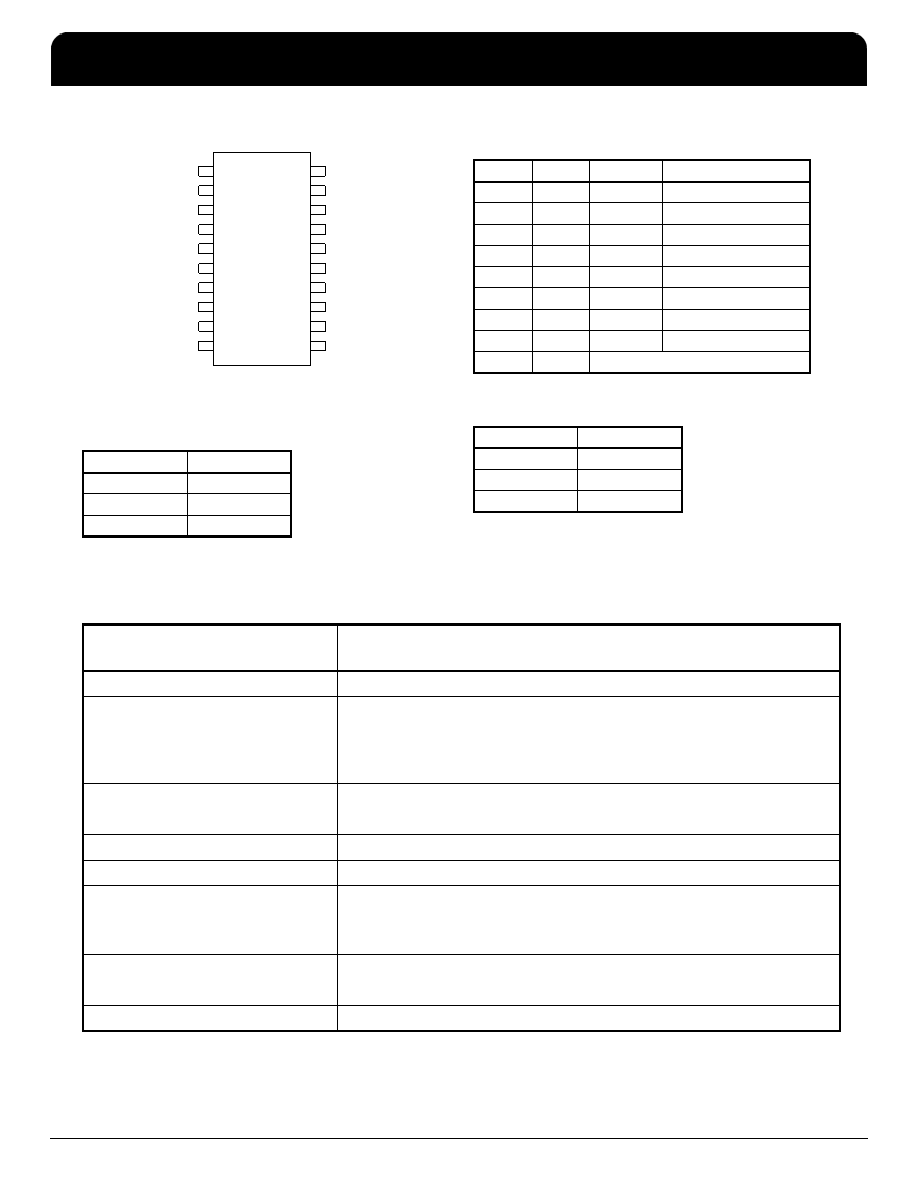

Pin Assignment

USB Clock (MHz)

Processor Clock (MHz)

Audio Clock (MHz)

0 = connect directly to ground

1 = connect directly to VDD

M = leave unconnected (floating)

Pin Descriptions

USEL

UCLK

012

M24

148

13

4

12

5

11

VDD

8

9

10

VDD

20M

14.318M

OE

ACLK

PCLK1

17

16

PCLK4

3

X1/ICLK

VDD

PCLK3

18

PCLK2

1

USEL

X2

PSEL0

20

PSEL1

19

14

2

7

GND

UCLK

ASEL

GND

15

6

20 pin (150 mil) SSOP

PSEL1

PSEL0

PCLK1

PCLK2, 3

PCLK4

0

25

50

18.75

0

M

TEST

0

1

TEST

M

0

40

80

20

M

33.3334

66.6667

25

M

1

20

40

25

1

0

20

33.3334

25

1

M

20

66.6667

25

1

Stops low all clocks except 20M

ASEL

ACLK

0

49.152

M

24.576

1

12.288

Pin

Number

Pin

Name

Pin

Type

Pin Description

1

USEL

Input

UCLK select pin. Determines frequency of USB clock per table above.

2

X2

XO

Crystal connection. Connect to parallel mode 14.31818 MHz crystal.

Leave open for clock.

3

X1/ICLK

XI

Crystal connection. Connect to parallel mode 14.31818 MHz crystal or

clock.

4

VDD

Power

Connect to VDD. Must be same value as other VDD. Decouple with pin 6.

5

VDD

Power

Connect to VDD. Must be same value as other VDD.

6

GND

Power

Connect to ground.

7

UCLK

Output

USB clock output per table above.

8

20M

Output

Fixed 20 MHz output for Ethernet. Only clock that runs when

PSEL1=PSEL0=1.

9

ACLK

Output

AC97 audio clock output per table above.

10

PCLK4

Output

PCLK output number 4 per table above.

11

OE

Input

Output enable. Tri-states all outputs when low.

12

PCLK1

Output

PCLK output number 1 per table above.

ICS650-01

System Peripheral Clock Source

TSD

IDT / ICS System Peripheral Clock Source

ICS650-01

2

相关PDF资料 |

PDF描述 |

|---|---|

| ICS650R-01T | 80 MHz, PROC SPECIFIC CLOCK GENERATOR, PDSO20 |

| ICS650R-01 | 80 MHz, PROC SPECIFIC CLOCK GENERATOR, PDSO20 |

| ICS662M-02 | 662 SERIES, PLL BASED CLOCK DRIVER, 1 TRUE OUTPUT(S), 0 INVERTED OUTPUT(S), PDSO8 |

| ICS670M-01 | 670 SERIES, PLL BASED CLOCK DRIVER, 1 TRUE OUTPUT(S), 0 INVERTED OUTPUT(S), PDSO16 |

| ICS670M-01ILFT | 670 SERIES, PLL BASED CLOCK DRIVER, 1 TRUE OUTPUT(S), 0 INVERTED OUTPUT(S), PDSO16 |

相关代理商/技术参数 |

参数描述 |

|---|---|

| ICS650R-01LFT | 功能描述:IC CLK SYNTHESIZER 20-SSOP RoHS:是 类别:集成电路 (IC) >> 时钟/计时 - 时钟发生器,PLL,频率合成器 系列:- 标准包装:2,000 系列:- 类型:PLL 时钟发生器 PLL:带旁路 输入:LVCMOS,LVPECL 输出:LVCMOS 电路数:1 比率 - 输入:输出:2:11 差分 - 输入:输出:是/无 频率 - 最大:240MHz 除法器/乘法器:是/无 电源电压:3.135 V ~ 3.465 V 工作温度:0°C ~ 70°C 安装类型:表面贴装 封装/外壳:32-LQFP 供应商设备封装:32-TQFP(7x7) 包装:带卷 (TR) |

| ICS650R-01T | 功能描述:IC CLK SYNTHESIZER 20-SSOP RoHS:否 类别:集成电路 (IC) >> 时钟/计时 - 时钟发生器,PLL,频率合成器 系列:- 产品变化通告:Product Discontinuation 04/May/2011 标准包装:96 系列:- 类型:时钟倍频器,零延迟缓冲器 PLL:带旁路 输入:LVTTL 输出:LVTTL 电路数:1 比率 - 输入:输出:1:8 差分 - 输入:输出:无/无 频率 - 最大:133.3MHz 除法器/乘法器:是/无 电源电压:3 V ~ 3.6 V 工作温度:0°C ~ 70°C 安装类型:表面贴装 封装/外壳:16-TSSOP(0.173",4.40mm 宽) 供应商设备封装:16-TSSOP 包装:管件 其它名称:23S08-5HPGG |

| ICS650R-05 | 制造商:ICS 制造商全称:ICS 功能描述:HDTV Clock Synthesizer |

| ICS650R-05T | 制造商:ICS 制造商全称:ICS 功能描述:HDTV Clock Synthesizer |

| ICS650R-07 | 功能描述:IC NETWORKING CLK SOURCE 20-SSOP RoHS:否 类别:集成电路 (IC) >> 时钟/计时 - 时钟发生器,PLL,频率合成器 系列:- 产品变化通告:Product Discontinuation 04/May/2011 标准包装:96 系列:- 类型:时钟倍频器,零延迟缓冲器 PLL:带旁路 输入:LVTTL 输出:LVTTL 电路数:1 比率 - 输入:输出:1:8 差分 - 输入:输出:无/无 频率 - 最大:133.3MHz 除法器/乘法器:是/无 电源电压:3 V ~ 3.6 V 工作温度:0°C ~ 70°C 安装类型:表面贴装 封装/外壳:16-TSSOP(0.173",4.40mm 宽) 供应商设备封装:16-TSSOP 包装:管件 其它名称:23S08-5HPGG |

发布紧急采购,3分钟左右您将得到回复。