- 您现在的位置:买卖IC网 > PDF目录61070 > ICS671G-06IT (INTEGRATED DEVICE TECHNOLOGY INC) 671 SERIES, PLL BASED CLOCK DRIVER, 8 TRUE OUTPUT(S), 0 INVERTED OUTPUT(S), PDSO16 PDF资料下载

参数资料

| 型号: | ICS671G-06IT |

| 厂商: | INTEGRATED DEVICE TECHNOLOGY INC |

| 元件分类: | 时钟及定时 |

| 英文描述: | 671 SERIES, PLL BASED CLOCK DRIVER, 8 TRUE OUTPUT(S), 0 INVERTED OUTPUT(S), PDSO16 |

| 封装: | 4.40 MM, 0.65 MM PITCH, TSSOP-16 |

| 文件页数: | 1/7页 |

| 文件大小: | 178K |

| 代理商: | ICS671G-06IT |

ICS671-06

MDS 671-06 C

1

Revision 011705

Integrated Circuit Systems l 525 Race Street, San Jose, CA 95126 l tel (408) 297-1201 l

www.icst.com

3.3 VOLT ZERO DELAY, LOW SKEW BUFFER

Description

The ICS671-06 is a low phase noise, high-speed

PLL-based, 8 output, low skew zero delay buffer.

Based on ICS’ proprietary low jitter Phase-Locked

Loop (PLL) techniques, the device provides eight low

skew outputs at speeds up to 133 MHz at 3.3 V. The

outputs can be generated from the PLL (for zero delay),

or directly from the input (for testing), and can be set to

tri-state mode or to stop at a low level. For normal

operation as a zero delay buffer, any output clock is

tied to the FBIN pin.

ICS manufactures the largest variety of clock

generators and buffers and is the largest clock supplier

in the world.

Features

Clock outputs from 10 to 133 MHz

Zero input-output delay

Eight low skew (<200 ps) outputs

Device-to-device skew <700 ps

Low jitter (<200 ps)

Full CMOS outputs with 25 mA output drive

capability at TTL levels

5 V tolerant FBIN and CLKIN pins

Tri-state mode for board-level testing

Advanced, low power, sub-micron CMOS process

Operating voltage of 3.3 V

Industrial temperature range available

Packaged in 16-pin SOIC and TSSOP packages

Available in Pb (lead) free package

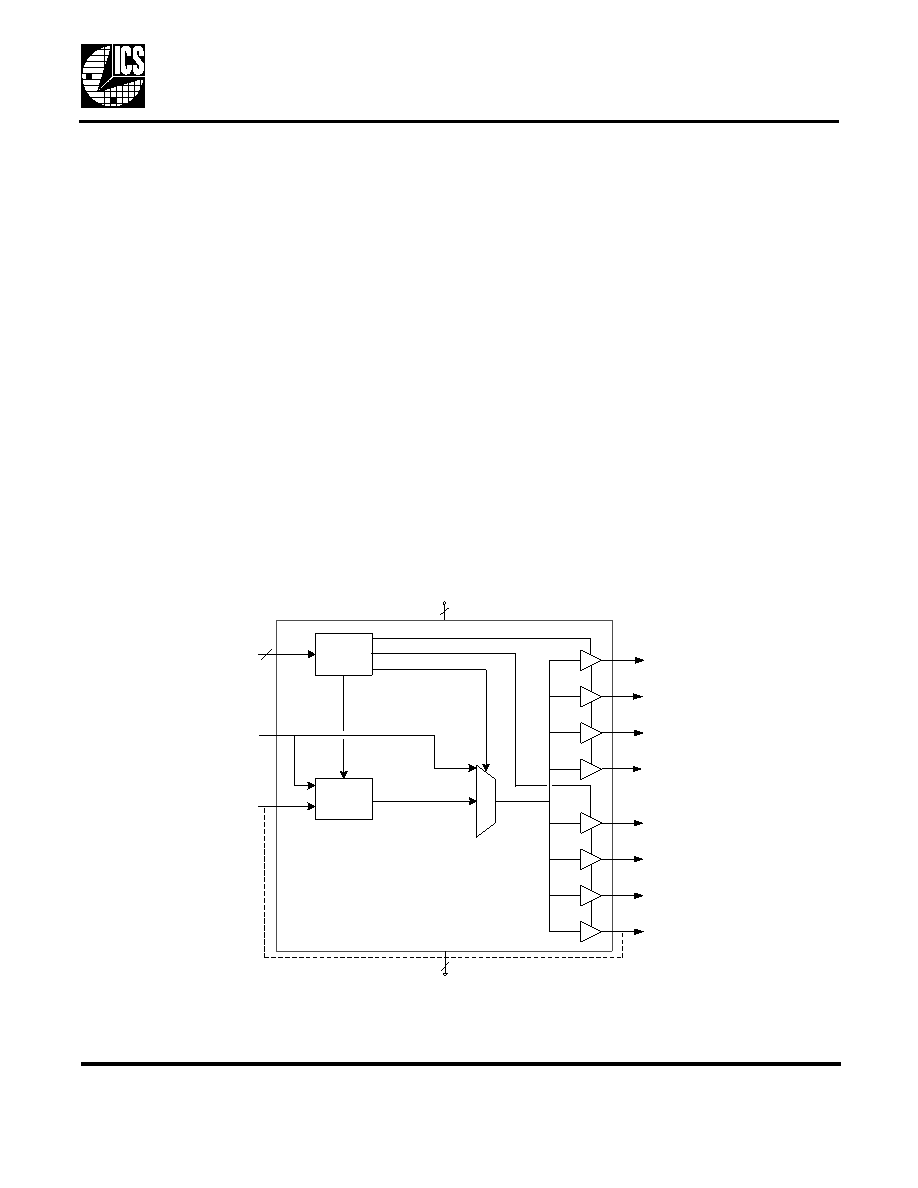

Block Diagram

CLKA4

CLKB1

CLKA3

CLKB2

CLKB3

CLKA2

CLKA1

CLKB4

CLKIN

Control

Logic

1

0

S2, S1

2

Clock

Synthesis

PLL

FBIN

Feedback is shown from CLKB4 for

illustration, but may come from any output.

VDD

2

GND

2

相关PDF资料 |

PDF描述 |

|---|---|

| ICS672M-02 | 672 SERIES, PLL BASED CLOCK DRIVER, 4 TRUE OUTPUT(S), 0 INVERTED OUTPUT(S), PDSO16 |

| ICS672M-02ILFT | 672 SERIES, PLL BASED CLOCK DRIVER, 4 TRUE OUTPUT(S), 0 INVERTED OUTPUT(S), PDSO16 |

| ICS672M-02T | 672 SERIES, PLL BASED CLOCK DRIVER, 4 TRUE OUTPUT(S), 0 INVERTED OUTPUT(S), PDSO16 |

| ICS672M-02ILFT | 672 SERIES, PLL BASED CLOCK DRIVER, 4 TRUE OUTPUT(S), 0 INVERTED OUTPUT(S), PDSO16 |

| ICS672M-01LFT | 672 SERIES, PLL BASED CLOCK DRIVER, 4 TRUE OUTPUT(S), 0 INVERTED OUTPUT(S), PDSO16 |

相关代理商/技术参数 |

参数描述 |

|---|---|

| ICS671G-15 | 功能描述:IC BUFFER ZD LOW SKEW 24-TSSOP RoHS:否 类别:集成电路 (IC) >> 时钟/计时 - 时钟发生器,PLL,频率合成器 系列:- 标准包装:1,000 系列:- 类型:时钟/频率合成器,扇出分配 PLL:- 输入:- 输出:- 电路数:- 比率 - 输入:输出:- 差分 - 输入:输出:- 频率 - 最大:- 除法器/乘法器:- 电源电压:- 工作温度:- 安装类型:表面贴装 封装/外壳:56-VFQFN 裸露焊盘 供应商设备封装:56-VFQFP-EP(8x8) 包装:带卷 (TR) 其它名称:844S012AKI-01LFT |

| ICS671G-15T | 功能描述:IC BUFFER ZD LOW SKEW 24-TSSOP RoHS:否 类别:集成电路 (IC) >> 时钟/计时 - 时钟发生器,PLL,频率合成器 系列:- 标准包装:2,000 系列:- 类型:PLL 时钟发生器 PLL:带旁路 输入:LVCMOS,LVPECL 输出:LVCMOS 电路数:1 比率 - 输入:输出:2:11 差分 - 输入:输出:是/无 频率 - 最大:240MHz 除法器/乘法器:是/无 电源电压:3.135 V ~ 3.465 V 工作温度:0°C ~ 70°C 安装类型:表面贴装 封装/外壳:32-LQFP 供应商设备封装:32-TQFP(7x7) 包装:带卷 (TR) |

| ICS671M-01 | 功能描述:IC BUFFER/MULT ZD 16-SOIC RoHS:否 类别:集成电路 (IC) >> 时钟/计时 - 时钟发生器,PLL,频率合成器 系列:- 产品变化通告:Product Discontinuation 04/May/2011 标准包装:96 系列:- 类型:时钟倍频器,零延迟缓冲器 PLL:带旁路 输入:LVTTL 输出:LVTTL 电路数:1 比率 - 输入:输出:1:8 差分 - 输入:输出:无/无 频率 - 最大:133.3MHz 除法器/乘法器:是/无 电源电压:3 V ~ 3.6 V 工作温度:0°C ~ 70°C 安装类型:表面贴装 封装/外壳:16-TSSOP(0.173",4.40mm 宽) 供应商设备封装:16-TSSOP 包装:管件 其它名称:23S08-5HPGG |

| ICS671M-01LF | 功能描述:IC BUFFER/MULT ZD 16-SOIC RoHS:是 类别:集成电路 (IC) >> 时钟/计时 - 时钟发生器,PLL,频率合成器 系列:- 标准包装:1,000 系列:- 类型:时钟/频率合成器,扇出分配 PLL:- 输入:- 输出:- 电路数:- 比率 - 输入:输出:- 差分 - 输入:输出:- 频率 - 最大:- 除法器/乘法器:- 电源电压:- 工作温度:- 安装类型:表面贴装 封装/外壳:56-VFQFN 裸露焊盘 供应商设备封装:56-VFQFP-EP(8x8) 包装:带卷 (TR) 其它名称:844S012AKI-01LFT |

| ICS671M-01LFT | 功能描述:IC BUFFER/MULT ZD 16-SOIC RoHS:是 类别:集成电路 (IC) >> 时钟/计时 - 时钟发生器,PLL,频率合成器 系列:- 标准包装:2,000 系列:- 类型:PLL 时钟发生器 PLL:带旁路 输入:LVCMOS,LVPECL 输出:LVCMOS 电路数:1 比率 - 输入:输出:2:11 差分 - 输入:输出:是/无 频率 - 最大:240MHz 除法器/乘法器:是/无 电源电压:3.135 V ~ 3.465 V 工作温度:0°C ~ 70°C 安装类型:表面贴装 封装/外壳:32-LQFP 供应商设备封装:32-TQFP(7x7) 包装:带卷 (TR) |

发布紧急采购,3分钟左右您将得到回复。