- 您现在的位置:买卖IC网 > PDF目录65531 > ICS671M-05I (INTEGRATED DEVICE TECHNOLOGY INC) PLL BASED CLOCK DRIVER, 8 TRUE OUTPUT(S), 0 INVERTED OUTPUT(S), PDSO16 PDF资料下载

参数资料

| 型号: | ICS671M-05I |

| 厂商: | INTEGRATED DEVICE TECHNOLOGY INC |

| 元件分类: | 时钟及定时 |

| 英文描述: | PLL BASED CLOCK DRIVER, 8 TRUE OUTPUT(S), 0 INVERTED OUTPUT(S), PDSO16 |

| 封装: | 0.150 INCH, SOIC-16 |

| 文件页数: | 4/7页 |

| 文件大小: | 176K |

| 代理商: | ICS671M-05I |

3.3 VOLT ZERO DELAY, LOW SKEW BUFFER

MDS 671-05 F

4

Revision 031004

Integrated Circuit Systems l 525 Race Street, San Jose, CA 95126 l tel (408) 297-1201 l

www.icst.com

ICS671-05

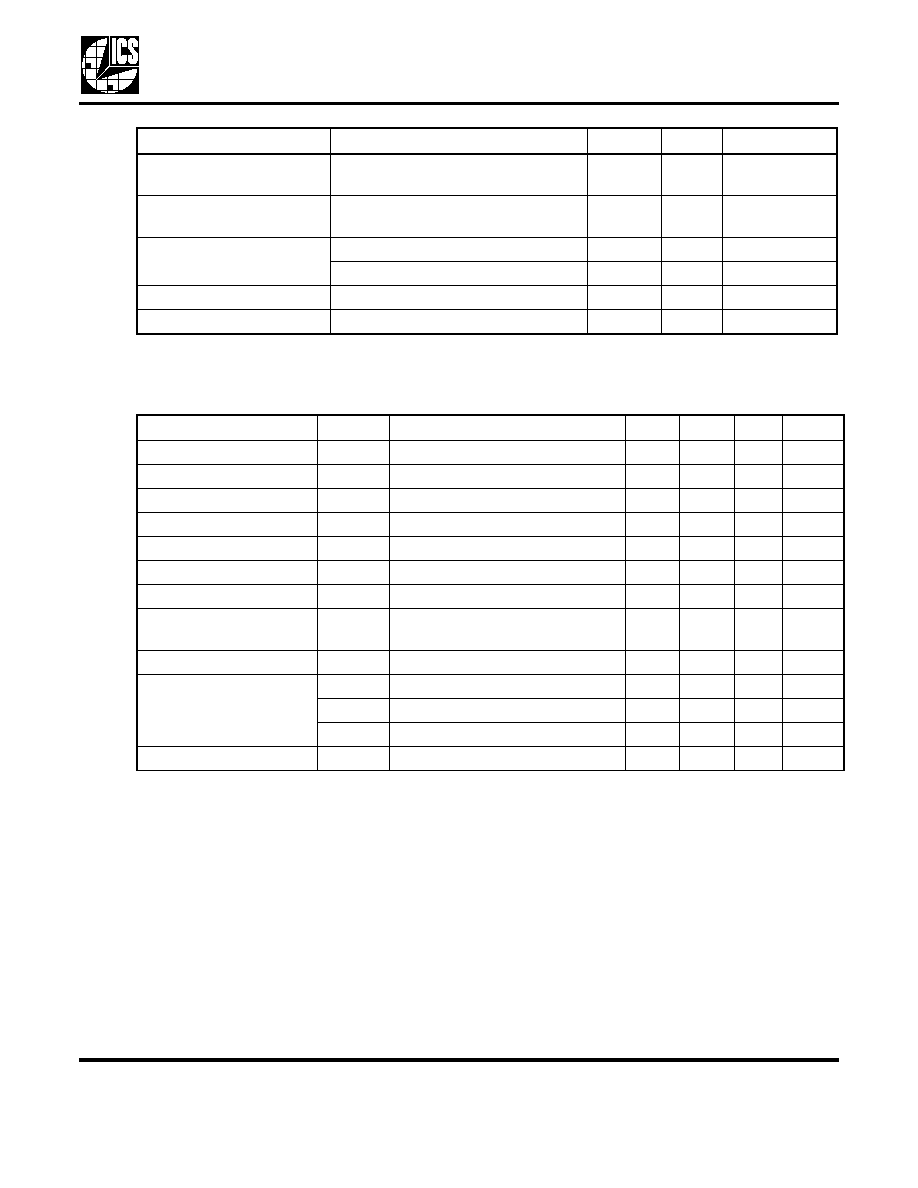

AC Electrical Characteristics

VDD = 3.3 V ±10%, Ambient Temperature -40 to +85

°C, CLOAD at CLK = 15 pF, unless stated otherwise

Note 1: With CLKIN = 100 MHz, FBIN to CLKA4, all outputs at 100 MHz

Note 2:When there is no clock signal present at CLKIN, the device will enter power-down mode. The PLL

is stopped and the outputs are tri-state.

Note 3: Withh VDD at a steady rate and valid clocks at CLKIN and FBIN.

Output High Voltage,

CMOS level

VOH

IOH = -8 mA

VDD-0.4

V

Operating Supply Current

IDD

No Load, S2 = 1, S1 = 1,

Note 1

25

mA

Power Down Supply

Current

IDDPD

CLKIN = 0, S2 = 0, S1 = 1

12

A

CLKIN = 0, Note 2

12

A

Short Circuit Current

IOS

Each output

±50

mA

Input Capacitance

CIN

S2, S1, FBIN

5

pF

Parameter

Symbol

Conditions

Min.

Typ. Max. Units

Input Clock Frequency

fIN

See table on page 2

10

133

MHz

Output Clock Frequency

See table on page 2

10

133

MHz

Output Rise Time

tOR

0.8 to 2.0V, CL=30 pF

1.5

ns

Output Fall Time

tOF

2.0 to 0.8V, CL=30 pF

1.25

ns

Output Clock Duty Cycle

tDC

measured at VDD/2

45

50

55

%

Device to Device Skew

rising edges at VDD/2, Note 3

700

ps

Output to Output Skew

rising edges at VDD/2, Note 3

200

ps

Input to Output Skew

rising edges at VDD/2, FBIN to

CLKA4, S1 = 1, S0 = 1, Note 1

±250

ps

Maximum Absolute JItter

CL = 15 pF, measured at 66.67M

130

ps

Cycle to Cycle Jitter

CL = 30 pF, measured at 66.67M

200

ps

CL = 15 pF, measured at 66.67M

200

CL = 15 pF, measured at 133.33M

100

PLL Lock Time

Note 3

1.0

ms

Parameter

Symbol

Conditions

Min.

Typ.

Max.

Units

相关PDF资料 |

PDF描述 |

|---|---|

| ICS671M-05ILF | PLL BASED CLOCK DRIVER, 8 TRUE OUTPUT(S), 0 INVERTED OUTPUT(S), PDSO16 |

| ICS671G-15 | 671 SERIES, PLL BASED CLOCK DRIVER, 6 TRUE OUTPUT(S), 0 INVERTED OUTPUT(S), PDSO24 |

| ICS671M-02ILF | PLL BASED CLOCK DRIVER, 8 TRUE OUTPUT(S), 0 INVERTED OUTPUT(S), PDSO16 |

| ICS671M-02I | PLL BASED CLOCK DRIVER, 8 TRUE OUTPUT(S), 0 INVERTED OUTPUT(S), PDSO16 |

| ICS671M-02ILF | PLL BASED CLOCK DRIVER, 8 TRUE OUTPUT(S), 0 INVERTED OUTPUT(S), PDSO16 |

相关代理商/技术参数 |

参数描述 |

|---|---|

| ICS671M-06I | 制造商:ICS 制造商全称:ICS 功能描述:3.3 VOLT ZERO DELAY, LOW SKEW BUFFER |

| ICS671M-06ILF | 制造商:ICS 制造商全称:ICS 功能描述:3.3 VOLT ZERO DELAY, LOW SKEW BUFFER |

| ICS671M-06ILFT | 制造商:ICS 制造商全称:ICS 功能描述:3.3 VOLT ZERO DELAY, LOW SKEW BUFFER |

| ICS671M-06IT | 制造商:ICS 制造商全称:ICS 功能描述:3.3 VOLT ZERO DELAY, LOW SKEW BUFFER |

| ICS672-01 | 制造商:ICS 制造商全称:ICS 功能描述:QuadraClock⑩ Quadrature Delay Buffer |

发布紧急采购,3分钟左右您将得到回复。