- 您现在的位置:买卖IC网 > PDF目录9150 > ICS673M-01ILF (IDT, Integrated Device Technology Inc)IC PLL BUILDING BLOCK 16SOIC PDF资料下载

参数资料

| 型号: | ICS673M-01ILF |

| 厂商: | IDT, Integrated Device Technology Inc |

| 文件页数: | 2/8页 |

| 文件大小: | 0K |

| 描述: | IC PLL BUILDING BLOCK 16SOIC |

| 标准包装: | 48 |

| 类型: | 锁相环路(PLL) |

| PLL: | 是 |

| 输入: | 时钟 |

| 输出: | 时钟 |

| 电路数: | 1 |

| 比率 - 输入:输出: | 1:2 |

| 差分 - 输入:输出: | 无/无 |

| 频率 - 最大: | 120MHz |

| 除法器/乘法器: | 是/无 |

| 电源电压: | 3.13 V ~ 5.5 V |

| 工作温度: | -40°C ~ 85°C |

| 安装类型: | 表面贴装 |

| 封装/外壳: | 16-SOIC(0.154",3.90mm 宽) |

| 供应商设备封装: | 16-SOIC |

| 包装: | 管件 |

| 其它名称: | 673M-01ILF ICS673M-01ILF-ND |

PLL BUILDING BLOCK

MDS 673-01 L

2

Revision 051310

www.idt.com

ICS673-01

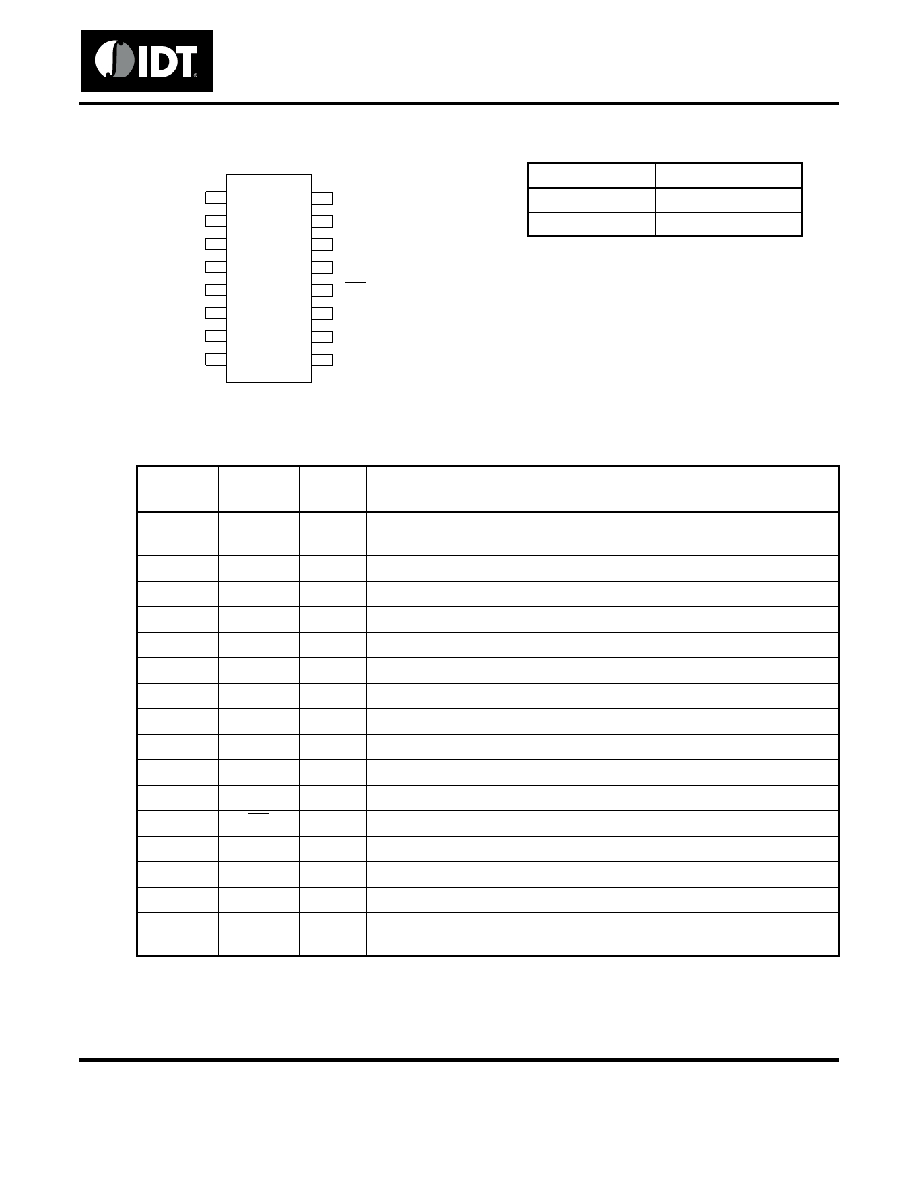

Pin Assignment

VCO Predivide Select Table

0 = connect pin directly to ground

1 = connect pin directly to VDD

Pin Descriptions

12

1

11

2

10

FB IN

RE F IN

3

9

VD D

4

VD D

NC

5

GN D

6

CL K 1

7

GN D

8

GN D

CL K 2

PD

SEL

CH G P

OE

VC O IN

CA P

16

15

14

13

16 p in narro w (150 m il) S O IC

SEL

VCO Predivide

04

11

Pin

Number

Pin

Name

Pin

Type

Pin Description

1

FBIN

Input

Feedback clock input. Connect the feedback clock to this pin. Falling

edge triggered.

2

VDD

Power

Connect to +3.3 V or +5 V and to VDD on pin 3.

3

VDD

Power

Connect to VDD on pin 2.

4

GND

Power

Connect to ground.

5

GND

Power

Connect to ground.

6

GND

Power

Connect to ground.

7

CHGP

Output

Charge pump output. Connect to VCOIN under normal operation.

8

VCOIN

Input

Input to internal VCO.

9

CAP

Input

Loop filter return.

10

OE

Input

Output enable. Active when high. Tri-states both outputs when low.

11

SEL

Input

Select pin for VCO predivide to feedback divider per table above.

12

PD

Input

Power down. Turns off entire chip when pin is low. Outputs stop low.

13

CLK2

Output

Clock output 2. Low skew divide by two version of CLK1.

14

CLK1

Output

Clock output 1.

15

NC

-

No connect. Nothing is connected internally to this pin.

16

REFIN

Input

Reference input. Connect reference clock to this pin. Falling edge is

triggered.

相关PDF资料 |

PDF描述 |

|---|---|

| V300A5H300BG3 | CONVERTER MOD DC/DC 5V 300W |

| ICS87332AMI-01LF | IC CLK GEN /2 ECL/LVPECL 8-SOIC |

| V300A5H300BG2 | CONVERTER MOD DC/DC 5V 300W |

| V300A5H300BF3 | CONVERTER MOD DC/DC 5V 300W |

| V300A5H300BF2 | CONVERTER MOD DC/DC 5V 300W |

相关代理商/技术参数 |

参数描述 |

|---|---|

| ICS673M-01ILFT | 功能描述:IC PLL BUILDING BLOCK 16-SOIC RoHS:是 类别:集成电路 (IC) >> 时钟/计时 - 时钟发生器,PLL,频率合成器 系列:- 标准包装:2,000 系列:- 类型:PLL 时钟发生器 PLL:带旁路 输入:LVCMOS,LVPECL 输出:LVCMOS 电路数:1 比率 - 输入:输出:2:11 差分 - 输入:输出:是/无 频率 - 最大:240MHz 除法器/乘法器:是/无 电源电压:3.135 V ~ 3.465 V 工作温度:0°C ~ 70°C 安装类型:表面贴装 封装/外壳:32-LQFP 供应商设备封装:32-TQFP(7x7) 包装:带卷 (TR) |

| ICS673M-01IT | 功能描述:IC PLL BUILDING BLOCK 16-SOIC RoHS:否 类别:集成电路 (IC) >> 时钟/计时 - 时钟发生器,PLL,频率合成器 系列:- 产品变化通告:Product Discontinuation 04/May/2011 标准包装:96 系列:- 类型:时钟倍频器,零延迟缓冲器 PLL:带旁路 输入:LVTTL 输出:LVTTL 电路数:1 比率 - 输入:输出:1:8 差分 - 输入:输出:无/无 频率 - 最大:133.3MHz 除法器/乘法器:是/无 电源电压:3 V ~ 3.6 V 工作温度:0°C ~ 70°C 安装类型:表面贴装 封装/外壳:16-TSSOP(0.173",4.40mm 宽) 供应商设备封装:16-TSSOP 包装:管件 其它名称:23S08-5HPGG |

| ICS673M-01LF | 功能描述:IC PLL BUILDING BLOCK 16-SOIC RoHS:是 类别:集成电路 (IC) >> 时钟/计时 - 时钟发生器,PLL,频率合成器 系列:- 标准包装:2,000 系列:- 类型:PLL 频率合成器 PLL:是 输入:晶体 输出:时钟 电路数:1 比率 - 输入:输出:1:1 差分 - 输入:输出:无/无 频率 - 最大:1GHz 除法器/乘法器:是/无 电源电压:4.5 V ~ 5.5 V 工作温度:-20°C ~ 85°C 安装类型:表面贴装 封装/外壳:16-LSSOP(0.175",4.40mm 宽) 供应商设备封装:16-SSOP 包装:带卷 (TR) 其它名称:NJW1504V-TE1-NDNJW1504V-TE1TR |

| ICS673M-01LFT | 功能描述:IC PLL BUILDING BLOCK 16-SOIC RoHS:是 类别:集成电路 (IC) >> 时钟/计时 - 时钟发生器,PLL,频率合成器 系列:- 标准包装:2,000 系列:- 类型:PLL 时钟发生器 PLL:带旁路 输入:LVCMOS,LVPECL 输出:LVCMOS 电路数:1 比率 - 输入:输出:2:11 差分 - 输入:输出:是/无 频率 - 最大:240MHz 除法器/乘法器:是/无 电源电压:3.135 V ~ 3.465 V 工作温度:0°C ~ 70°C 安装类型:表面贴装 封装/外壳:32-LQFP 供应商设备封装:32-TQFP(7x7) 包装:带卷 (TR) |

| ICS673M-01T | 功能描述:IC PLL BUILDING BLOCK 16-SOIC RoHS:否 类别:集成电路 (IC) >> 时钟/计时 - 时钟发生器,PLL,频率合成器 系列:- 产品变化通告:Product Discontinuation 04/May/2011 标准包装:96 系列:- 类型:时钟倍频器,零延迟缓冲器 PLL:带旁路 输入:LVTTL 输出:LVTTL 电路数:1 比率 - 输入:输出:1:8 差分 - 输入:输出:无/无 频率 - 最大:133.3MHz 除法器/乘法器:是/无 电源电压:3 V ~ 3.6 V 工作温度:0°C ~ 70°C 安装类型:表面贴装 封装/外壳:16-TSSOP(0.173",4.40mm 宽) 供应商设备封装:16-TSSOP 包装:管件 其它名称:23S08-5HPGG |

发布紧急采购,3分钟左右您将得到回复。