- 您现在的位置:买卖IC网 > PDF目录65533 > ICS8432AY-101T (INTEGRATED DEVICE TECHNOLOGY INC) PLL BASED CLOCK DRIVER, 2 TRUE OUTPUT(S), 0 INVERTED OUTPUT(S), PQFP32 PDF资料下载

参数资料

| 型号: | ICS8432AY-101T |

| 厂商: | INTEGRATED DEVICE TECHNOLOGY INC |

| 元件分类: | 时钟及定时 |

| 英文描述: | PLL BASED CLOCK DRIVER, 2 TRUE OUTPUT(S), 0 INVERTED OUTPUT(S), PQFP32 |

| 封装: | 7 X 7 MM, 1.40 MM HEIGHT, MS-026, LQFP-32 |

| 文件页数: | 3/10页 |

| 文件大小: | 114K |

| 代理商: | ICS8432AY-101T |

8432AY-101

www.icst.com/products/hiperclocks.html

REV. B JULY 30, 2001

2

PRELIMINARY

Integrated

Circuit

Systems, Inc.

ICS8432-101

700MHZ, LOW PHASE NOISE,

LVPECL FREQUENCY SYNTHESIZER

FUNCTIONAL DESCRIPTION

NOTE: The functional description that follows describes operation using a 25MHz clock input. Valid PLL loop divider values

for different input frequencies are defined in the Input Frequency Characteristics, Table 5, NOTE 1.

The ICS8432-101 features a fully integrated PLL and therefore requires no external component for setting the loop bandwidth.

A differential clock input is used as the input to the ICS8432-101. This input is fed into the phase detector. A

25MHz clock input provides a 25MHz phase detector reference frequency. The VCO of the PLL operates over a range of

250MHz to 700MHz. The output of the loop divider is also applied to the phase detector.

The phase detector and the loop filter divider force the VCO output frequency to be M times the reference frequency by

adjusting the VCO control voltage. Note that for some values of M (either too high or too low) the PLL will not achieve lock.

The output of the VCO is scaled by a divider prior to being sent to each of the LVPECL output buffers. The divider provides

a 50% output duty cycle.

The programmable features of the ICS8432-101 support two input modes and programmable PLL loop divider and output

divider. The two input operational modes are parallel and serial.

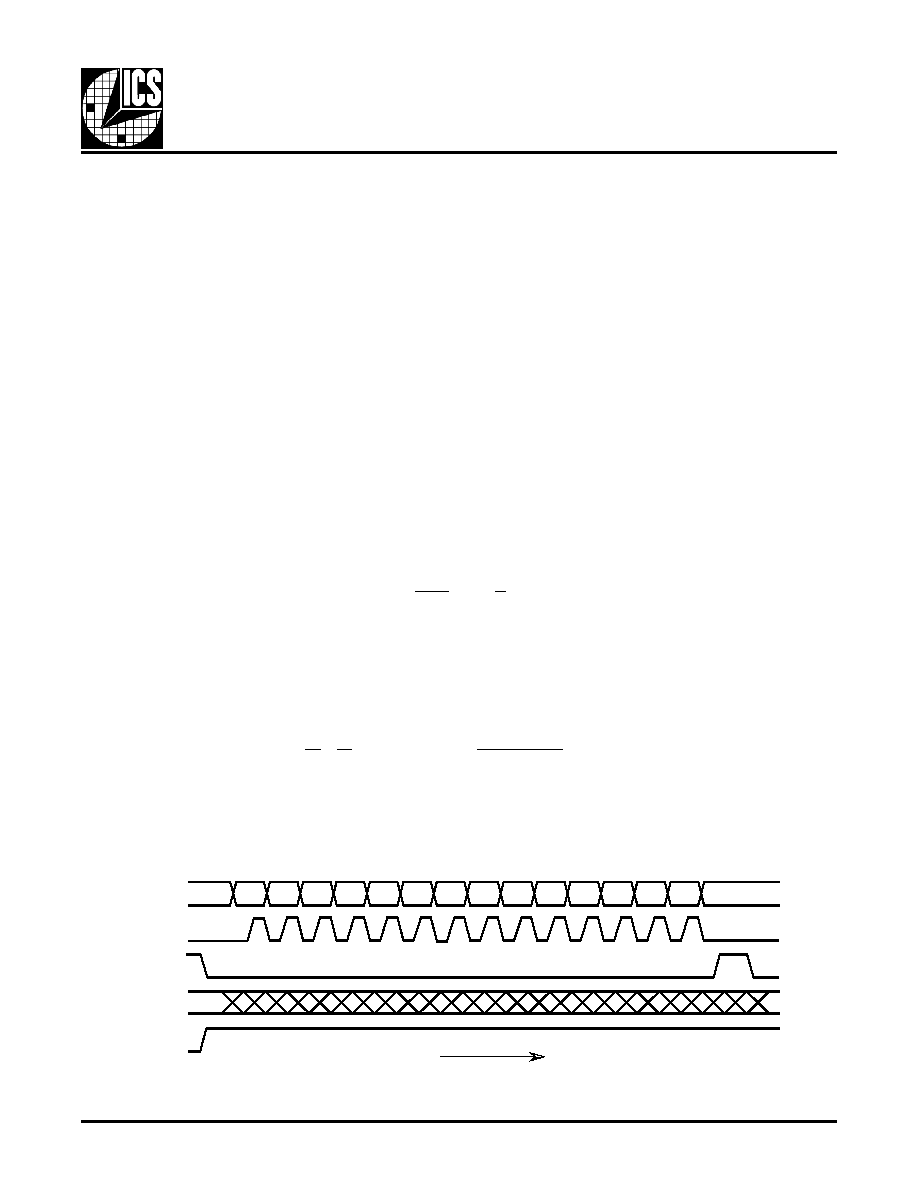

Figure 1 shows the timing diagram for each mode. In parallel

mode the nP_LOAD input is initially LOW. The data on inputs M0 through M8 and N0 and N1 is passed directly to the ripple

counter. On the LOW-to-HIGH transition of the nP_LOAD input the data is latched and the ripple counter remains loaded until

the next LOW transition on nP_LOAD or until a serial event occurs. As a result the M and N bits can be hardwired to set the

ripple counter to a specific default state that will automatically occur during power-up. The TEST output is LOW when operat-

ing in the parallel input mode. The relationship between the VCO frequency, the input frequency and the loop divider is defined

as follows:

The M count and the required values of M0 through M8 are shown in Table 3B, Programmable VCO Frequency Function.

Valid M values for which the PLL will achieve lock are defined as 10

≤ M ≤ 28. The frequency out is defined as follows:

Serial operation occurs when nP_LOAD is HIGH and S_LOAD is LOW. The shift register is loaded by sampling the

S_DATA bits with the rising edge of S_CLOCK. The contents of the shift register are loaded into the ripple counter when

S_LOAD transitions from LOW-to-HIGH. The ripple counter divide values are latched on the HIGH-to-LOW transition of

S_LOAD. If S_LOAD is held HIGH data at the S_DATA input is passed directly to the ripple counter on each rising edge of

S_CLOCK. The serial mode can be used to program the M and N bits and test bits T1 and T0. The internal registers T0 and

T1 determine the state of the TEST output as follows:

fVCO = fIN x M

T1

T0

TEST Output

0

LOW

0

1

S_Data

1

0

Output of M divider

1

CMOS Fout

FIGURE 1. PARALLEL & SERIAL LOAD OPERATIONS

S_DATA

S_CLOCK

S_LOAD

M0:M8, N0:N2

nP_LOAD

fOUT = fVCO = fIN x M

N

Time

T1

T0

*NULL

N 1

N 0

M8

M7

M6

M5

M4

M3

M2

M1

M0

*NOTE: The NULL timing slot must be observed.

相关PDF资料 |

PDF描述 |

|---|---|

| ICS8432BY-21 | 500 MHz, OTHER CLOCK GENERATOR, PQFP32 |

| ICS8432BY-21T | 500 MHz, OTHER CLOCK GENERATOR, PQFP32 |

| ICS8432BY-21 | 500 MHz, OTHER CLOCK GENERATOR, PQFP32 |

| ICS8516DYT | LOW SKEW CLOCK DRIVER, 16 TRUE OUTPUT(S), 0 INVERTED OUTPUT(S), PQFP48 |

| ICS8516DYLFT | LOW SKEW CLOCK DRIVER, 16 TRUE OUTPUT(S), 0 INVERTED OUTPUT(S), PQFP48 |

相关代理商/技术参数 |

参数描述 |

|---|---|

| ICS8432BI51 | 制造商:IDT 制造商全称:Integrated Device Technology 功能描述:700MHZ, CYRSTAL-TO-3.3V DIFFERENTIAL LVPECL FREQUENCY SYNTHESIZER |

| ICS8432BI-51L | 制造商:IDT 制造商全称:Integrated Device Technology 功能描述:700MHZ, CYRSTAL-TO-3.3V DIFFERENTIAL LVPECL FREQUENCY SYNTHESIZER |

| ICS8432BK-51 | 制造商:ICS 制造商全称:ICS 功能描述:700MHZ, CRYSTAL-TO-3.3V DIFFERENTIAL LVPECL FREQUENCY SYNTHESIZER |

| ICS8432BK-51LF | 功能描述:IC SYNTHESIZER LVPECL 32-VFQFPN RoHS:是 类别:集成电路 (IC) >> 时钟/计时 - 时钟发生器,PLL,频率合成器 系列:HiPerClockS™ 标准包装:1,000 系列:- 类型:时钟/频率合成器,扇出分配 PLL:- 输入:- 输出:- 电路数:- 比率 - 输入:输出:- 差分 - 输入:输出:- 频率 - 最大:- 除法器/乘法器:- 电源电压:- 工作温度:- 安装类型:表面贴装 封装/外壳:56-VFQFN 裸露焊盘 供应商设备封装:56-VFQFP-EP(8x8) 包装:带卷 (TR) 其它名称:844S012AKI-01LFT |

| ICS8432BK-51LFT | 功能描述:IC SYNTHESIZER LVPECL 32-VFQFPN RoHS:是 类别:集成电路 (IC) >> 时钟/计时 - 时钟发生器,PLL,频率合成器 系列:HiPerClockS™ 标准包装:1,000 系列:- 类型:时钟/频率合成器,扇出分配 PLL:- 输入:- 输出:- 电路数:- 比率 - 输入:输出:- 差分 - 输入:输出:- 频率 - 最大:- 除法器/乘法器:- 电源电压:- 工作温度:- 安装类型:表面贴装 封装/外壳:56-VFQFN 裸露焊盘 供应商设备封装:56-VFQFP-EP(8x8) 包装:带卷 (TR) 其它名称:844S012AKI-01LFT |

发布紧急采购,3分钟左右您将得到回复。