- 您现在的位置:买卖IC网 > PDF目录67692 > ICS84330CYIT (INTEGRATED DEVICE TECHNOLOGY INC) 720 MHz, OTHER CLOCK GENERATOR, PQFP32 PDF资料下载

参数资料

| 型号: | ICS84330CYIT |

| 厂商: | INTEGRATED DEVICE TECHNOLOGY INC |

| 元件分类: | 时钟产生/分配 |

| 英文描述: | 720 MHz, OTHER CLOCK GENERATOR, PQFP32 |

| 封装: | 7 X 7 MM, 1.40 MM HEIGHT, MS-026BBA, LQFP-32 |

| 文件页数: | 12/20页 |

| 文件大小: | 503K |

| 代理商: | ICS84330CYIT |

84330CVI

www.icst.com/products/hiperclocks.html

REV. A DECEMBER 7, 2004

2

Integrated

Circuit

Systems, Inc.

ICS84330CI

720MHZ, LOW JITTER, CRYSTAL-TO-3.3V

DIFFERENTIAL LVPECL FREQUENCY SYNTHESIZER

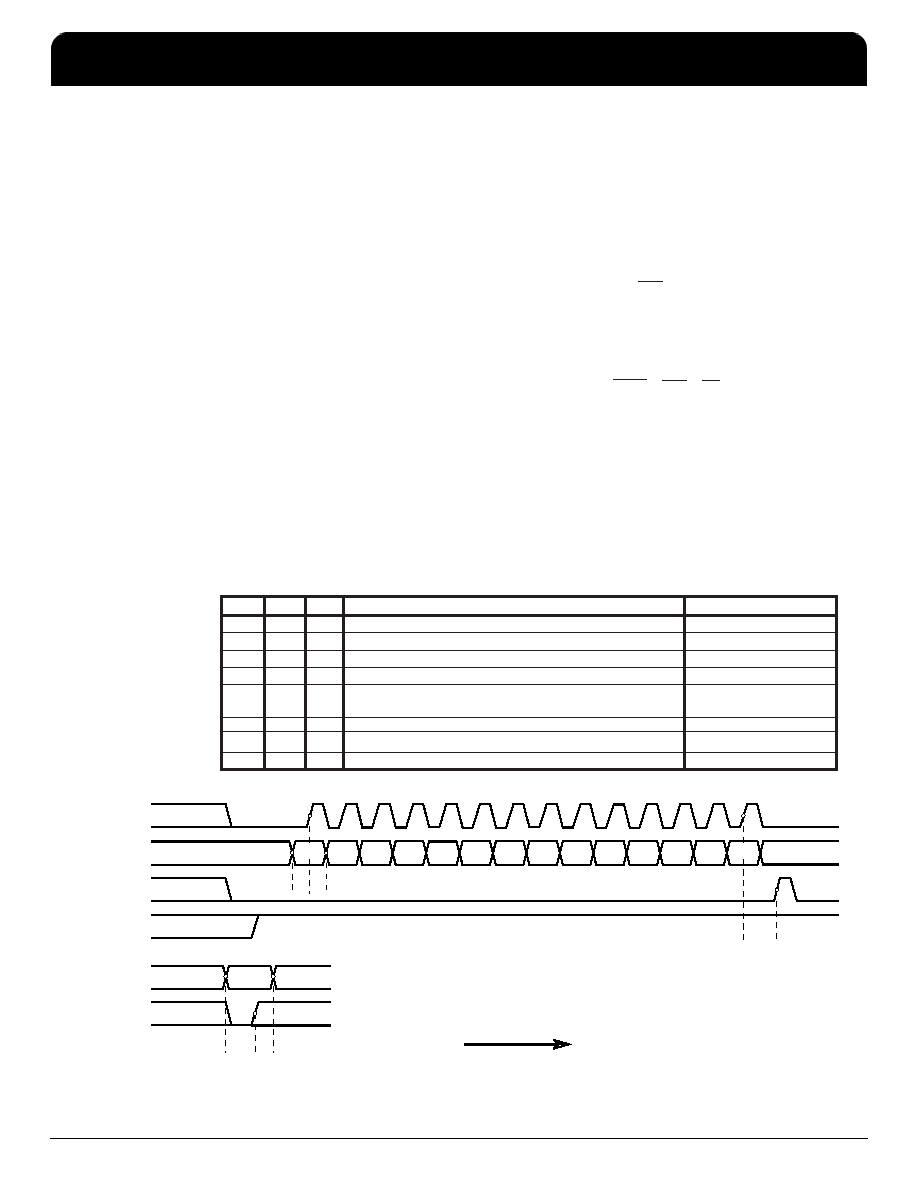

N0 through N1 is passed directly to the M divider and N output

divider. On the LOW-to-HIGH transition of the nP_LOAD input,

the data is latched and the M divider remains loaded until the

next LOW transition on nP_LOAD or until a serial event occurs.

The TEST output is Mode 000 (shift register out) when operat-

ing in the parallel input mode.The relationship between the VCO

frequency, the crystal frequency and the M divider is defined as

follows:

The M value and the required values of M0 through M8 are

shown in Table 3B, Programmable VCO Frequency Function

Table. Valid M values for which the PLL will achieve lock are

defined as 125

≤ M ≤ 360. The frequency out is defined as

follows:

Serial operation occurs when nP_LOAD is HIGH and S_LOAD

is LOW. The shift register is loaded by sampling the S_DATA

bits with the rising edge of S_CLOCK. The contents of the

shift register are loaded into the M divider when S_LOAD tran-

sitions from LOW-to-HIGH. The M divide and N output divide

values are latched on the HIGH-to-LOW transition of S_LOAD.

If S_LOAD is held HIGH, data at the S_DATA input is passed

directly to the M divider on each rising edge of S_CLOCK.

The serial mode can be used to program the M and N bits and

test bits T2:T0. The internal registers T2:T0 determine the state

of the TEST output as follows in the table below:

FUNCTIONAL DESCRIPTION

NOTE: The functional description that follows describes op-

eration using a 16MHz crystal. Valid PLL loop divider values

for different crystal or input frequencies are defined in the In-

put Frequency Characteristics, Table 6, NOTE 1.

The ICS84330CI features a fully integrated PLL and there-

fore requires no external components for setting the loop band-

width. A quartz crystal is used as the input to the on-chip

oscillator. The output of the oscillator is divided by 16 prior to

the phase detector. With a 16MHz crystal this provides a 1MHz

reference frequency. The VCO of the PLL operates over a

range of 250MHz to 720MHz. The output of the M divider is

also applied to the phase detector.

The phase detector and the M divider force the VCO output fre-

quency to be 2M times the reference frequency by adjusting the

VCO control voltage. Note that for some values of M (either too

high or too low), the PLL will not achieve lock. The output of the

VCO is scaled by a divider prior to being sent to each of the LVPECL

output buffers.The divider provides a 50% output duty cycle.

The programmable features of the ICS84330CI support two in-

put modes to program the M divider and N output divider. The

two input operational modes are parallel and serial.

Figure 1

shows the timing diagram for each mode. In parallel mode the

nP_LOAD input is LOW. The data on inputs M0 through M8 and

FIGURE 1. PARALLEL & SERIAL LOAD OPERATIONS

16

2M

fVCO =

fxtal x

N

fout =

fVCO

=

16

2M

fxtal x

N

T2

T1

T0

TEST Output

0

Shift Register Out

00

1

High

0

1

0

PLL Reference Xtal ÷ 16

0

1

(VCO ÷ M) /2 (non 50% Duty Cycle M divider)

1

0

fOUT

LVCMOS Output Frequency < 200MHz

1

0

1

Low

1

0

(S_CLOCK ÷ M) /2 (non 50% Duty Cycle M divider)

1

fOUT ÷ 4

fOUT

fOUT

S_CLOCK ÷ N divider

fOUT

Time

SERIAL LOADING

PARALLEL LOADING

M, N

t

S

t

H

t

S

t

H

t

S

T2

T1

T0

N 1

N 0

M8

M7

M6

M5

M4

M3

M2

M1

M0

S_CLOCK

S_DATA

S_LOAD

nP_LOAD

M0:M8, N0:N1

nP_LOAD

ICS84330CI

720MHZ, LOW JITTER, CRYSTAL-TO-3.3V DIFFERENTIAL LVPECL FREQUENCY SYNTHESIZER

TSD

IDT / ICS 720MHZ, LOW JITTER, CRYSTAL-TO-3.3V DIFFERENTIAL LVPECL FREQUENCY SYNTHESIZER

ICS84330CI

2

相关PDF资料 |

PDF描述 |

|---|---|

| ICS84330CY | 700 MHz, OTHER CLOCK GENERATOR, PQFP32 |

| ICS84330CYLNT | 700 MHz, OTHER CLOCK GENERATOR, PQFP32 |

| ICS84334AYT | 700 MHz, OTHER CLOCK GENERATOR, PQFP48 |

| ICS843AG-106LF | 106.25 MHz, OTHER CLOCK GENERATOR, PDSO8 |

| ICS843AG-75LF | 75 MHz, OTHER CLOCK GENERATOR, PDSO8 |

相关代理商/技术参数 |

参数描述 |

|---|---|

| ICS84330CYLN | 功能描述:IC SYNTHESIZER GP LVPECL 32-LQFP RoHS:否 类别:集成电路 (IC) >> 时钟/计时 - 时钟发生器,PLL,频率合成器 系列:HiPerClockS™ 标准包装:2,000 系列:- 类型:PLL 频率合成器 PLL:是 输入:晶体 输出:时钟 电路数:1 比率 - 输入:输出:1:1 差分 - 输入:输出:无/无 频率 - 最大:1GHz 除法器/乘法器:是/无 电源电压:4.5 V ~ 5.5 V 工作温度:-20°C ~ 85°C 安装类型:表面贴装 封装/外壳:16-LSSOP(0.175",4.40mm 宽) 供应商设备封装:16-SSOP 包装:带卷 (TR) 其它名称:NJW1504V-TE1-NDNJW1504V-TE1TR |

| ICS84330CYLNT | 功能描述:IC SYNTHESIZER 700MHZ 32-LQFP RoHS:是 类别:集成电路 (IC) >> 时钟/计时 - 时钟发生器,PLL,频率合成器 系列:HiPerClockS™ 标准包装:1,000 系列:- 类型:时钟/频率合成器,扇出分配 PLL:- 输入:- 输出:- 电路数:- 比率 - 输入:输出:- 差分 - 输入:输出:- 频率 - 最大:- 除法器/乘法器:- 电源电压:- 工作温度:- 安装类型:表面贴装 封装/外壳:56-VFQFN 裸露焊盘 供应商设备封装:56-VFQFP-EP(8x8) 包装:带卷 (TR) 其它名称:844S012AKI-01LFT |

| ICS84330CYT | 制造商:Integrated Device Technology Inc 功能描述:IC SYNTHESIZER 700MHZ 28-PLCC |

| ICS843312AKILF | 功能描述:IC CLK GENERATOR 32VFQFN RoHS:是 类别:集成电路 (IC) >> 时钟/计时 - 时钟发生器,PLL,频率合成器 系列:- 标准包装:27 系列:Precision Edge® 类型:频率合成器 PLL:是 输入:PECL,晶体 输出:PECL 电路数:1 比率 - 输入:输出:1:1 差分 - 输入:输出:无/是 频率 - 最大:800MHz 除法器/乘法器:是/无 电源电压:3.135 V ~ 5.25 V 工作温度:0°C ~ 85°C 安装类型:表面贴装 封装/外壳:28-SOIC(0.295",7.50mm 宽) 供应商设备封装:28-SOIC 包装:管件 |

| ICS843312AKILFT | 功能描述:IC CLK GENERATOR 32VFQFN RoHS:是 类别:集成电路 (IC) >> 时钟/计时 - 时钟发生器,PLL,频率合成器 系列:- 标准包装:1,000 系列:- 类型:时钟/频率合成器,扇出分配 PLL:- 输入:- 输出:- 电路数:- 比率 - 输入:输出:- 差分 - 输入:输出:- 频率 - 最大:- 除法器/乘法器:- 电源电压:- 工作温度:- 安装类型:表面贴装 封装/外壳:56-VFQFN 裸露焊盘 供应商设备封装:56-VFQFP-EP(8x8) 包装:带卷 (TR) 其它名称:844S012AKI-01LFT |

发布紧急采购,3分钟左右您将得到回复。