- 您现在的位置:买卖IC网 > PDF目录67692 > ICS844002AGLF 226.66 MHz, OTHER CLOCK GENERATOR, PDSO20 PDF资料下载

参数资料

| 型号: | ICS844002AGLF |

| 元件分类: | 时钟产生/分配 |

| 英文描述: | 226.66 MHz, OTHER CLOCK GENERATOR, PDSO20 |

| 封装: | 6.50 X 4.40 MM, 0.92 MM HEIGHT, ROHS COMPLIANT, MO-153, TSSOP-20 |

| 文件页数: | 11/12页 |

| 文件大小: | 264K |

| 代理商: | ICS844002AGLF |

844002AG

www.icst.com/products/hiperclocks.html

REV. A MAY 18, 2006

8

Integrated

Circuit

Systems, Inc.

ICS844002

FEMTOCLOCKS CRYSTAL-TO-

LVDS FREQUENCY SYNTHESIZER

3.3V, 2.5V LVDS DRIVER TERMINATION

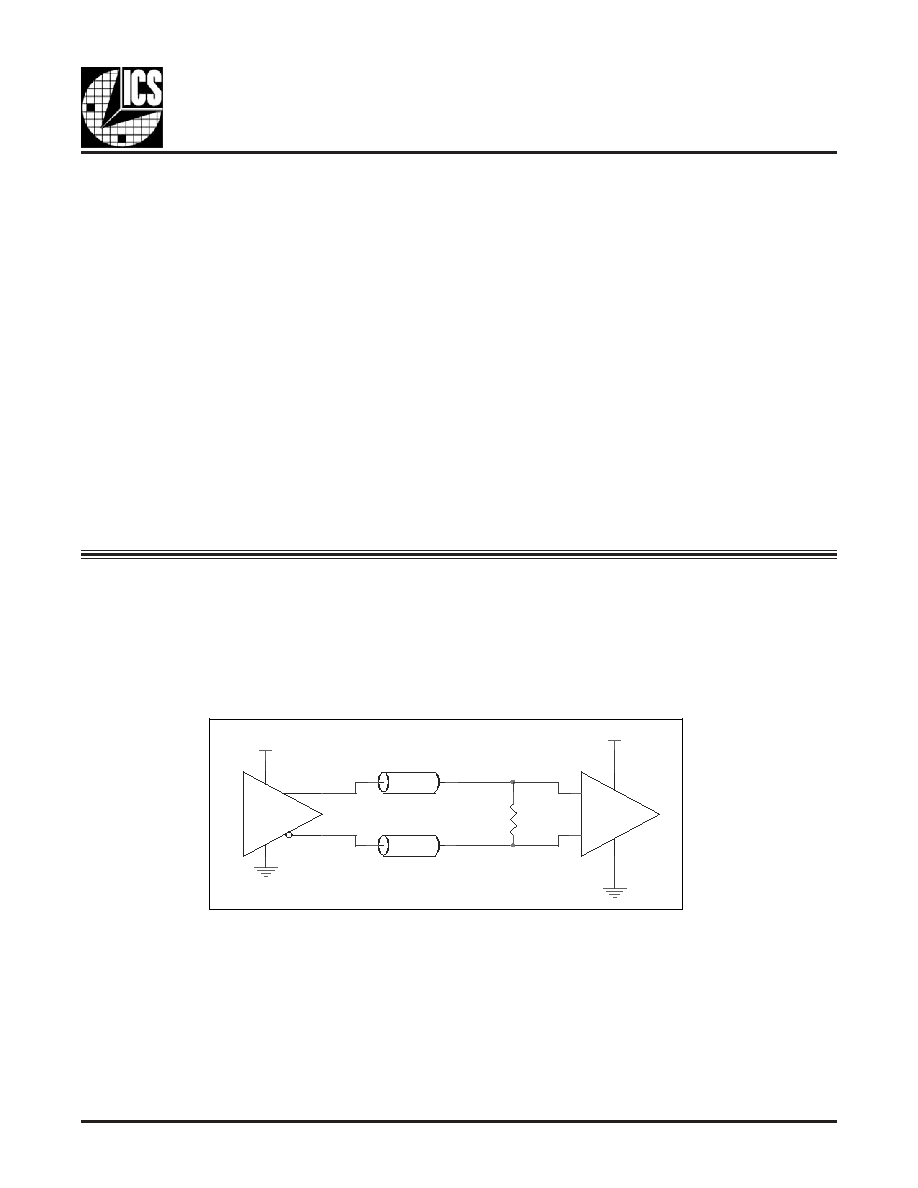

A general LVDS interface is shown in Figure 3. In a 100

Ω

differential transmission line environment, LVDS drivers

require a matched load termination of 100

Ω across near

FIGURE 3. TYPICAL LVDS DRIVER TERMINATION

the receiver input. For a multiple LVDS outputs buffer, if only

partial outputs are used, it is recommended to terminate the

un-used outputs.

2.5V or 3.3V

+

-

VDD

100 Ohm Differential Transmission Line

R1

100

LVDS_Driv er

INPUTS:

CRYSTAL INPUT:

For applications not requiring the use of the crystal oscillator

input, both XTAL_IN and XTAL_OUT can be left floating.

Though not required, but for additional protection, a 1k

Ω

resistor can be tied from XTAL_IN to ground.

REF_CLK INPUT:

For applications not requiring the use of the reference clock,

it can be left floating. Though not required, but for additional

protection, a 1k

Ω resistor can be tied from the REF_CLK to

ground.

LVCMOS CONTROL PINS:

All control pins have internal pull-ups or pull-downs; additional

resistance is not required but can be added for additional

protection. A 1k

Ω resistor can be used.

RECOMMENDATIONS FOR UNUSED INPUT AND OUTPUT PINS

OUTPUTS:

LVDS

All unused LVDS output pairs can be either left floating or

terminated with 100

Ω across. If they are left floating, we

recommend that there is no trace attached.

相关PDF资料 |

PDF描述 |

|---|---|

| ICS844003AGILFT | 700 MHz, OTHER CLOCK GENERATOR, PDSO24 |

| ICS844003AGLFT | 700 MHz, OTHER CLOCK GENERATOR, PDSO24 |

| ICS844003BGI-01LFT | 680 MHz, OTHER CLOCK GENERATOR, PDSO24 |

| ICS844003BGI-01LF | 680 MHz, OTHER CLOCK GENERATOR, PDSO24 |

| ICS844003BGI-01LF | 680 MHz, OTHER CLOCK GENERATOR, PDSO24 |

相关代理商/技术参数 |

参数描述 |

|---|---|

| ICS844002AGLFT | 功能描述:IC SYNTHESIZER 2LVDS 20-TSSOP RoHS:是 类别:集成电路 (IC) >> 时钟/计时 - 时钟发生器,PLL,频率合成器 系列:HiPerClockS™, FemtoClock™ 标准包装:1,000 系列:- 类型:时钟/频率合成器,扇出分配 PLL:- 输入:- 输出:- 电路数:- 比率 - 输入:输出:- 差分 - 输入:输出:- 频率 - 最大:- 除法器/乘法器:- 电源电压:- 工作温度:- 安装类型:表面贴装 封装/外壳:56-VFQFN 裸露焊盘 供应商设备封装:56-VFQFP-EP(8x8) 包装:带卷 (TR) 其它名称:844S012AKI-01LFT |

| ICS844002AKLF | 功能描述:IC SYNTHESIZER 2LVDS 32-VFQFPN RoHS:是 类别:集成电路 (IC) >> 时钟/计时 - 时钟发生器,PLL,频率合成器 系列:HiPerClockS™, FemtoClock™ 标准包装:1,000 系列:- 类型:时钟/频率合成器,扇出分配 PLL:- 输入:- 输出:- 电路数:- 比率 - 输入:输出:- 差分 - 输入:输出:- 频率 - 最大:- 除法器/乘法器:- 电源电压:- 工作温度:- 安装类型:表面贴装 封装/外壳:56-VFQFN 裸露焊盘 供应商设备封装:56-VFQFP-EP(8x8) 包装:带卷 (TR) 其它名称:844S012AKI-01LFT |

| ICS844002AKLFT | 功能描述:IC SYNTHESIZER 2LVDS 32-VFQFPN RoHS:是 类别:集成电路 (IC) >> 时钟/计时 - 时钟发生器,PLL,频率合成器 系列:HiPerClockS™, FemtoClock™ 标准包装:1,000 系列:- 类型:时钟/频率合成器,扇出分配 PLL:- 输入:- 输出:- 电路数:- 比率 - 输入:输出:- 差分 - 输入:输出:- 频率 - 最大:- 除法器/乘法器:- 电源电压:- 工作温度:- 安装类型:表面贴装 封装/外壳:56-VFQFN 裸露焊盘 供应商设备封装:56-VFQFP-EP(8x8) 包装:带卷 (TR) 其它名称:844S012AKI-01LFT |

| ICS844003AGLF | 功能描述:IC SYNTHESIZER 3LVDS 24-TSSOP RoHS:是 类别:集成电路 (IC) >> 时钟/计时 - 时钟发生器,PLL,频率合成器 系列:HiPerClockS™, FemtoClock™ 标准包装:27 系列:Precision Edge® 类型:频率合成器 PLL:是 输入:PECL,晶体 输出:PECL 电路数:1 比率 - 输入:输出:1:1 差分 - 输入:输出:无/是 频率 - 最大:800MHz 除法器/乘法器:是/无 电源电压:3.135 V ~ 5.25 V 工作温度:0°C ~ 85°C 安装类型:表面贴装 封装/外壳:28-SOIC(0.295",7.50mm 宽) 供应商设备封装:28-SOIC 包装:管件 |

| ICS844003AGLFT | 功能描述:IC SYNTHESIZER 3LVDS 24-TSSOP RoHS:是 类别:集成电路 (IC) >> 时钟/计时 - 时钟发生器,PLL,频率合成器 系列:HiPerClockS™, FemtoClock™ 标准包装:1,000 系列:- 类型:时钟/频率合成器,扇出分配 PLL:- 输入:- 输出:- 电路数:- 比率 - 输入:输出:- 差分 - 输入:输出:- 频率 - 最大:- 除法器/乘法器:- 电源电压:- 工作温度:- 安装类型:表面贴装 封装/外壳:56-VFQFN 裸露焊盘 供应商设备封装:56-VFQFP-EP(8x8) 包装:带卷 (TR) 其它名称:844S012AKI-01LFT |

发布紧急采购,3分钟左右您将得到回复。