- 您现在的位置:买卖IC网 > PDF目录2073 > ICS844031BGI-01LF (IDT, Integrated Device Technology Inc)IC CLK GEN ETHERNET 8TSSOP PDF资料下载

参数资料

| 型号: | ICS844031BGI-01LF |

| 厂商: | IDT, Integrated Device Technology Inc |

| 文件页数: | 12/13页 |

| 文件大小: | 0K |

| 描述: | IC CLK GEN ETHERNET 8TSSOP |

| 标准包装: | 96 |

| 系列: | HiPerClockS™, FemtoClock™ |

| 类型: | 时钟发生器 |

| PLL: | 是 |

| 输入: | 晶体 |

| 输出: | LVDS |

| 电路数: | 1 |

| 比率 - 输入:输出: | 1:1 |

| 差分 - 输入:输出: | 无/是 |

| 频率 - 最大: | 340MHz |

| 除法器/乘法器: | 是/无 |

| 电源电压: | 2.375 V ~ 3.465 V |

| 工作温度: | -40°C ~ 85°C |

| 安装类型: | 表面贴装 |

| 封装/外壳: | 8-TSSOP(0.173",4.40mm 宽) |

| 供应商设备封装: | 8-TSSOP |

| 包装: | 管件 |

IDT / ICS LVDS CLOCK GENERATOR

8

ICS844031BGI-01 REV. A MAY 1, 2008

ICS844031I-01

FEMTOCLOCKS CRYSTAL-TO-LVDS CLOCK GENERATOR

LVCMOS TO XTAL INTERFACE

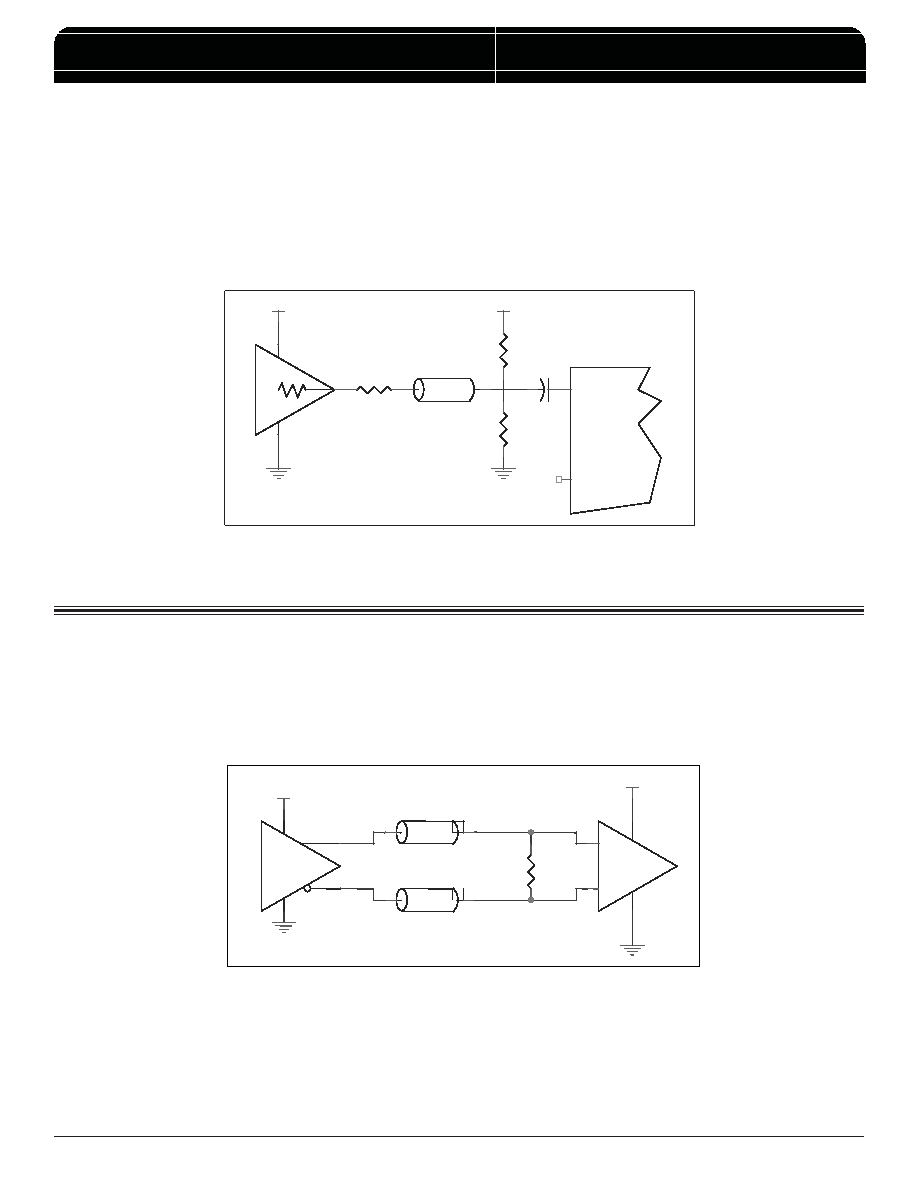

The XTAL_IN input can accept a single-ended LVCMOS signal

through an AC coupling capacitor. A general interface diagram is

shown in

Figure 3. The XTAL_OUT pin can be left floating. The

input edge rate can be as slow as 10ns. For LVCMOS inputs, it is

recommended that the amplitude be reduced from full swing to

half swing in order to prevent signal interference with the power

rail and to reduce noise. This configuration requires that the output

FIGURE 3. GENERAL DIAGRAM FOR LVCMOS DRIVER TO XTAL INPUT INTERFACE

impedance of the driver (Ro) plus the series resistance (Rs) equals

the transmission line impedance. In addition, matched termination

at the crystal input will attenuate the signal in half. This can be

done in one of two ways. First, R1 and R2 in parallel should equal

the transmission line impedance. For most 50

Ω applications, R1

and R2 can be 100

Ω.This can also be accomplished by removing

R1 and making R2 50

Ω.

R2

Zo = 50

VDD

Ro

Zo = Ro + Rs

R1

VDD

XTAL_IN

XTAL_OUT

.1uf

Rs

3.3V, 2.5V LVDS DRIVER TERMINATION

A general LVDS interface is shown in

Figure 4 In a 100

Ω

differential transmission line environment, LVDS drivers

require a matched load termination of 100

Ω across near

FIGURE 4. TYPICAL LVDS DRIVER TERMINATION

the receiver input. For a multiple LVDS outputs buffer, if only

partial outputs are used, it is recommended to terminate the

unused outputs.

R1

100

3.3V or 2.5V

100

Ω Differential Transmission

VDD

+

-

LVDS

相关PDF资料 |

PDF描述 |

|---|---|

| ICS845252AKILF | IC CLK GENERATOR CML 32VFQFN |

| ICS850S1201BGILF | IC CLOCK MUX 12:1 250MHZ 20TSSOP |

| ICS851010AYLFT | IC CLK BUFFER 1:10 250MHZ 32TQFP |

| ICS851021AYLF | IC CLK BUFFER 1:21 250MHZ 64TQFP |

| ICS85102AGILFT | IC CLOCK BUFFER MUX 2:2 16-TSSOP |

相关代理商/技术参数 |

参数描述 |

|---|---|

| ICS844031BGI-01LFT | 功能描述:IC CLK GEN ETHERNET 8TSSOP RoHS:是 类别:集成电路 (IC) >> 时钟/计时 - 时钟发生器,PLL,频率合成器 系列:HiPerClockS™, FemtoClock™ 标准包装:1,000 系列:- 类型:时钟/频率合成器,扇出分配 PLL:- 输入:- 输出:- 电路数:- 比率 - 输入:输出:- 差分 - 输入:输出:- 频率 - 最大:- 除法器/乘法器:- 电源电压:- 工作温度:- 安装类型:表面贴装 封装/外壳:56-VFQFN 裸露焊盘 供应商设备封装:56-VFQFP-EP(8x8) 包装:带卷 (TR) 其它名称:844S012AKI-01LFT |

| ICS844031BGI-01T | 制造商:Integrated Device Technology Inc 功能描述:IC SYNTHESIZER LVDS 8TSSOP |

| ICS844051CGILF | 功能描述:IC CLK GEN GIG ETH LVDS 8-TSSOP RoHS:是 类别:集成电路 (IC) >> 时钟/计时 - 时钟发生器,PLL,频率合成器 系列:HiPerClockS™, FemtoClock™ 标准包装:1,000 系列:Precision Edge® 类型:时钟/频率合成器 PLL:无 输入:CML,PECL 输出:CML 电路数:1 比率 - 输入:输出:2:1 差分 - 输入:输出:是/是 频率 - 最大:10.7GHz 除法器/乘法器:无/无 电源电压:2.375 V ~ 3.6 V 工作温度:-40°C ~ 85°C 安装类型:表面贴装 封装/外壳:16-VFQFN 裸露焊盘,16-MLF? 供应商设备封装:16-MLF?(3x3) 包装:带卷 (TR) 其它名称:SY58052UMGTRSY58052UMGTR-ND |

| ICS844051CGILFT | 功能描述:IC CLOCK GEN GIG ETH 8-TSSOP RoHS:是 类别:集成电路 (IC) >> 时钟/计时 - 时钟发生器,PLL,频率合成器 系列:HiPerClockS™, FemtoClock™ 标准包装:1,000 系列:- 类型:时钟/频率合成器,扇出分配 PLL:- 输入:- 输出:- 电路数:- 比率 - 输入:输出:- 差分 - 输入:输出:- 频率 - 最大:- 除法器/乘法器:- 电源电压:- 工作温度:- 安装类型:表面贴装 封装/外壳:56-VFQFN 裸露焊盘 供应商设备封装:56-VFQFP-EP(8x8) 包装:带卷 (TR) 其它名称:844S012AKI-01LFT |

| ICS844071AGLF | 功能描述:IC CLK GEN SAS LVDS 8-TSSOP RoHS:是 类别:集成电路 (IC) >> 时钟/计时 - 时钟发生器,PLL,频率合成器 系列:HiPerClockS™, FemtoClock™ 标准包装:2,000 系列:- 类型:PLL 频率合成器 PLL:是 输入:晶体 输出:时钟 电路数:1 比率 - 输入:输出:1:1 差分 - 输入:输出:无/无 频率 - 最大:1GHz 除法器/乘法器:是/无 电源电压:4.5 V ~ 5.5 V 工作温度:-20°C ~ 85°C 安装类型:表面贴装 封装/外壳:16-LSSOP(0.175",4.40mm 宽) 供应商设备封装:16-SSOP 包装:带卷 (TR) 其它名称:NJW1504V-TE1-NDNJW1504V-TE1TR |

发布紧急采购,3分钟左右您将得到回复。