- 您现在的位置:买卖IC网 > PDF目录67693 > ICS85104AMILF (INTEGRATED DEVICE TECHNOLOGY INC) 85104 SERIES, LOW SKEW CLOCK DRIVER, 4 TRUE OUTPUT(S), 0 INVERTED OUTPUT(S), PDSO20 PDF资料下载

参数资料

| 型号: | ICS85104AMILF |

| 厂商: | INTEGRATED DEVICE TECHNOLOGY INC |

| 元件分类: | 时钟及定时 |

| 英文描述: | 85104 SERIES, LOW SKEW CLOCK DRIVER, 4 TRUE OUTPUT(S), 0 INVERTED OUTPUT(S), PDSO20 |

| 封装: | 7.50 MM, 12.80 MM, 2.30 MM HEIGHT, ROHS COMPLIANT, MS-013, MO-119, SOIC-20 |

| 文件页数: | 1/13页 |

| 文件大小: | 304K |

| 代理商: | ICS85104AMILF |

LOW SKEW, 1-TO-4, DIFFERENTIAL/

LVCMOS-TO-0.7V HCSL FANOUT BUFFER

ICS85104I

IDT / ICS 0.7V HCSL FANOUT BUFFER

1

ICS85104AGI REV. A NOVEMBER 13, 2006

PRELIMINARY

GENERAL DESCRIPTION

The ICS85104I is a low skew, high performance 1-

to-4 Differential/LVCMOS-to-0.7V HCSL Fanout

Buffer and a member of the HiPerClockS family

of High Performance Clock Solutions from IDT.

The ICS85104I has two selectable clock inputs.

The CLK0, nCLK0 pair can accept most standard differential

input levels. The single-ended CLK1 can accept LVCMOS or

LVTTL input levels. The clock enable is internally synchronized

to eliminate runt clock pulses on the outputs during asynchro-

nous assertion/deassertion of the clock enable pin.

Guaranteed output and part-to-part skew characteristics make

the ICS85104I ideal for those applications demanding well

defined performance and repeatability.

FEATURES

Four 0.7V differential HCSL outputs

Selectable differential CLK0, nCLK0 or LVCMOS inputs

CLK0, nCLK0 pair can accept the following differential

input levels: LVPECL, LVDS, LVHSTL, HCSL, SSTL

CLK1 can accept the following input levels:

LVCMOS or LVTTL

Maximum output frequency: 500MHz

Translates any single-ended input signal to 3.3V

HCSL levels with resistor bias on nCLK input

Output skew: 75ps (typical), TSSOP package

TBD, SOIC package

Part-to-part skew: 300ps (typical)

Propagation delay: 2.4ns (typical)

Additive phase jitter, RMS: 0.31ps (typical)

3.3V operating supply

-40°C to 85°C ambient operating temperature

Available in both standard (RoHS 5) and lead-free (RoHS 6)

packages

HiPerClockS

ICS

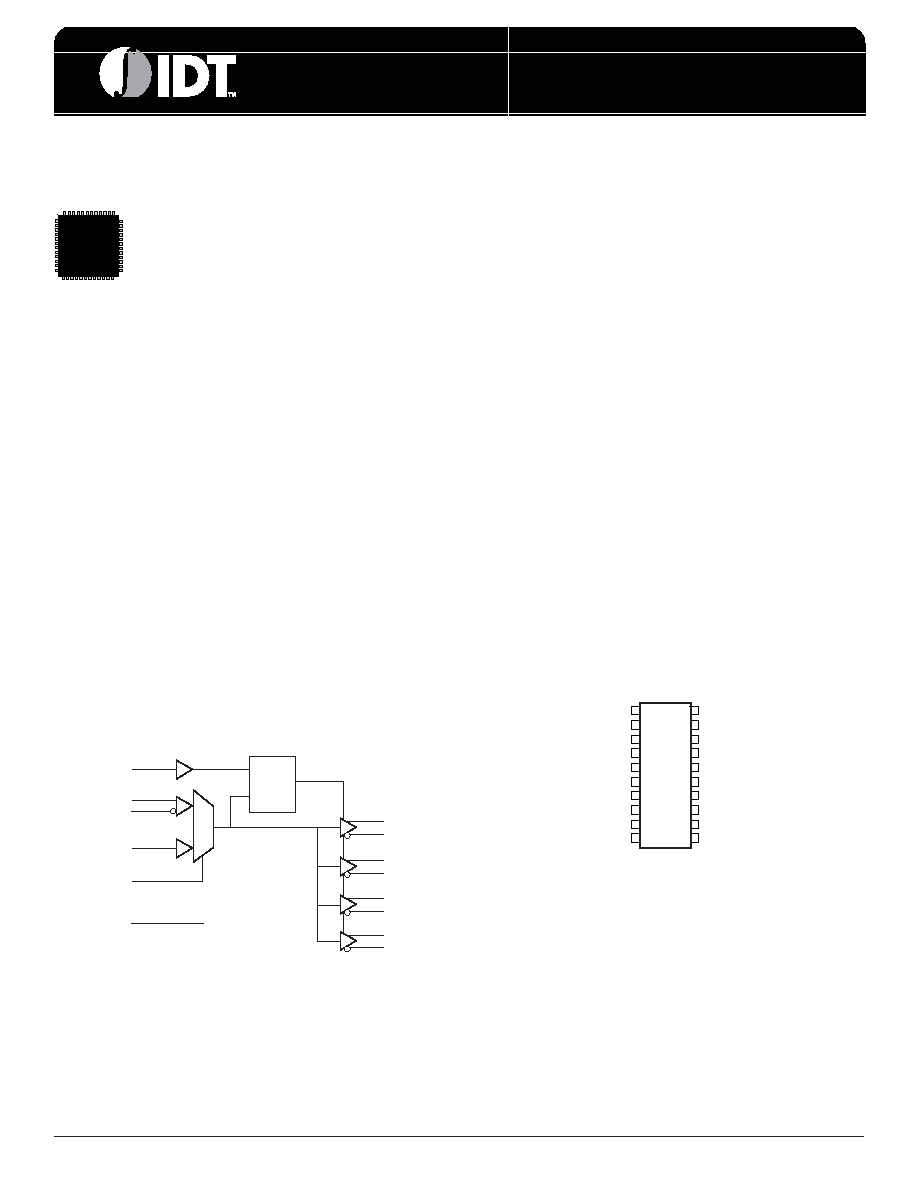

BLOCK DIAGRAM

PIN ASSIGNMENT

VSS

CLK_EN

CLK_SEL

CLK0

nCLK0

CLK1

nc

IREF

VDD

1

2

3

4

5

6

7

8

9

10

20

19

18

17

16

15

14

13

12

11

Q0

nQ0

VDD

Q1

nQ1

Q2

nQ2

VDD

Q3

nQ3

ICS85104I

20-Lead TSSOP

6.5mm x 4.4mm x 0.92mm Package Body

G Package

Top View

ICS85104I

20-Lead SOIC

7.5mm x 12.8mm x 2.3mm Package Body

M Package

Top View

Q0

nQ0

Q1

nQ1

CLK_EN

CLK_SEL

IREF

CLK1

CLK0

nCLK0

D

LE

Q

0

1

Q2

nQ2

Q3

nQ3

Pulldown

Pullup

The Preliminary Information presented herein represents a product in pre-production.The noted characteristics are based on initial product characterization and/

or qualification. Integrated Device Technology, Incorporated (IDT) reserves the right to change any circuitry or specifications without notice.

相关PDF资料 |

PDF描述 |

|---|---|

| ICS8516EY-T | LOW SKEW CLOCK DRIVER, 16 TRUE OUTPUT(S), 0 INVERTED OUTPUT(S), PQFP48 |

| ICS8516EYLF | LOW SKEW CLOCK DRIVER, 16 TRUE OUTPUT(S), 0 INVERTED OUTPUT(S), PQFP48 |

| ICS8516EY | LOW SKEW CLOCK DRIVER, 16 TRUE OUTPUT(S), 0 INVERTED OUTPUT(S), PQFP48 |

| ICS8516FY-01LF | LOW SKEW CLOCK DRIVER, 16 TRUE OUTPUT(S), 0 INVERTED OUTPUT(S), PQFP48 |

| ICS8516FYIT | LOW SKEW CLOCK DRIVER, 16 TRUE OUTPUT(S), 0 INVERTED OUTPUT(S), PQFP48 |

相关代理商/技术参数 |

参数描述 |

|---|---|

| ICS85105AGI | 制造商:Integrated Device Technology Inc 功能描述:IC CLK BUFFER 2:5 500MHZ 20TSSOP |

| ICS85105AGILF | 功能描述:IC CLOCK BUFFER MUX 2:5 20-TSSOP RoHS:是 类别:集成电路 (IC) >> 时钟/计时 - 时钟缓冲器,驱动器 系列:HiPerClockS™ 标准包装:74 系列:- 类型:扇出缓冲器(分配) 电路数:1 比率 - 输入:输出:1:10 差分 - 输入:输出:是/是 输入:HCSL, LVCMOS, LVDS, LVPECL, LVTTL 输出:HCSL,LVDS 频率 - 最大:400MHz 电源电压:3 V ~ 3.6 V 工作温度:-40°C ~ 85°C 安装类型:表面贴装 封装/外壳:32-VFQFN 裸露焊盘 供应商设备封装:32-QFN(5x5) 包装:管件 |

| ICS85105AGILFT | 功能描述:IC CLOCK BUFFER MUX 2:5 20-TSSOP RoHS:是 类别:集成电路 (IC) >> 时钟/计时 - 时钟缓冲器,驱动器 系列:HiPerClockS™ 标准包装:74 系列:- 类型:扇出缓冲器(分配) 电路数:1 比率 - 输入:输出:1:10 差分 - 输入:输出:是/是 输入:HCSL, LVCMOS, LVDS, LVPECL, LVTTL 输出:HCSL,LVDS 频率 - 最大:400MHz 电源电压:3 V ~ 3.6 V 工作温度:-40°C ~ 85°C 安装类型:表面贴装 封装/外壳:32-VFQFN 裸露焊盘 供应商设备封装:32-QFN(5x5) 包装:管件 |

| ICS85105AGIT | 制造商:Integrated Device Technology Inc 功能描述:IC CLK BUFFER 2:5 500MHZ 20TSSOP |

| ICS85108AGI | 制造商:Integrated Device Technology Inc 功能描述:IC CLK BUFFER 1:8 500MHZ 24TSSOP |

发布紧急采购,3分钟左右您将得到回复。