- 您现在的位置:买卖IC网 > PDF目录8991 > ICS86004BGLF (IDT, Integrated Device Technology Inc)IC CLK BUFFER ZD 1:4 16-TSSOP PDF资料下载

参数资料

| 型号: | ICS86004BGLF |

| 厂商: | IDT, Integrated Device Technology Inc |

| 文件页数: | 7/10页 |

| 文件大小: | 0K |

| 描述: | IC CLK BUFFER ZD 1:4 16-TSSOP |

| 标准包装: | 96 |

| 系列: | HiPerClockS™ |

| 类型: | 扇出配送,多路复用器,零延迟缓冲器 |

| PLL: | 带旁路 |

| 输入: | LVCMOS,LVTTL |

| 输出: | LVCMOS,LVTTL |

| 电路数: | 1 |

| 比率 - 输入:输出: | 1:4 |

| 差分 - 输入:输出: | 无/无 |

| 频率 - 最大: | 62.5MHz |

| 除法器/乘法器: | 是/无 |

| 电源电压: | 2.375 V ~ 3.465 V |

| 工作温度: | 0°C ~ 70°C |

| 安装类型: | 表面贴装 |

| 封装/外壳: | 16-TSSOP(0.173",4.40mm 宽) |

| 供应商设备封装: | 16-TSSOP |

| 包装: | 管件 |

| 其它名称: | 86004BGLF |

2005 Fairchild Semiconductor Corporation

www.fairchildsemi.com

FMS6363 Rev. 1.0.4

6

FM

S6363

—

Low-

C

ost

,Three-

C

h

annel,6t

h

-O

rder,

H

igh-

D

e

finit

ion,

Video

Filt

er

D

river

The same method can be used for biased signals with

the addition of a pull-up resistor to make sure the clamp

never operates. The internal pull-down resistance is

800k

Ω ±20%, so the external resistance should be

7.5M

Ω to set the DC level to 500mV. If a pull-up

resistance of less than 7.5M

Ω desired, add an external

pull-down such that the DC input level is set to 500mV.

75

Ω

LCVF

Bias

Input

75

Ω

0.1

External Video

source must

be AC-coupled.

500mV+/-350mV

7.5M

Ω

Figure 13. Biased SCART with DC-coupled Outputs

DVD or

STB

SoC

DAC

Output

75

Ω

LCVF

Clamp

Inactive

0V- 1.4V

220

Figure 14. DC-coupled Inputs, AC-coupled Outputs

75

Ω

LCVF

Clamp

Active

75

Ω

0.1

External video

source must

be AC-coupled.

220

500mV+/-350mV

7.5M

Ω

Figure 15. Biased SCART with AC-Coupled Outputs

Note

: The video tilt or line time distortion is dominated

by the AC-coupling capacitor. The value may

need to be increased beyond 220F to obtain

satisfactory operation in some applications.

Power Dissipation

The FMS6363 output drive configuration must be

considered when calculating overall power dissipation.

Care must be taken not to exceed the maximum die

junction temperature. The following example can be

used to calculate the FMS6363’s power dissipation and

internal temperature rise.

TJ= TA+ Pd ΘJA

where Pd= PCH1+ PCH2+ PCH3

and PCHx= VS ICH- (VO2/RL)

where

VO = 2VIN+ 0.280V

ICH = (ICC/ 3) + (VO/RL)

VIN= RMS value of input signal

ICC = 24mA

VS= 5V

RL= channel load resistance

(1)

Board layout affects thermal characteristics. Refer to

the Layout Considerations section for more information

.

The FMS6363 is specified to operate with output

currents typically less than 50mA, more than sufficient

for a single (150

Ω) video load. Internal amplifiers are

current limited to a maximum of 100mA and should

withstand

brief

duration,

short-circuit

conditions;

however, this capability is not guaranteed.

Output Considerations

The FMS6363 outputs will be DC offset from the input

by 150mv therefore VOUT = 2*VIN DC+150mv. This offset

is required to obtain optimal performance from the

output driver and is held at the minimum value in order

to decrease the standing DC current into the load.

Since the FMS6363 has a 2x (6dB) gain, the output is

typically connected via a 75 series back-matching

resistor followed by the 75 video cable. Because of

the inherent divide by two of this configuration, the

blanking level at the load of the video signal is always

less then 1V. When AC-coupling the output ensure that

the coupling capacitor of choice will pass the lowest

frequency content in the video signal and that line time

distortion (video tilt) is kept as low as possible.

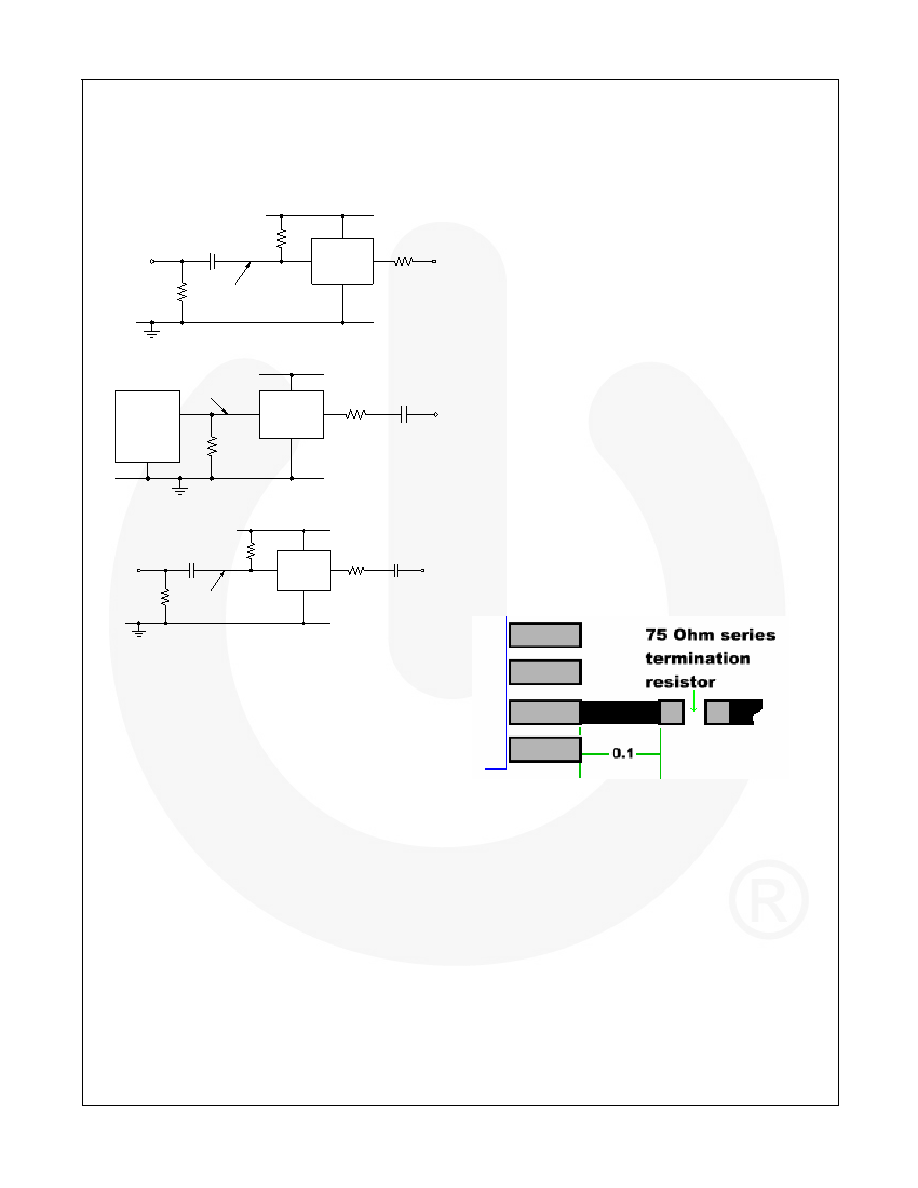

The selection of the coupling capacitor is a function of

the subsequent circuit input impedance and the leakage

current of the input being driven. In order to obtain the

highest

quality

output

video

signal

the

series

termination resistor must be placed as close to the

device output pin as possible. This greatly reduces the

parasitic capacitance and inductance effect on the

FMS6646 output driver. Recommend distance from

device pin to place series termination resistor should be

no greater than 0.1 inches.

Figure 16.Distance from Device Pin to Series

Termination Resistor

相关PDF资料 |

PDF描述 |

|---|---|

| D38999/26MC4SD | CONN PLUG 4POS STRAIGHT W/SCKT |

| ICS843004AG-125LFT | IC SYNTHESIZER LVPECL 24TSSOP |

| LTC1665IGN#PBF | IC D/A CONV 8BIT OCTAL 16-SSOP |

| VE-J4M-MZ-F4 | CONVERTER MOD DC/DC 10V 25W |

| SY89322VMG TR | IC TRANSLATOR DUAL 3.3/5V 8-MLF |

相关代理商/技术参数 |

参数描述 |

|---|---|

| ICS86004BGLFT | 功能描述:IC CLK BUFFER ZD 1:4 16-TSSOP RoHS:是 类别:集成电路 (IC) >> 时钟/计时 - 时钟发生器,PLL,频率合成器 系列:HiPerClockS™ 标准包装:1,000 系列:- 类型:时钟/频率合成器,扇出分配 PLL:- 输入:- 输出:- 电路数:- 比率 - 输入:输出:- 差分 - 输入:输出:- 频率 - 最大:- 除法器/乘法器:- 电源电压:- 工作温度:- 安装类型:表面贴装 封装/外壳:56-VFQFN 裸露焊盘 供应商设备封装:56-VFQFP-EP(8x8) 包装:带卷 (TR) 其它名称:844S012AKI-01LFT |

| ICS8602AY | 制造商:ICS 功能描述: |

| ICS8602BYLF | 功能描述:IC CLOCK GEN ZD 1-9 32-LQFP RoHS:是 类别:集成电路 (IC) >> 时钟/计时 - 时钟发生器,PLL,频率合成器 系列:HiPerClockS™ 标准包装:1,000 系列:- 类型:时钟/频率合成器,扇出分配 PLL:- 输入:- 输出:- 电路数:- 比率 - 输入:输出:- 差分 - 输入:输出:- 频率 - 最大:- 除法器/乘法器:- 电源电压:- 工作温度:- 安装类型:表面贴装 封装/外壳:56-VFQFN 裸露焊盘 供应商设备封装:56-VFQFP-EP(8x8) 包装:带卷 (TR) 其它名称:844S012AKI-01LFT |

| ICS8602BYLFT | 功能描述:IC CLOCK GEN ZD 1-9 32-LQFP RoHS:是 类别:集成电路 (IC) >> 时钟/计时 - 时钟发生器,PLL,频率合成器 系列:HiPerClockS™ 标准包装:1,000 系列:- 类型:时钟/频率合成器,扇出分配 PLL:- 输入:- 输出:- 电路数:- 比率 - 输入:输出:- 差分 - 输入:输出:- 频率 - 最大:- 除法器/乘法器:- 电源电压:- 工作温度:- 安装类型:表面贴装 封装/外壳:56-VFQFN 裸露焊盘 供应商设备封装:56-VFQFP-EP(8x8) 包装:带卷 (TR) 其它名称:844S012AKI-01LFT |

| ICS8624BYILF | 功能描述:IC BUFFER ZD 1-5 HSTL 32-LQFP RoHS:是 类别:集成电路 (IC) >> 时钟/计时 - 时钟发生器,PLL,频率合成器 系列:HiPerClockS™ 标准包装:27 系列:Precision Edge® 类型:频率合成器 PLL:是 输入:PECL,晶体 输出:PECL 电路数:1 比率 - 输入:输出:1:1 差分 - 输入:输出:无/是 频率 - 最大:800MHz 除法器/乘法器:是/无 电源电压:3.135 V ~ 5.25 V 工作温度:0°C ~ 85°C 安装类型:表面贴装 封装/外壳:28-SOIC(0.295",7.50mm 宽) 供应商设备封装:28-SOIC 包装:管件 |

发布紧急采购,3分钟左右您将得到回复。