- 您现在的位置:买卖IC网 > PDF目录67699 > ICS87004AGILF 87004 SERIES, PLL BASED CLOCK DRIVER, 4 TRUE OUTPUT(S), 0 INVERTED OUTPUT(S), PDSO24 PDF资料下载

参数资料

| 型号: | ICS87004AGILF |

| 元件分类: | 时钟及定时 |

| 英文描述: | 87004 SERIES, PLL BASED CLOCK DRIVER, 4 TRUE OUTPUT(S), 0 INVERTED OUTPUT(S), PDSO24 |

| 封装: | 4.40 X 7.80 MM, 0.92 MM HEIGHT, ROHS COMPLIANT, MO-153, TSSOP-24 |

| 文件页数: | 15/15页 |

| 文件大小: | 172K |

| 代理商: | ICS87004AGILF |

87004AGI

www.icst.com/products/hiperclocks.html

REV. C OCTOBER 14, 2005

9

Integrated

Circuit

Systems, Inc.

ICS87004I

1:4, DIFFERENTIAL-TO-LVCMOS/LVTTL

ZERO DELAY CLOCK GENERATOR

APPLICATION INFORMATION

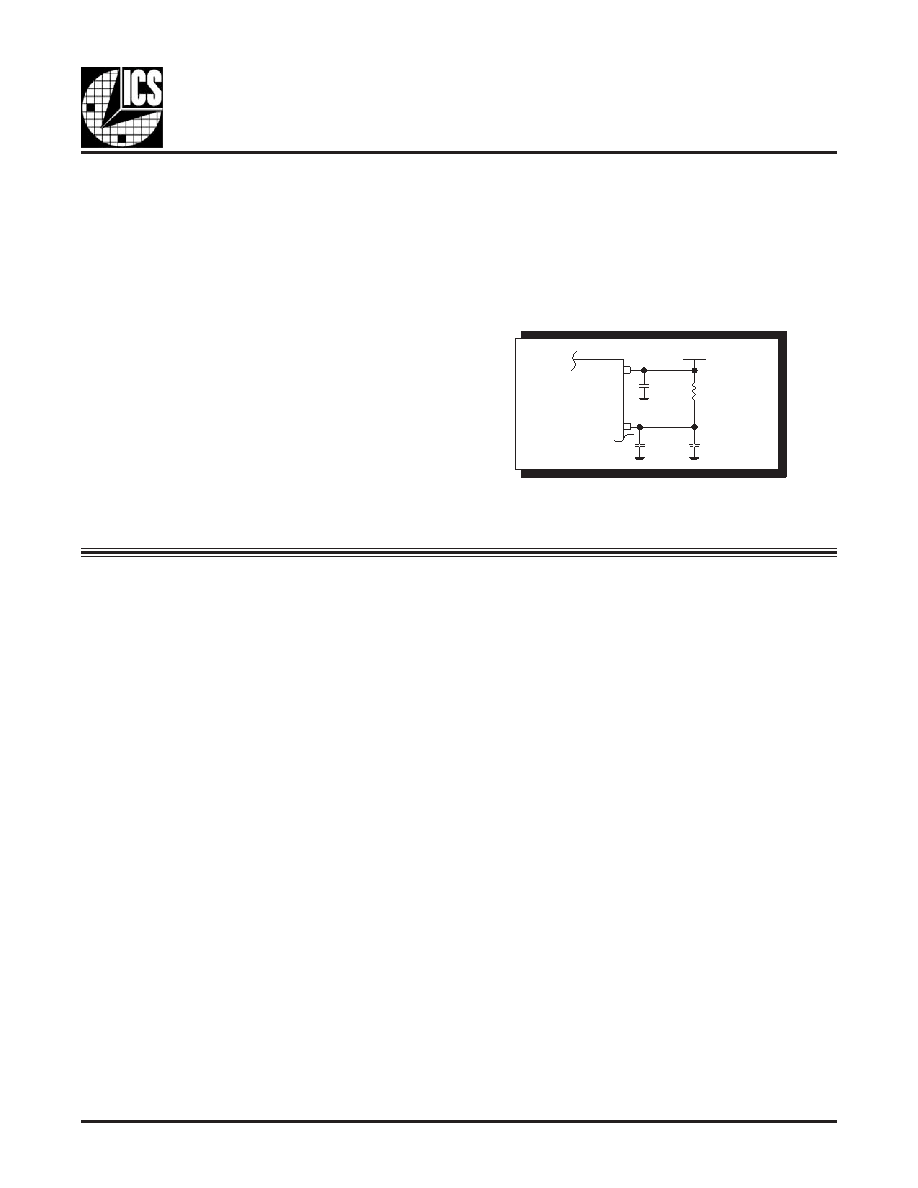

As in any high speed analog circuitry, the power supply pins

are vulnerable to random noise. The ICS87004I provides sepa-

rate power supplies to isolate any high switching

noise from the outputs to the internal PLL. V

DD, VDDA, and VDDO

should be individually connected to the power supply

plane through vias, and bypass capacitors should be

used for each pin. To achieve optimum jitter performance,

power supply isolation is required. Figure 1 illustrates how

a 10

Ω resistor along with a 10F and a .01μF bypass

capacitor should be connected to each V

DDA.

POWER SUPPLY FILTERING TECHNIQUES

FIGURE 1. POWER SUPPLY FILTERING

10

Ω

V

DDA

10

μF

.01

μF

3.3V or 2.5V

.01

μF

V

DD

INPUTS:

CLK/nCLK INPUT:

For applications not requiring the use of the differential input,

both CLK and nCLK can be left floating. Though not required,

but for additional protection, a 1k

Ω resistor can be tied from

CLK to ground.

SELECT PINS:

All select pins have internal pull-ups or pull-downs; additional

resistance is not required but can be added for additional

protection. A 1k

Ω resistor can be used.

RECOMMENDATIONS FOR UNUSED INPUT AND OUTPUT PINS

OUTPUTS:

LVCMOS OUTPUT:

All unused LVCMOS output can be left floating. We

recommend that there is no trace attached.

相关PDF资料 |

PDF描述 |

|---|---|

| ICS87004AGLFT | 87004 SERIES, PLL BASED CLOCK DRIVER, 4 TRUE OUTPUT(S), 0 INVERTED OUTPUT(S), PDSO24 |

| ICS87004AGT | 87004 SERIES, PLL BASED CLOCK DRIVER, 4 TRUE OUTPUT(S), 0 INVERTED OUTPUT(S), PDSO24 |

| ICS87004AG | 87004 SERIES, PLL BASED CLOCK DRIVER, 4 TRUE OUTPUT(S), 0 INVERTED OUTPUT(S), PDSO24 |

| ICS87004AGLF | 87004 SERIES, PLL BASED CLOCK DRIVER, 4 TRUE OUTPUT(S), 0 INVERTED OUTPUT(S), PDSO24 |

| ICS87008AGI | 87008 SERIES, LOW SKEW CLOCK DRIVER, 8 TRUE OUTPUT(S), 0 INVERTED OUTPUT(S), PDSO24 |

相关代理商/技术参数 |

参数描述 |

|---|---|

| ICS87004AGILFT | 功能描述:IC CLOCK GEN ZD 1:4 24-TSSOP RoHS:是 类别:集成电路 (IC) >> 时钟/计时 - 时钟发生器,PLL,频率合成器 系列:HiPerClockS™ 标准包装:1,000 系列:- 类型:时钟/频率合成器,扇出分配 PLL:- 输入:- 输出:- 电路数:- 比率 - 输入:输出:- 差分 - 输入:输出:- 频率 - 最大:- 除法器/乘法器:- 电源电压:- 工作温度:- 安装类型:表面贴装 封装/外壳:56-VFQFN 裸露焊盘 供应商设备封装:56-VFQFP-EP(8x8) 包装:带卷 (TR) 其它名称:844S012AKI-01LFT |

| ICS87004AGLF | 功能描述:IC CLK GENERATOR ZD 1:4 24-TSSOP RoHS:是 类别:集成电路 (IC) >> 时钟/计时 - 时钟发生器,PLL,频率合成器 系列:HiPerClockS™ 标准包装:1,000 系列:Precision Edge® 类型:时钟/频率合成器 PLL:无 输入:CML,PECL 输出:CML 电路数:1 比率 - 输入:输出:2:1 差分 - 输入:输出:是/是 频率 - 最大:10.7GHz 除法器/乘法器:无/无 电源电压:2.375 V ~ 3.6 V 工作温度:-40°C ~ 85°C 安装类型:表面贴装 封装/外壳:16-VFQFN 裸露焊盘,16-MLF? 供应商设备封装:16-MLF?(3x3) 包装:带卷 (TR) 其它名称:SY58052UMGTRSY58052UMGTR-ND |

| ICS87004AGLFT | 功能描述:IC CLOCK GEN ZD 1:4 24-TSSOP RoHS:是 类别:集成电路 (IC) >> 时钟/计时 - 时钟发生器,PLL,频率合成器 系列:HiPerClockS™ 标准包装:1,000 系列:- 类型:时钟/频率合成器,扇出分配 PLL:- 输入:- 输出:- 电路数:- 比率 - 输入:输出:- 差分 - 输入:输出:- 频率 - 最大:- 除法器/乘法器:- 电源电压:- 工作温度:- 安装类型:表面贴装 封装/外壳:56-VFQFN 裸露焊盘 供应商设备封装:56-VFQFP-EP(8x8) 包装:带卷 (TR) 其它名称:844S012AKI-01LFT |

| ICS87004BG-03LF | 功能描述:IC CLOCK DIVIDER MUX 2:4 20TSSOP RoHS:是 类别:集成电路 (IC) >> 时钟/计时 - 时钟缓冲器,驱动器 系列:HiPerClockS™ 标准包装:74 系列:- 类型:扇出缓冲器(分配) 电路数:1 比率 - 输入:输出:1:10 差分 - 输入:输出:是/是 输入:HCSL, LVCMOS, LVDS, LVPECL, LVTTL 输出:HCSL,LVDS 频率 - 最大:400MHz 电源电压:3 V ~ 3.6 V 工作温度:-40°C ~ 85°C 安装类型:表面贴装 封装/外壳:32-VFQFN 裸露焊盘 供应商设备封装:32-QFN(5x5) 包装:管件 |

| ICS87004BG-03LFT | 功能描述:IC CLOCK DIVIDER MUX 2:4 20TSSOP RoHS:是 类别:集成电路 (IC) >> 时钟/计时 - 时钟缓冲器,驱动器 系列:HiPerClockS™ 标准包装:74 系列:- 类型:扇出缓冲器(分配) 电路数:1 比率 - 输入:输出:1:10 差分 - 输入:输出:是/是 输入:HCSL, LVCMOS, LVDS, LVPECL, LVTTL 输出:HCSL,LVDS 频率 - 最大:400MHz 电源电压:3 V ~ 3.6 V 工作温度:-40°C ~ 85°C 安装类型:表面贴装 封装/外壳:32-VFQFN 裸露焊盘 供应商设备封装:32-QFN(5x5) 包装:管件 |

发布紧急采购,3分钟左右您将得到回复。