- 您现在的位置:买卖IC网 > PDF目录2074 > ICS870919BVI-01LF (IDT, Integrated Device Technology Inc)IC CLK GENERATOR LVCMOS 28PLCC PDF资料下载

参数资料

| 型号: | ICS870919BVI-01LF |

| 厂商: | IDT, Integrated Device Technology Inc |

| 文件页数: | 12/16页 |

| 文件大小: | 0K |

| 描述: | IC CLK GENERATOR LVCMOS 28PLCC |

| 标准包装: | 38 |

| 系列: | HiPerClockS™ |

| 类型: | 时钟发生器 |

| PLL: | 带旁路 |

| 输入: | LVCMOS,LVTTL |

| 输出: | LVCMOS,LVTTL |

| 电路数: | 1 |

| 比率 - 输入:输出: | 2:8 |

| 差分 - 输入:输出: | 无/无 |

| 频率 - 最大: | 160MHz |

| 除法器/乘法器: | 是/是 |

| 电源电压: | 3 V ~ 3.6 V |

| 工作温度: | -40°C ~ 85°C |

| 安装类型: | 表面贴装 |

| 封装/外壳: | 28-LCC(J 形引线) |

| 供应商设备封装: | 28-PLCC(11.5x11.5) |

| 包装: | 管件 |

ICS870919BVI-01 REVISION C JANUARY 6, 2012

5

2012 Integrated Device Technology, Inc.

ICS870919I-01 Data Sheet

LVCMOS CLOCK GENERATOR

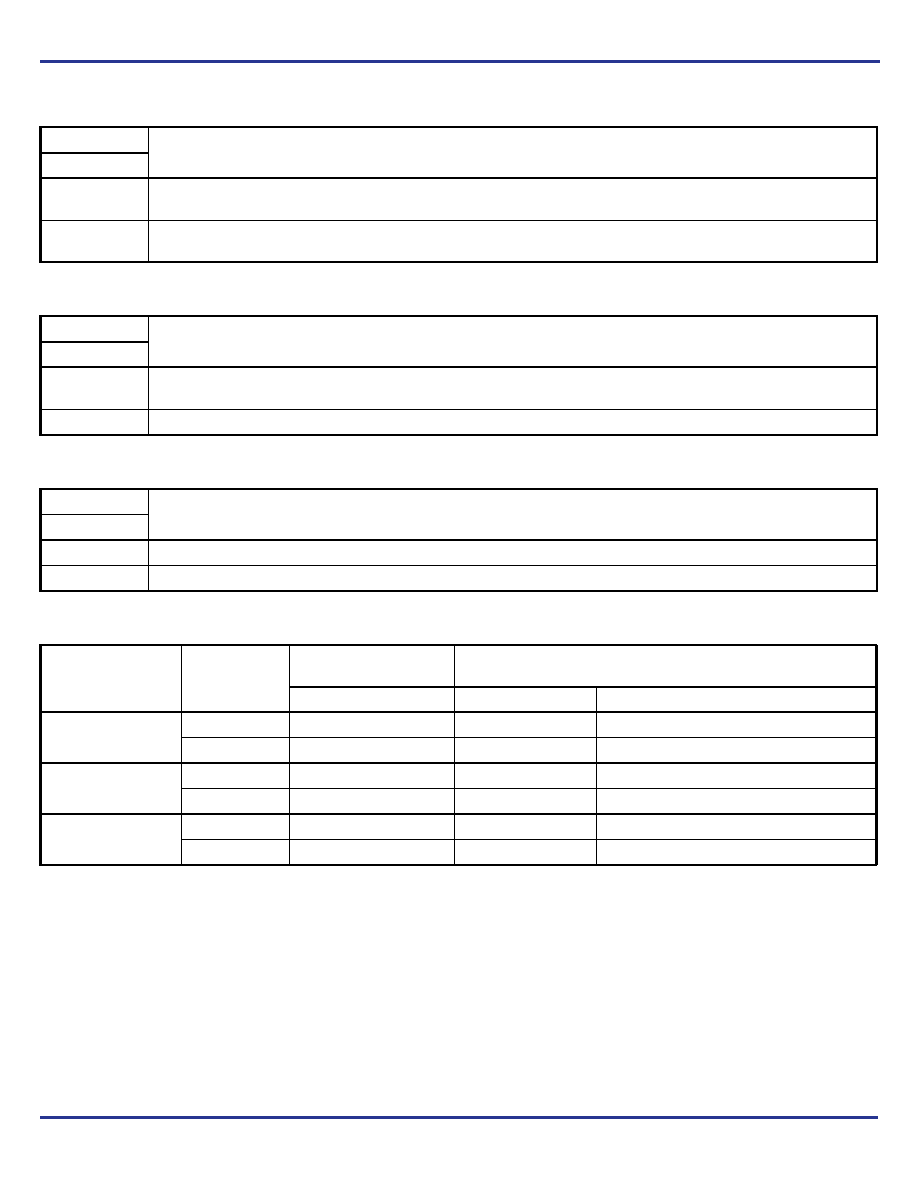

Table 3D. FREQ_SEL Mode Configuration Table

Table 3E. PLL_EN Mode Configuration Table

Table 3F. LOCK Mode Configuration Table

Table 3G. Frequency Configuration Table

NOTE 1: The nQ5 output is inverted (180° phase shift) with respect to Q0:Q4.

NOTE 2: The input reference frequency is limited to 100MHz maximum.

Input

Operation

FREQ_SEL

0

The VCO output is frequency-divided by 2. This setting allows for a lower input frequency range.

See also table 3G for available frequency ranges.

1

The VCO output is frequency-divided by 1. This setting allows for a higher input frequency range.

See also table 3G for available frequency ranges.

Input

Operation

PLL_EN

0

The PLL is bypassed. The selected input reference clock is routed to the output dividers for low-frequency board test

purpose. The PLL-related AC specifications do not apply in PLL bypass mode.

1

The PLL is enabled and locks to the selected input reference signal.

Output

Operation

LOCK

0

PLL is not locked to the selected input reference clock.

1

PLL is locked to the selected input reference clock.

Outputs Used for

PLL Feedback

FREQ_SEL

Input Frequency Range

(MHz)

Output Frequency Range (MHz) and

Output-to-Input Frequency Multiplication Factor

SYNC[0:1]

Q[0:4], nQ5NOTE1

2XQ

Q/2

Q0, Q1, Q2,

Q3, Q4 or nQ5

0

5 - 40

5 - 40 (1x)

10 - 80 (2x)

2.5 - 20 (0.5x)

1

10 - 80

10 - 80 (1x)

20 - 160 (2x)

5 - 40 (0.5x)

2XQ

0

10 - 80

5 - 40 (0.5x)

10 - 80 (1x)

2.5 - 20 (0.25x)

1

20 - 100NOTE2

10 - 50 (0.5x)

20 - 100 (1x)

5 - 25 (0.25x)

Q/2

0

2.5 - 20

5 - 40 (2x)

10 - 80 (4x)

2.5 - 20 (1x)

1

5 - 40

10 - 80 (2x)

20 - 160 (4x)

5 - 40 (1x)

相关PDF资料 |

PDF描述 |

|---|---|

| ICS8735AY-31LF | IC CLK GEN ZD DIFF-LVPECL 32LQFP |

| ICS8737AG-11LFT | IC CLK BUFF DVDR MUX 2:2 20TSSOP |

| ICS873990AYLF | IC CLK GEN LV LVPECL/ECL 52-LQFP |

| ICS873991AY-147LF | IC CLK GEN LV ECL LVPECL 52-LQFP |

| ICS873991AYLFT | IC CLK GEN LV LVPECL 52-LQFP |

相关代理商/技术参数 |

参数描述 |

|---|---|

| ICS870919BVI-01LFT | 功能描述:IC CLK GENERATOR LVCMOS 28PLCC RoHS:是 类别:集成电路 (IC) >> 时钟/计时 - 时钟发生器,PLL,频率合成器 系列:HiPerClockS™ 标准包装:1,000 系列:- 类型:时钟/频率合成器,扇出分配 PLL:- 输入:- 输出:- 电路数:- 比率 - 输入:输出:- 差分 - 输入:输出:- 频率 - 最大:- 除法器/乘法器:- 电源电压:- 工作温度:- 安装类型:表面贴装 封装/外壳:56-VFQFN 裸露焊盘 供应商设备封装:56-VFQFP-EP(8x8) 包装:带卷 (TR) 其它名称:844S012AKI-01LFT |

| ICS870919BVILF | 功能描述:IC CLK GENERATOR LVCMOS 28PLCC RoHS:是 类别:集成电路 (IC) >> 时钟/计时 - 时钟发生器,PLL,频率合成器 系列:HiPerClockS™, FemtoClock™ 标准包装:27 系列:Precision Edge® 类型:频率合成器 PLL:是 输入:PECL,晶体 输出:PECL 电路数:1 比率 - 输入:输出:1:1 差分 - 输入:输出:无/是 频率 - 最大:800MHz 除法器/乘法器:是/无 电源电压:3.135 V ~ 5.25 V 工作温度:0°C ~ 85°C 安装类型:表面贴装 封装/外壳:28-SOIC(0.295",7.50mm 宽) 供应商设备封装:28-SOIC 包装:管件 |

| ICS870919BVILFT | 功能描述:IC CLK GENERATOR LVCMOS 28PLCC RoHS:是 类别:集成电路 (IC) >> 时钟/计时 - 时钟发生器,PLL,频率合成器 系列:HiPerClockS™, FemtoClock™ 标准包装:1,000 系列:- 类型:时钟/频率合成器,扇出分配 PLL:- 输入:- 输出:- 电路数:- 比率 - 输入:输出:- 差分 - 输入:输出:- 频率 - 最大:- 除法器/乘法器:- 电源电压:- 工作温度:- 安装类型:表面贴装 封装/外壳:56-VFQFN 裸露焊盘 供应商设备封装:56-VFQFP-EP(8x8) 包装:带卷 (TR) 其它名称:844S012AKI-01LFT |

| ICS870931ARI-01 | 制造商:Integrated Device Technology Inc 功能描述:IC CLK GENERATOR LVCMOS 20QSOP |

| ICS870931ARI-01LF | 功能描述:IC CLK GENERATOR LVCMOS 20QSOP RoHS:是 类别:集成电路 (IC) >> 时钟/计时 - 时钟发生器,PLL,频率合成器 系列:HiPerClockS™ 标准包装:1,000 系列:- 类型:时钟/频率合成器,扇出分配 PLL:- 输入:- 输出:- 电路数:- 比率 - 输入:输出:- 差分 - 输入:输出:- 频率 - 最大:- 除法器/乘法器:- 电源电压:- 工作温度:- 安装类型:表面贴装 封装/外壳:56-VFQFN 裸露焊盘 供应商设备封装:56-VFQFP-EP(8x8) 包装:带卷 (TR) 其它名称:844S012AKI-01LFT |

发布紧急采购,3分钟左右您将得到回复。