- 您现在的位置:买卖IC网 > PDF目录377124 > ICS873991AY-147LFT (INTEGRATED DEVICE TECHNOLOGY INC) LOW VOLTAGE, LVCMOS/LVPECL-TO LVPECL/ECL CLOCK GENERATOR PDF资料下载

参数资料

| 型号: | ICS873991AY-147LFT |

| 厂商: | INTEGRATED DEVICE TECHNOLOGY INC |

| 元件分类: | 时钟及定时 |

| 英文描述: | LOW VOLTAGE, LVCMOS/LVPECL-TO LVPECL/ECL CLOCK GENERATOR |

| 中文描述: | 873991 SERIES, LOW SKEW CLOCK DRIVER, 13 TRUE OUTPUT(S), 0 INVERTED OUTPUT(S), PQFP52 |

| 封装: | 10 X 10 MM, 1.40 MM HEIGHT, ROHS COMPLIANT, MS-026BCC, LQFP-52 |

| 文件页数: | 9/17页 |

| 文件大小: | 292K |

| 代理商: | ICS873991AY-147LFT |

IDT

/ ICS

LVPECL/ECL CLOCK GENERATOR

9

ICS873991AY-147 REV. A AUGUST 10, 2007

ICS873991-147

LOW VOLTAGE, LVCMOS/LVPECL-TO-LVPECL/ECL CLOCK GENERATOR

PRELIMINARY

Figure 3

shows how the differential input can be wired to accept

single ended levels. The reference voltage V_REF = V

/2 is

generated by the bias resistors R1, R2 and C1. This bias circuit

should be located as close as possible to the input pin. The ratio

F

IGURE

3. S

INGLE

E

NDED

S

IGNAL

D

RIVING

D

IFFERENTIAL

I

NPUT

W

IRING

THE

D

IFFERENTIAL

I

NPUT

TO

A

CCEPT

S

INGLE

E

NDED

L

EVELS

of R1 and R2 might need to be adjusted to position the V_REF in

the center of the input voltage swing. For example, if the input

clock swing is only 2.5V and V

CC

= 3.3V, V_REF should be 1.25V

and R2/R1 = 0.609.

As in any high speed analog circuitry, the power supply pins

are vulnerable to random noise. The ICS873991-147 provides

separate power supplies to isolate any high switching

noise from the outputs to the internal PLL. V

, V

and V

should be individually connected to the power supply plane

through vias, and bypass capacitors should be used for each

pin. To achieve optimum jitter performance, power supply iso-

lation is required.

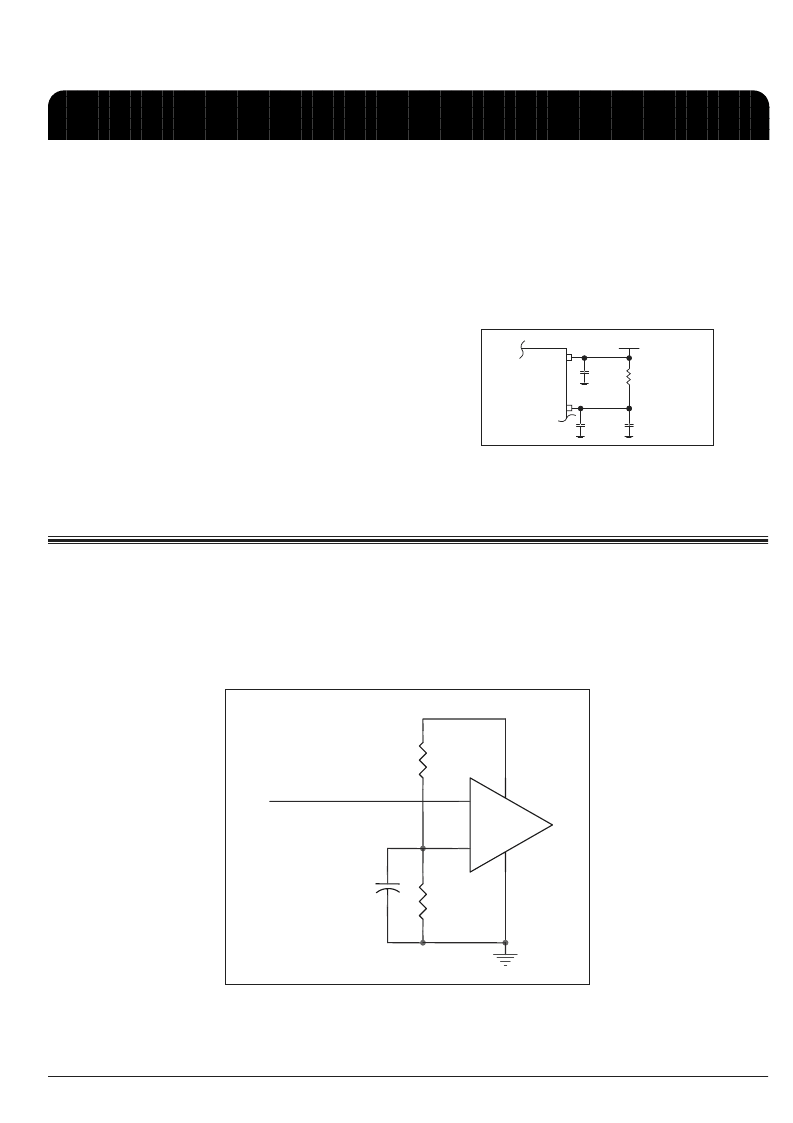

Figure 2

illustrates how a 10

Ω

resistor along

with a 10

μ

F and a 0.01

μ

F bypass capacitor should be con-

nected to each V

CCA

pin.

F

IGURE

2. P

OWER

S

UPPLY

F

ILTERING

10

Ω

V

CCA

10

μ

F

.01

μ

F

3.3V

.01

μ

F

V

CC

P

OWER

S

UPPLY

F

ILTERING

T

ECHNIQUES

A

PPLICATIONS

I

NFORMATION

VCC

R2

1K

V_REF

C1

0.1u

R1

1K

Single Ended Clock Input

PCLK

nPCLK

相关PDF资料 |

PDF描述 |

|---|---|

| ICS8741004 | DIFFERENTIAL-TO-LVDS/0.7V DIFFERENTIAL PCI EXPRESS⑩ JITTER ATTENUATOR |

| ICS8741004AG | DIFFERENTIAL-TO-LVDS/0.7V DIFFERENTIAL PCI EXPRESS⑩ JITTER ATTENUATOR |

| ICS8741004AGLF | DIFFERENTIAL-TO-LVDS/0.7V DIFFERENTIAL PCI EXPRESS⑩ JITTER ATTENUATOR |

| ICS98ULPA877A | 1.8V Low-Power Wide-Range Frequency Clock Driver |

| ICS98ULPA877AKLF-T | 1.8V Low-Power Wide-Range Frequency Clock Driver |

相关代理商/技术参数 |

参数描述 |

|---|---|

| ICS873991AYLF | 功能描述:IC CLK GEN LV LVPECL/ECL 52-LQFP RoHS:是 类别:集成电路 (IC) >> 时钟/计时 - 时钟发生器,PLL,频率合成器 系列:HiPerClockS™ 标准包装:2,000 系列:- 类型:PLL 频率合成器 PLL:是 输入:晶体 输出:时钟 电路数:1 比率 - 输入:输出:1:1 差分 - 输入:输出:无/无 频率 - 最大:1GHz 除法器/乘法器:是/无 电源电压:4.5 V ~ 5.5 V 工作温度:-20°C ~ 85°C 安装类型:表面贴装 封装/外壳:16-LSSOP(0.175",4.40mm 宽) 供应商设备封装:16-SSOP 包装:带卷 (TR) 其它名称:NJW1504V-TE1-NDNJW1504V-TE1TR |

| ICS873991AYLFT | 功能描述:IC CLK GEN LV LVPECL 52-LQFP RoHS:是 类别:集成电路 (IC) >> 时钟/计时 - 时钟发生器,PLL,频率合成器 系列:HiPerClockS™ 标准包装:1,000 系列:- 类型:时钟/频率合成器,扇出分配 PLL:- 输入:- 输出:- 电路数:- 比率 - 输入:输出:- 差分 - 输入:输出:- 频率 - 最大:- 除法器/乘法器:- 电源电压:- 工作温度:- 安装类型:表面贴装 封装/外壳:56-VFQFN 裸露焊盘 供应商设备封装:56-VFQFP-EP(8x8) 包装:带卷 (TR) 其它名称:844S012AKI-01LFT |

| ICS873995AYLF | 功能描述:IC ZD/MULT/DIVIDER 48-LQFP RoHS:是 类别:集成电路 (IC) >> 时钟/计时 - 时钟发生器,PLL,频率合成器 系列:HiPerClockS™ 标准包装:1,000 系列:- 类型:时钟/频率合成器,扇出分配 PLL:- 输入:- 输出:- 电路数:- 比率 - 输入:输出:- 差分 - 输入:输出:- 频率 - 最大:- 除法器/乘法器:- 电源电压:- 工作温度:- 安装类型:表面贴装 封装/外壳:56-VFQFN 裸露焊盘 供应商设备封装:56-VFQFP-EP(8x8) 包装:带卷 (TR) 其它名称:844S012AKI-01LFT |

| ICS873995AYLFT | 功能描述:IC ZD/MULT/DIVIDER 48-LQFP RoHS:是 类别:集成电路 (IC) >> 时钟/计时 - 时钟发生器,PLL,频率合成器 系列:HiPerClockS™ 标准包装:1,000 系列:- 类型:时钟/频率合成器,扇出分配 PLL:- 输入:- 输出:- 电路数:- 比率 - 输入:输出:- 差分 - 输入:输出:- 频率 - 最大:- 除法器/乘法器:- 电源电压:- 工作温度:- 安装类型:表面贴装 封装/外壳:56-VFQFN 裸露焊盘 供应商设备封装:56-VFQFP-EP(8x8) 包装:带卷 (TR) 其它名称:844S012AKI-01LFT |

| ICS873996AYLF | 功能描述:IC ZD/MULT/DIVIDER 48-LQFP RoHS:是 类别:集成电路 (IC) >> 时钟/计时 - 时钟发生器,PLL,频率合成器 系列:HiPerClockS™ 标准包装:2,000 系列:- 类型:PLL 频率合成器 PLL:是 输入:晶体 输出:时钟 电路数:1 比率 - 输入:输出:1:1 差分 - 输入:输出:无/无 频率 - 最大:1GHz 除法器/乘法器:是/无 电源电压:4.5 V ~ 5.5 V 工作温度:-20°C ~ 85°C 安装类型:表面贴装 封装/外壳:16-LSSOP(0.175",4.40mm 宽) 供应商设备封装:16-SSOP 包装:带卷 (TR) 其它名称:NJW1504V-TE1-NDNJW1504V-TE1TR |

发布紧急采购,3分钟左右您将得到回复。