- 您现在的位置:买卖IC网 > PDF目录9185 > ICS873996AYLF (IDT, Integrated Device Technology Inc)IC ZD/MULT/DIVIDER 48-LQFP PDF资料下载

参数资料

| 型号: | ICS873996AYLF |

| 厂商: | IDT, Integrated Device Technology Inc |

| 文件页数: | 8/10页 |

| 文件大小: | 0K |

| 描述: | IC ZD/MULT/DIVIDER 48-LQFP |

| 标准包装: | 250 |

| 系列: | HiPerClockS™ |

| 类型: | 零延迟,倍增器,除法器 |

| PLL: | 带旁路 |

| 输入: | HCSL,LVDS,LVHSTL,LVPECL,SSTL |

| 输出: | LVPECL |

| 电路数: | 1 |

| 比率 - 输入:输出: | 2:6 |

| 差分 - 输入:输出: | 是/是 |

| 频率 - 最大: | 640MHz |

| 除法器/乘法器: | 是/是 |

| 电源电压: | 3.135 V ~ 3.465 V |

| 工作温度: | 0°C ~ 70°C |

| 安装类型: | 表面贴装 |

| 封装/外壳: | 48-TQFP 裸露焊盘 |

| 供应商设备封装: | 48-PTQFP-EP(7x7) |

| 包装: | 托盘 |

| 其它名称: | 800-2287 873996AYLF ICS873996AYLF-ND |

Micrel, Inc.

SY88149CL

January 2009

7

M9999-011609-C

hbwhelp@micrel.com or (408) 955-1690

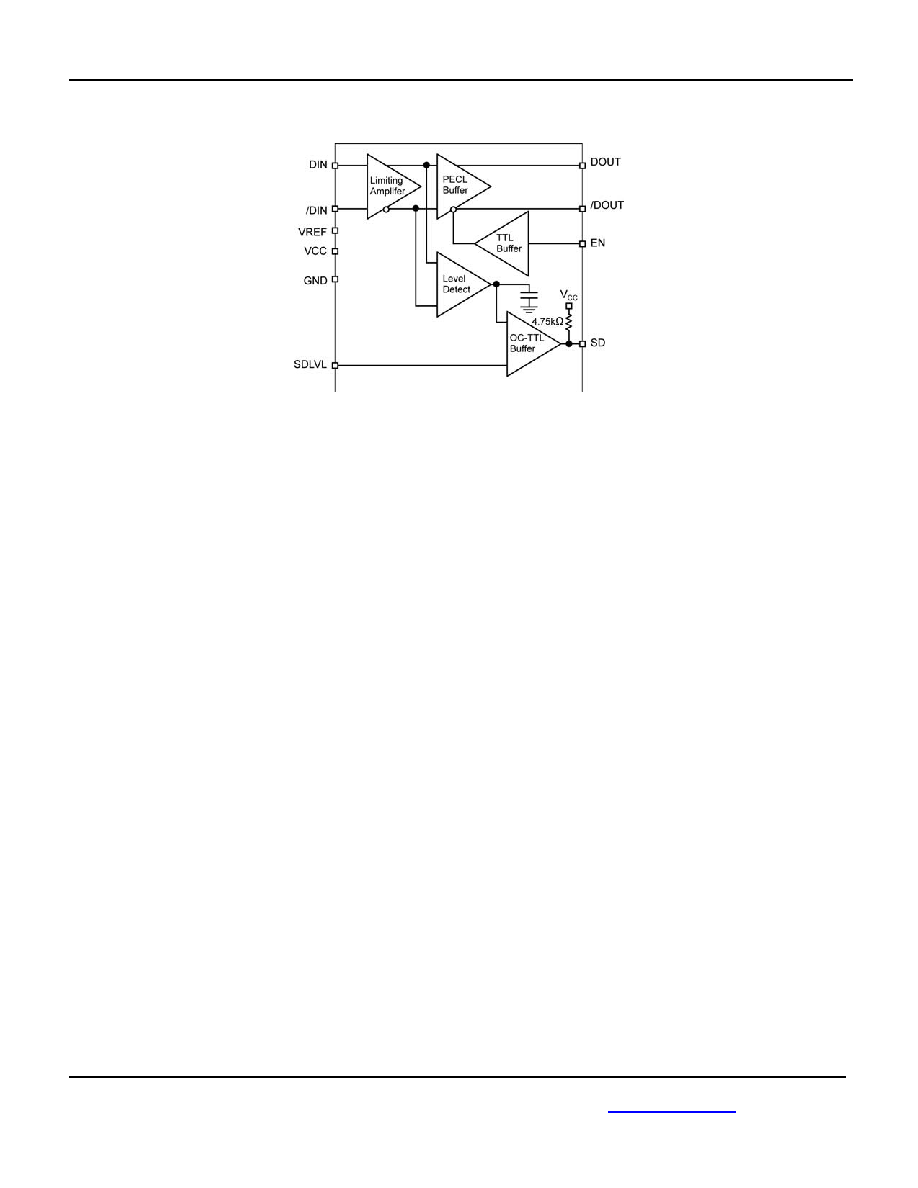

Functional Block Diagram

Detailed Description

The SY88149CL high-sensitivity limiting post amplifier

operates from a single +3.3V power supply, over

temperatures from –40°C to +85°C. Signals with data

rates up to 1.25Gbps and as small as 5mVPP can be

amplified. Figure 1 shows the allowed input voltage

swing. The SY88149CL generates an SD output,

allowing feedback to EN for output stability. SDLVL sets

the sensitivity of the input amplitude detection.

Input Amplifier/Buffer

Figure 2 shows a simplified schematic of the input

stage. The high-sensitivity of the input amplifier allows

signals as small as 5mVPP to be detected and amplified.

The input amplifier allows input signals as large as

1800mVPP. Input signals are linearly amplified with a

typically 42dB differential voltage gain. Since it is a

limiting amplifier, the SY88149CL outputs typically

1500mVPP voltage-limited waveforms for input signals

that are greater than 12mVPP. Applications requiring the

SY88149CL to operate with high-gain should have the

upstream TIA placed as close as possible to the

SY88149CL’s input pins. This ensures the best

performance of the device.

Output Buffer

The SY88149CL’s PECL output buffer is designed to

drive 50 lines. The output buffer requires appropriate

termination for proper operation. An external 50

resistor to VCC–2V for each output pin provides this.

Figure 3 shows a simplified schematic of the output

stage.

Signal Detect

The SY88149CL generates a chatter-free Signal-Detect

(SD) open-collector TTL output with internal 4.75k pull-

up resistor, as shown in Figure 4. SD is used to

determine that the input amplitude is too small to be

considered a valid input. SD asserts high if the input

amplitude rises above threshold set by SDLVL and de-

asserts low otherwise. SD can be fed back to the enable

(EN) input to maintain output stability under a SDs of

signal condition. EN de-asserts low the true output

signal without removing the input signals. Typically,

3.4dB SD hysteresis is provided to prevent chattering.

Signal Detect Level Set

A programmable SD level set pin (SDLVL) sets the

threshold of the input amplitude detection. Connecting

an external resistor between VCC and SDLVL sets the

voltage at SDLVL. This voltage ranges from VCC to VREF.

The external resistor creates a voltage divider between

VCC and VREF, as shown in Figure 5.

Hysteresis

The SY88149CL provides typically 3.4dB SD electrical

hysteresis. By definition, a power ratio measured in dB

is 10log (power ratio). Power is calculated as V

2

IN/R for

an electrical signal. Hence the same ratio can be stated

as 20log (voltage ratio). While in linear mode, the

electrical voltage input changes linearly with the optical

power and hence the ratios change linearly. Therefore,

the optical hysteresis in dB is half the electrical

hysteresis in dB given in the data sheet. The

SY88149CL is an electrical device; this data sheet

refers to hysteresis in electrical terms. With 3.4dB SD

hysteresis, a voltage factor of 1.5 is required to assert or

de-assert SD.

相关PDF资料 |

PDF描述 |

|---|---|

| MS27484T24B1PA | CONN PLUG 128POS STRAIGHT W/PINS |

| MS27496E11F98SA | CONN RCPT 6POS BOX MNT W/SCKT |

| VI-B4P-MW-B1 | CONVERTER MOD DC/DC 13.8V 100W |

| MAX5387MAUD+T | IC DGTL POT 256POS 50K 14TSSOP |

| M83723/76W2212Y | CONN PLUG 12POS STRAIGHT W/PINS |

相关代理商/技术参数 |

参数描述 |

|---|---|

| ICS873996AYLFT | 功能描述:IC ZD/MULT/DIVIDER 48-LQFP RoHS:是 类别:集成电路 (IC) >> 时钟/计时 - 时钟发生器,PLL,频率合成器 系列:HiPerClockS™ 标准包装:1,000 系列:- 类型:时钟/频率合成器,扇出分配 PLL:- 输入:- 输出:- 电路数:- 比率 - 输入:输出:- 差分 - 输入:输出:- 频率 - 最大:- 除法器/乘法器:- 电源电压:- 工作温度:- 安装类型:表面贴装 封装/外壳:56-VFQFN 裸露焊盘 供应商设备封装:56-VFQFP-EP(8x8) 包装:带卷 (TR) 其它名称:844S012AKI-01LFT |

| ICS874001AGI-02LF | 功能描述:IC PCI EXPRSS/JITT ATTEN 20TSSOP RoHS:是 类别:集成电路 (IC) >> 时钟/计时 - 专用 系列:FemtoClock™, PCI Express™ (PCIe) 标准包装:1,500 系列:- 类型:时钟缓冲器/驱动器 PLL:是 主要目的:- 输入:- 输出:- 电路数:- 比率 - 输入:输出:- 差分 - 输入:输出:- 频率 - 最大:- 电源电压:3.3V 工作温度:0°C ~ 70°C 安装类型:表面贴装 封装/外壳:28-SSOP(0.209",5.30mm 宽) 供应商设备封装:28-SSOP 包装:带卷 (TR) 其它名称:93786AFT |

| ICS874001AGI-02LFT | 功能描述:IC PCI EXPRSS/JITT ATTEN 20TSSOP RoHS:是 类别:集成电路 (IC) >> 时钟/计时 - 专用 系列:FemtoClock™, PCI Express™ (PCIe) 标准包装:1,500 系列:- 类型:时钟缓冲器/驱动器 PLL:是 主要目的:- 输入:- 输出:- 电路数:- 比率 - 输入:输出:- 差分 - 输入:输出:- 频率 - 最大:- 电源电压:3.3V 工作温度:0°C ~ 70°C 安装类型:表面贴装 封装/外壳:28-SSOP(0.209",5.30mm 宽) 供应商设备封装:28-SSOP 包装:带卷 (TR) 其它名称:93786AFT |

| ICS874001AGI-05LF | 功能描述:IC PCI EXPRSS/JITT ATTEN 20TSSOP RoHS:是 类别:集成电路 (IC) >> 时钟/计时 - 专用 系列:FemtoClock™, PCI Express™ (PCIe) 标准包装:1 系列:- 类型:时钟/频率发生器,多路复用器 PLL:是 主要目的:存储器,RDRAM 输入:晶体 输出:LVCMOS 电路数:1 比率 - 输入:输出:1:2 差分 - 输入:输出:无/是 频率 - 最大:400MHz 电源电压:3 V ~ 3.6 V 工作温度:0°C ~ 85°C 安装类型:表面贴装 封装/外壳:16-TSSOP(0.173",4.40mm 宽) 供应商设备封装:16-TSSOP 包装:Digi-Reel® 其它名称:296-6719-6 |

| ICS874001AGI-05LFT | 功能描述:IC PCI EXPRSS/JITT ATTEN 20TSSOP RoHS:是 类别:集成电路 (IC) >> 时钟/计时 - 专用 系列:FemtoClock™, PCI Express™ (PCIe) 标准包装:1,500 系列:- 类型:时钟缓冲器/驱动器 PLL:是 主要目的:- 输入:- 输出:- 电路数:- 比率 - 输入:输出:- 差分 - 输入:输出:- 频率 - 最大:- 电源电压:3.3V 工作温度:0°C ~ 70°C 安装类型:表面贴装 封装/外壳:28-SSOP(0.209",5.30mm 宽) 供应商设备封装:28-SSOP 包装:带卷 (TR) 其它名称:93786AFT |

发布紧急采购,3分钟左右您将得到回复。