- 您现在的位置:买卖IC网 > PDF目录67703 > ICS87946AYI-01T LOW SKEW CLOCK DRIVER, 10 TRUE OUTPUT(S), 0 INVERTED OUTPUT(S), PQFP32 PDF资料下载

参数资料

| 型号: | ICS87946AYI-01T |

| 元件分类: | 时钟及定时 |

| 英文描述: | LOW SKEW CLOCK DRIVER, 10 TRUE OUTPUT(S), 0 INVERTED OUTPUT(S), PQFP32 |

| 封装: | 7 X 7 MM, 1.40 MM HEIGHT, MS-026, LQFP-32 |

| 文件页数: | 1/12页 |

| 文件大小: | 255K |

| 代理商: | ICS87946AYI-01T |

87946AYI-01

www.icst.com/products/hiperclocks.html

REV. A NOVEMBER 21, 2003

1

Integrated

Circuit

Systems, Inc.

ICS87946I-01

LOW SKEW,

÷1, ÷2

LVPECL-TO-LVCMOS/LVTTL CLOCK GENERATOR

GENERAL DESCRIPTION

The ICS87946I-01 is a low skew, ÷1, ÷2 Clock

Generator and a member of the HiPerClockS

family of High Performance Clock Solutions from

ICS. The ICS87946I-01 has one LVPECL clock

input pair. The PCLK, nPCLK pair can accept

LVPECL, CML, or SSTL input levels. The low impedance

LVCMOS/LVTTL outputs are designed to drive 50

series or

parallel terminated transmission lines. The effective fanout can

be increased from 10 to 20 by utilizing the ability of the out-

puts to drive two series terminated lines.

The divide select inputs, DIV_SELx, control the output fre-

quency of each bank. The outputs can be utilized in the ÷1,

÷2 or a combination of ÷1 and ÷2 modes. The master reset

input, MR/nOE, resets the internal frequency dividers and also

controls the active and high impedance states of all outputs.

The ICS87946I-01 is characterized at 3.3V core/3.3V output

and 3.3V core/2.5V output. Guaranteed bank, output and part-

to-part skew characteristics make the ICS87946I-01 ideal for

those clock distribution applications demanding well defined

performance and repeatability.

FEATURES

10 single ended LVCMOS/LVTTL outputs,

7

typical output impedance

LVPECL clock input pair

PCLK, nPCLK supports the following input levels:

LVPECL, CML, SSTL

Maximum input frequency: 250MHz

Output skew: 120ps (maximum)

Part-to-part skew: 700ps (maximum)

Multiple frequency skew: 320ps (maximum)

3.3V core, 3.3V or 2.5V output supply modes

-40°C to 85°C ambient operating temperature

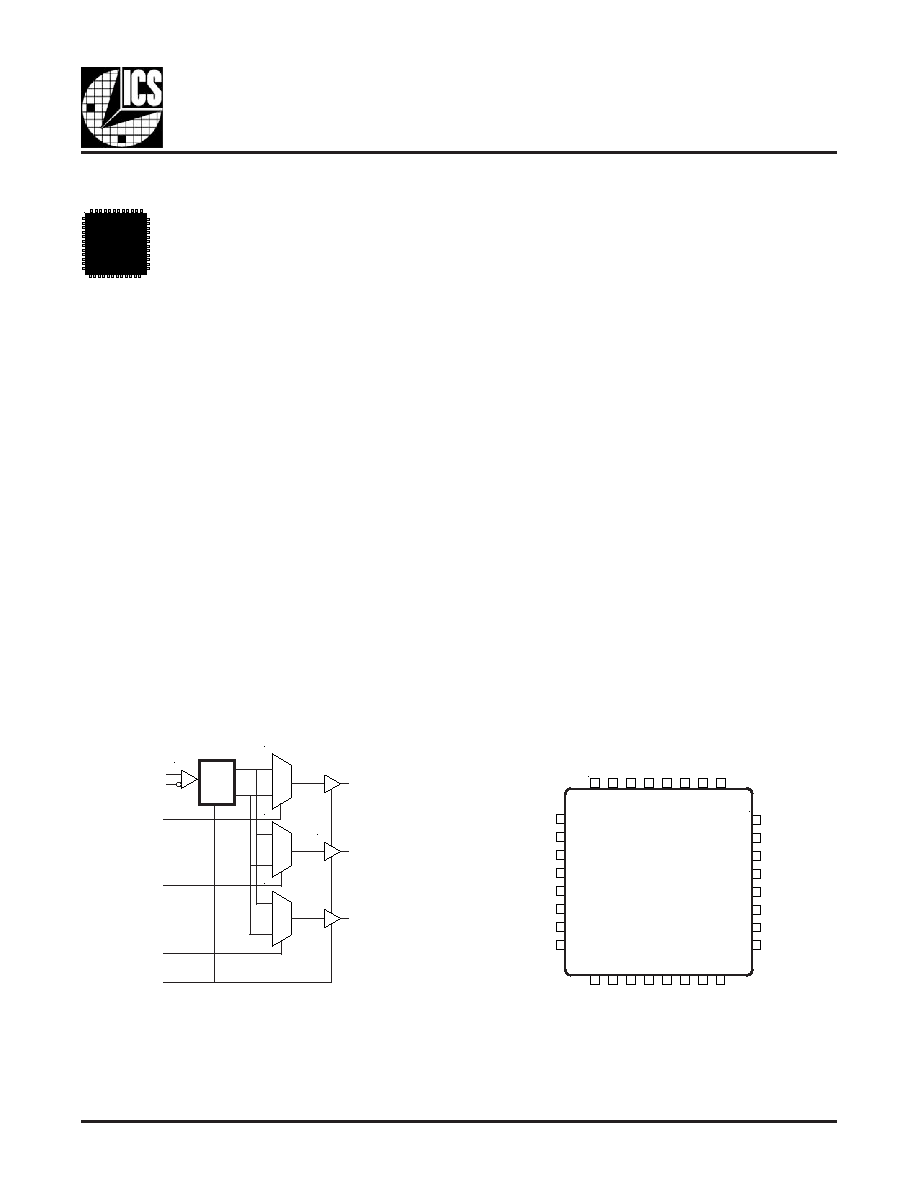

BLOCK DIAGRAM

PIN ASSIGNMENT

DIV_SELA

DIV_SELB

DIV_SELC

MR/nOE

QA0:QA2

QB0:QB2

QC0:QC3

PCLK

nPCLK

32-Lead LQFP

7mm x 7mm x 1.4mm package body

Y Package

Top View

HiPerClockS

ICS

0

1

÷1

÷2

0

1

0

1

32 31 30 29 28 27 26 25

9

10 11 12 13 14 15 16

1

2

3

4

5

6

7

8

24

23

22

21

20

19

18

17

GND

QB0

VDDB

QB1

GND

QB2

VDDB

VDDC

nc

VDD

PCLK

nPCLK

DIV_SELA

DIV_SELB

DIV_SELC

GND

QC3

GND

QC2

V

DDC

QC1

GND

QC0

V

DDC

V

DDA

QA2

GND

QA1

V

DDA

QA0

GND

MR/nOE

ICS87946I-01

相关PDF资料 |

PDF描述 |

|---|---|

| ICS87949AY-01LF | LOW SKEW CLOCK DRIVER, 15 TRUE OUTPUT(S), 0 INVERTED OUTPUT(S), PQFP48 |

| ICS87949AY-01 | LOW SKEW CLOCK DRIVER, 15 TRUE OUTPUT(S), 0 INVERTED OUTPUT(S), PQFP48 |

| ICS87949AY-01LFT | LOW SKEW CLOCK DRIVER, 15 TRUE OUTPUT(S), 0 INVERTED OUTPUT(S), PQFP48 |

| ICS87949AY-01T | LOW SKEW CLOCK DRIVER, 15 TRUE OUTPUT(S), 0 INVERTED OUTPUT(S), PQFP48 |

| ICS87949AY-01 | LOW SKEW CLOCK DRIVER, 15 TRUE OUTPUT(S), 0 INVERTED OUTPUT(S), PQFP48 |

相关代理商/技术参数 |

参数描述 |

|---|---|

| ICS87946AYI-147 | 制造商:Integrated Device Technology Inc 功能描述:IC CLOCK DIVIDER 32LQFP |

| ICS87946AYI-147LF | 功能描述:IC CLOCK GENERATOR 32-LQFP RoHS:是 类别:集成电路 (IC) >> 时钟/计时 - 时钟发生器,PLL,频率合成器 系列:HiPerClockS™ 标准包装:1,000 系列:- 类型:时钟/频率合成器,扇出分配 PLL:- 输入:- 输出:- 电路数:- 比率 - 输入:输出:- 差分 - 输入:输出:- 频率 - 最大:- 除法器/乘法器:- 电源电压:- 工作温度:- 安装类型:表面贴装 封装/外壳:56-VFQFN 裸露焊盘 供应商设备封装:56-VFQFP-EP(8x8) 包装:带卷 (TR) 其它名称:844S012AKI-01LFT |

| ICS87946AYI-147LFT | 功能描述:IC CLOCK GENERATOR 32-LQFP RoHS:是 类别:集成电路 (IC) >> 时钟/计时 - 时钟发生器,PLL,频率合成器 系列:HiPerClockS™ 标准包装:1,000 系列:- 类型:时钟/频率合成器,扇出分配 PLL:- 输入:- 输出:- 电路数:- 比率 - 输入:输出:- 差分 - 输入:输出:- 频率 - 最大:- 除法器/乘法器:- 电源电压:- 工作温度:- 安装类型:表面贴装 封装/外壳:56-VFQFN 裸露焊盘 供应商设备封装:56-VFQFP-EP(8x8) 包装:带卷 (TR) 其它名称:844S012AKI-01LFT |

| ICS87946AYI-147T | 制造商:Integrated Device Technology Inc 功能描述:IC CLOCK DIVIDER 32LQFP |

| ICS87946AYILF | 功能描述:IC CLK GEN LVCMOS /1 /2 32-LQFP RoHS:是 类别:集成电路 (IC) >> 时钟/计时 - 时钟发生器,PLL,频率合成器 系列:HiPerClockS™ 标准包装:2,000 系列:- 类型:PLL 频率合成器 PLL:是 输入:晶体 输出:时钟 电路数:1 比率 - 输入:输出:1:1 差分 - 输入:输出:无/无 频率 - 最大:1GHz 除法器/乘法器:是/无 电源电压:4.5 V ~ 5.5 V 工作温度:-20°C ~ 85°C 安装类型:表面贴装 封装/外壳:16-LSSOP(0.175",4.40mm 宽) 供应商设备封装:16-SSOP 包装:带卷 (TR) 其它名称:NJW1504V-TE1-NDNJW1504V-TE1TR |

发布紧急采购,3分钟左右您将得到回复。