- 您现在的位置:买卖IC网 > PDF目录1999 > ICS87973DYILFT (IDT, Integrated Device Technology Inc)IC CLK MULT/ZD BUFFER 52-LQFP PDF资料下载

参数资料

| 型号: | ICS87973DYILFT |

| 厂商: | IDT, Integrated Device Technology Inc |

| 文件页数: | 2/17页 |

| 文件大小: | 0K |

| 描述: | IC CLK MULT/ZD BUFFER 52-LQFP |

| 标准包装: | 500 |

| 系列: | HiPerClockS™ |

| 类型: | 时钟倍频器,零延迟缓冲器 |

| PLL: | 带旁路 |

| 输入: | HCSL,LVCMOS,LVDS,LVHSTL,LVPECL,LVTTL,SSTL |

| 输出: | LVCMOS,LVTTL |

| 电路数: | 1 |

| 比率 - 输入:输出: | 4:12 |

| 差分 - 输入:输出: | 是/无 |

| 频率 - 最大: | 125MHz |

| 除法器/乘法器: | 是/无 |

| 电源电压: | 3.135 V ~ 3.465 V |

| 工作温度: | -40°C ~ 85°C |

| 安装类型: | 表面贴装 |

| 封装/外壳: | 52-LQFP |

| 供应商设备封装: | 52-TQFP(10x10) |

| 包装: | 带卷 (TR) |

| 其它名称: | 87973DYILFT |

87973DYI

www.idt.com

REV. D AUGUST 11, 2010

10

ICS87973I

LOW SKEW, 1-TO-12

LVCMOS / LVTTL CLOCK MULTIPLIER/ZERO DELAY BUFFER

FRZ

Latched

FRZ

Cloc

k

e

d

Qx FREEZE Internal

Qx Internal

Qx Out

FRZ_CLK

FRZ_DATA

Star

t

Bit

QA0

QA1

QA2

QA3

QB0

QB1

QB2

QB3

QC1

QC2

QC3 QSYNC

APPLICATION INFORMATION

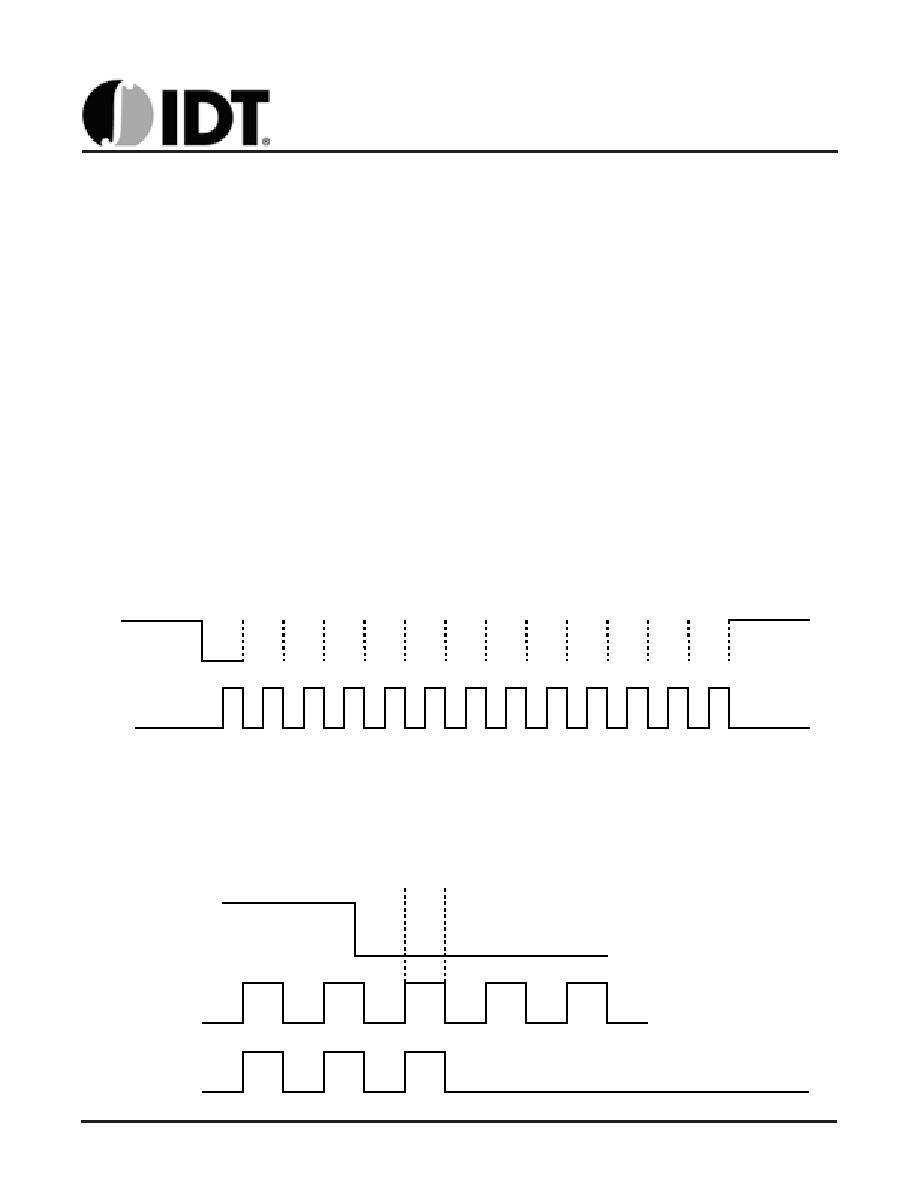

FIGURE 2A. FREEZE DATA INPUT PROTOCOL

USING THE OUTPUT FREEZE CIRCUITRY

OVERVIEW

To enable low power states within a system, each output of

ICS87973I (Except QC0 and QFB) can be individually frozen

(stopped in the logic “0” state) using a simple serial interface

to a 12 bit shift register. A serial interface was chosen to elimi-

nate the need for each output to have its own Output Enable

pin, which would dramatically increase pin count and package

cost. Common sources in a system that can be used to drive

the ICS87973I serial interface are FPGA’s and ASICs.

PROTOCOL

The Serial interface consists of two pins, FRZ_Data (Freeze

Data) and FRZ_CLK (Freeze Clock). Each of the outputs which

can be frozen has its own freeze enable bit in the 12 bit shift

register. The sequence is started by supplying a logic “0” start

bit followed by 12NRZ freeze enable bits. The period of each

FRZ_DATA bit equals the period of the FRZ_CLK signal. The

FRZ_DATA serial transmission should be timed so the ICS87973I

can sample each FRZ_DATA bit with the rising edge of the

FRZ_CLK signal. To place an output in the freeze state, a logic

“0” must be written to the respective freeze enable bit in the shift

register. To unfreeze an output, a logic “1” must be written to the

respective freeze enable bit. Outputs will not become enabled/

disabled until all 12 data bits are shifted into the shift register.

When all 12 data bits are shifted in the register, the next rising

edge of FRZ_CLK will enable or disable the outputs. If the bit

that is following the 12th bit in the register is a logic “0”, it is used

for the start bit of the next cycle; otherwise, the device will wait

and won’t start the next cycle until it sees a logic “0” bit. Freez-

ing and unfreezing of the output clock is synchronous (see the

timing diagram below). When going into a frozen state, the out-

put clock will go LOW at the time it would normally go LOW, and

the freeze logic will keep the output low until unfrozen. Likewise,

when coming out of the frozen state, the output will go HIGH

only when it would normally go HIGH. This logic, therefore, pre-

vents runt pulses when going into and out of the frozen state.

FIGURE 2B. OUTPUT DISABLE TIMING

相关PDF资料 |

PDF描述 |

|---|---|

| ICS87974CYILF | IC CLK GEN LVCMOS/LVTTL 52-LQFP |

| ICS894D115AGI-04LF | IC CLK/DATA RECOVERY 20-TSSOP |

| ICS894D115BGI-01LF | IC CLK/DATA RECOVERY 20-TSSOP |

| ICS9112AM-17LF | IC BUFFER HI PERFORMANCE 16-SOIC |

| ICS91305AMILF | IC CLOCK DRIVER LO JITTER 8-SOIC |

相关代理商/技术参数 |

参数描述 |

|---|---|

| ICS87974CYILF | 功能描述:IC CLK GEN LVCMOS/LVTTL 52-LQFP RoHS:是 类别:集成电路 (IC) >> 时钟/计时 - 时钟发生器,PLL,频率合成器 系列:HiPerClockS™ 标准包装:1,000 系列:- 类型:时钟/频率合成器,扇出分配 PLL:- 输入:- 输出:- 电路数:- 比率 - 输入:输出:- 差分 - 输入:输出:- 频率 - 最大:- 除法器/乘法器:- 电源电压:- 工作温度:- 安装类型:表面贴装 封装/外壳:56-VFQFN 裸露焊盘 供应商设备封装:56-VFQFP-EP(8x8) 包装:带卷 (TR) 其它名称:844S012AKI-01LFT |

| ICS87974CYILFT | 功能描述:IC CLOCK GEN 1-15 PLL 52-LQFP RoHS:是 类别:集成电路 (IC) >> 时钟/计时 - 时钟发生器,PLL,频率合成器 系列:HiPerClockS™ 标准包装:1,000 系列:- 类型:时钟/频率合成器,扇出分配 PLL:- 输入:- 输出:- 电路数:- 比率 - 输入:输出:- 差分 - 输入:输出:- 频率 - 最大:- 除法器/乘法器:- 电源电压:- 工作温度:- 安装类型:表面贴装 封装/外壳:56-VFQFN 裸露焊盘 供应商设备封装:56-VFQFP-EP(8x8) 包装:带卷 (TR) 其它名称:844S012AKI-01LFT |

| ICS879893AYILF | 功能描述:IC CLK GEN LVCMOS/LVTTL 48-LQFP RoHS:是 类别:集成电路 (IC) >> 时钟/计时 - 时钟发生器,PLL,频率合成器 系列:HiPerClockS™ 标准包装:1,000 系列:- 类型:时钟/频率合成器,扇出分配 PLL:- 输入:- 输出:- 电路数:- 比率 - 输入:输出:- 差分 - 输入:输出:- 频率 - 最大:- 除法器/乘法器:- 电源电压:- 工作温度:- 安装类型:表面贴装 封装/外壳:56-VFQFN 裸露焊盘 供应商设备封装:56-VFQFP-EP(8x8) 包装:带卷 (TR) 其它名称:844S012AKI-01LFT |

| ICS879893AYILFT | 功能描述:IC CLK GEN LVCMOS/LVTTL 48-LQFP RoHS:是 类别:集成电路 (IC) >> 时钟/计时 - 时钟发生器,PLL,频率合成器 系列:HiPerClockS™ 标准包装:1,000 系列:- 类型:时钟/频率合成器,扇出分配 PLL:- 输入:- 输出:- 电路数:- 比率 - 输入:输出:- 差分 - 输入:输出:- 频率 - 最大:- 除法器/乘法器:- 电源电压:- 工作温度:- 安装类型:表面贴装 封装/外壳:56-VFQFN 裸露焊盘 供应商设备封装:56-VFQFP-EP(8x8) 包装:带卷 (TR) 其它名称:844S012AKI-01LFT |

| ICS87993AYILF | 功能描述:IC PLL CLK DRIVER 1-5 32-LQFP RoHS:是 类别:集成电路 (IC) >> 时钟/计时 - 时钟发生器,PLL,频率合成器 系列:HiPerClockS™ 标准包装:1,000 系列:- 类型:时钟/频率合成器,扇出分配 PLL:- 输入:- 输出:- 电路数:- 比率 - 输入:输出:- 差分 - 输入:输出:- 频率 - 最大:- 除法器/乘法器:- 电源电压:- 工作温度:- 安装类型:表面贴装 封装/外壳:56-VFQFN 裸露焊盘 供应商设备封装:56-VFQFP-EP(8x8) 包装:带卷 (TR) 其它名称:844S012AKI-01LFT |

发布紧急采购,3分钟左右您将得到回复。