- 您现在的位置:买卖IC网 > PDF目录67704 > ICS87973DYIT PLL BASED CLOCK DRIVER, 13 TRUE OUTPUT(S), 0 INVERTED OUTPUT(S), PQFP52 PDF资料下载

参数资料

| 型号: | ICS87973DYIT |

| 元件分类: | 时钟及定时 |

| 英文描述: | PLL BASED CLOCK DRIVER, 13 TRUE OUTPUT(S), 0 INVERTED OUTPUT(S), PQFP52 |

| 封装: | 10 X 10 MM, 1.40 MM HEIGHT, MS-026, LQFP-52 |

| 文件页数: | 1/16页 |

| 文件大小: | 170K |

| 代理商: | ICS87973DYIT |

87973DYI

www.icst.com/products/hiperclocks.html

REV. D MAY 19, 2006

1

Integrated

Circuit

Systems, Inc.

ICS87973I

LOW SKEW, 1-TO-12

LVCMOS / LVTTL CLOCK MULTIPLIER/ZERO DELAY BUFFER

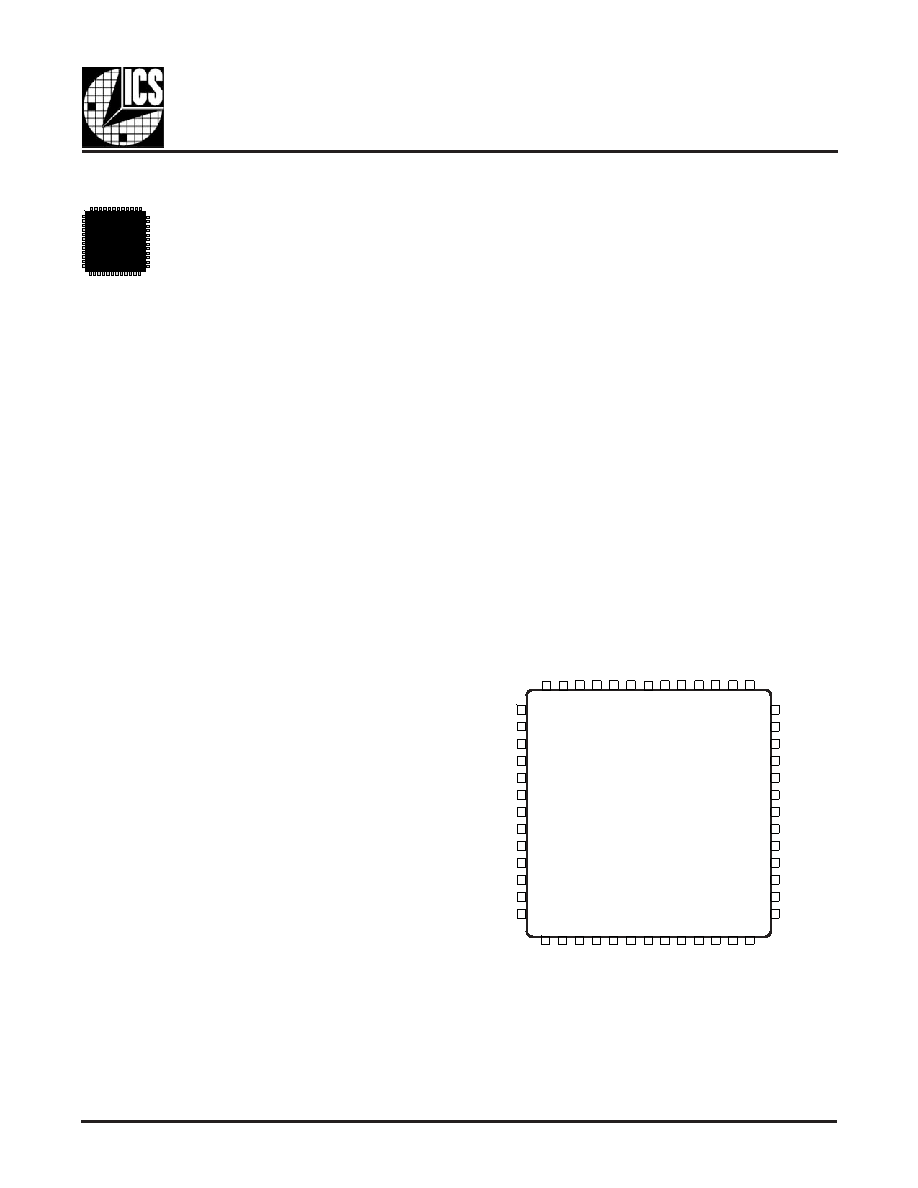

PIN ASSIGNMENT

GENERAL DESCRIPTION

The ICS87973I is a LVCMOS/LVTTL clock gen-

erator and a member of the HiPerClockSfamily

of High Performance Clock Solutions from ICS.

The ICS87973I has three selectable inputs and

provides fourteen LVCMOS/LVTTL outputs.

The ICS87973I is a highly flexible device. The three selectable

inputs (1 differential and 2 single ended inputs) are often used

in systems requiring redundant clock sources. Up to three dif-

ferent output frequencies can be generated among the three

output banks.

The three output banks and feedback output each have their

own output dividers which allows the device to generate a

multitude of different bank frequency ratios and output-to-input

frequency ratios. In addition, 2 outputs in Bank C (QC2, QC3)

can be selected to be inverting or non-inverting. The output fre-

quency range is 8.33MHz to125MHz. The input frequency range

is 5MHz to 120MHz.

The ICS87973I also has a QSYNC output which can by used

for system synchronization purposes. It monitors Bank A and

Bank C outputs and goes low one period prior to coincident

rising edges of Bank A and Bank C clocks. QSYNC then goes

high again when the coincident rising edges of Bank A and

Bank C occur.This feature is used primarily in applications where

Bank A and Bank C are running at different frequencies, and is

particularly useful when they are running at non-integer mul-

tiples of one another.

Example Applications:

1. System Clock generator: Use a 16.66MHz reference

clock to generate eight 33.33MHz copies for PCI and

four 100MHz copies for the CPU or PCI-X.

2. Line Card Multiplier: Multiply differential 62.5MHz from

a back plane to single-ended 125MHz for the line Card

ASICs and Gigabit Ethernet Serdes.

3. Zero Delay buffer for Synchronous memory: Fan out

up to twelve 100MHz copies from a memory controller

reference clock to the memory chips on a memory module

with zero delay.

FEATURES

Fully integrated PLL

Fourteen LVCMOS/LVTTL outputs; twelve clock outputs,

one feedback, one sync

Selectable LVCMOS/LVTTL or differential CLK, nCLK inputs

CLK0, CLK1 can accept the following input levels:

LVCMOS or LVTTL

CLK, nCLK pair can accept the following differential

input levels: LVPECL, LVDS, LVHSTL, SSTL, HCSL

Output frequency range: 8.33MHz to 125MHz

VCO range: 200MHz to 480MHz

Output skew: 550ps (maximum)

Cycle-to-cycle jitter: ±100ps (typical)

Full 3.3V supply voltage

-40°C to 85°C ambient operating temperature

Available in both standard and lead-free RoHS compliant

packages

Compatible with PowerPCandPentium Microprocessors

HiPerClockS

ICS

FSEL_FB0

V

DD

QFB

GNDO

EXT_FB

QB3

V

DDO

QB2

GNDO

QB1

V

DDO

QB0

GNDO

40

41

42

43

44

45

46

47

48

49

50

51

52

1

2

3

4

5 6

7

8

9 10 11 12 13

26

25

24

23

22

21

20

19

18

17

16

15

14

39 38 37 36 35 34 33 32 31 30 29 28 27

FSEL_B1

FSEL_B0

FSEL_A1

FSEL_A0

QA3

VDDO

QA2

GNDO

QA1

VDDO

QA0

GNDO

VCO_SEL

FSEL_FB1

QSYNC

GNDO

QC0

VDDO

QC1

FSEL_C0

FSEL_C1

QC2

VDDO

QC3

GNDO

INV_CLK

V

DDA

nCLK

CLK

CLK1

CLK0

CLK_SEL

REF_SEL

PLL_SEL

FSEL_FB2

FRZ_D

A

T

A

FRZ_CLK

nMR/OE

GNDI

52-Lead LQFP

10mm x 10mm x 1.4mm package body

Y package

Top View

ICS87973I

相关PDF资料 |

PDF描述 |

|---|---|

| ICS87974AY-01LF | PLL BASED CLOCK DRIVER, 15 TRUE OUTPUT(S), 0 INVERTED OUTPUT(S), PQFP52 |

| ICS87974AYI-01 | PLL BASED CLOCK DRIVER, 14 TRUE OUTPUT(S), 0 INVERTED OUTPUT(S), PQFP52 |

| ICS87974AYI-01LFT | PLL BASED CLOCK DRIVER, 14 TRUE OUTPUT(S), 0 INVERTED OUTPUT(S), PQFP52 |

| ICS87974AYI | PLL BASED CLOCK DRIVER, 14 TRUE OUTPUT(S), 0 INVERTED OUTPUT(S), PQFP52 |

| ICS87974AYI | PLL BASED CLOCK DRIVER, 14 TRUE OUTPUT(S), 0 INVERTED OUTPUT(S), PQFP52 |

相关代理商/技术参数 |

参数描述 |

|---|---|

| ICS87974CYILF | 功能描述:IC CLK GEN LVCMOS/LVTTL 52-LQFP RoHS:是 类别:集成电路 (IC) >> 时钟/计时 - 时钟发生器,PLL,频率合成器 系列:HiPerClockS™ 标准包装:1,000 系列:- 类型:时钟/频率合成器,扇出分配 PLL:- 输入:- 输出:- 电路数:- 比率 - 输入:输出:- 差分 - 输入:输出:- 频率 - 最大:- 除法器/乘法器:- 电源电压:- 工作温度:- 安装类型:表面贴装 封装/外壳:56-VFQFN 裸露焊盘 供应商设备封装:56-VFQFP-EP(8x8) 包装:带卷 (TR) 其它名称:844S012AKI-01LFT |

| ICS87974CYILFT | 功能描述:IC CLOCK GEN 1-15 PLL 52-LQFP RoHS:是 类别:集成电路 (IC) >> 时钟/计时 - 时钟发生器,PLL,频率合成器 系列:HiPerClockS™ 标准包装:1,000 系列:- 类型:时钟/频率合成器,扇出分配 PLL:- 输入:- 输出:- 电路数:- 比率 - 输入:输出:- 差分 - 输入:输出:- 频率 - 最大:- 除法器/乘法器:- 电源电压:- 工作温度:- 安装类型:表面贴装 封装/外壳:56-VFQFN 裸露焊盘 供应商设备封装:56-VFQFP-EP(8x8) 包装:带卷 (TR) 其它名称:844S012AKI-01LFT |

| ICS879893AYILF | 功能描述:IC CLK GEN LVCMOS/LVTTL 48-LQFP RoHS:是 类别:集成电路 (IC) >> 时钟/计时 - 时钟发生器,PLL,频率合成器 系列:HiPerClockS™ 标准包装:1,000 系列:- 类型:时钟/频率合成器,扇出分配 PLL:- 输入:- 输出:- 电路数:- 比率 - 输入:输出:- 差分 - 输入:输出:- 频率 - 最大:- 除法器/乘法器:- 电源电压:- 工作温度:- 安装类型:表面贴装 封装/外壳:56-VFQFN 裸露焊盘 供应商设备封装:56-VFQFP-EP(8x8) 包装:带卷 (TR) 其它名称:844S012AKI-01LFT |

| ICS879893AYILFT | 功能描述:IC CLK GEN LVCMOS/LVTTL 48-LQFP RoHS:是 类别:集成电路 (IC) >> 时钟/计时 - 时钟发生器,PLL,频率合成器 系列:HiPerClockS™ 标准包装:1,000 系列:- 类型:时钟/频率合成器,扇出分配 PLL:- 输入:- 输出:- 电路数:- 比率 - 输入:输出:- 差分 - 输入:输出:- 频率 - 最大:- 除法器/乘法器:- 电源电压:- 工作温度:- 安装类型:表面贴装 封装/外壳:56-VFQFN 裸露焊盘 供应商设备封装:56-VFQFP-EP(8x8) 包装:带卷 (TR) 其它名称:844S012AKI-01LFT |

| ICS87993AYILF | 功能描述:IC PLL CLK DRIVER 1-5 32-LQFP RoHS:是 类别:集成电路 (IC) >> 时钟/计时 - 时钟发生器,PLL,频率合成器 系列:HiPerClockS™ 标准包装:1,000 系列:- 类型:时钟/频率合成器,扇出分配 PLL:- 输入:- 输出:- 电路数:- 比率 - 输入:输出:- 差分 - 输入:输出:- 频率 - 最大:- 除法器/乘法器:- 电源电压:- 工作温度:- 安装类型:表面贴装 封装/外壳:56-VFQFN 裸露焊盘 供应商设备封装:56-VFQFP-EP(8x8) 包装:带卷 (TR) 其它名称:844S012AKI-01LFT |

发布紧急采购,3分钟左右您将得到回复。