- 您现在的位置:买卖IC网 > PDF目录9063 > ICS9112BM-17LFT (IDT, Integrated Device Technology Inc)IC BUFFER ZD HI PERFORM 16-SOIC PDF资料下载

参数资料

| 型号: | ICS9112BM-17LFT |

| 厂商: | IDT, Integrated Device Technology Inc |

| 文件页数: | 4/8页 |

| 文件大小: | 0K |

| 描述: | IC BUFFER ZD HI PERFORM 16-SOIC |

| 标准包装: | 2,500 |

| 类型: | 零延迟缓冲器 |

| PLL: | 带旁路 |

| 输入: | 时钟 |

| 输出: | 时钟 |

| 电路数: | 1 |

| 比率 - 输入:输出: | 1:9 |

| 差分 - 输入:输出: | 无/无 |

| 频率 - 最大: | 133MHz |

| 除法器/乘法器: | 无/无 |

| 电源电压: | 2.97 V ~ 5.5 V |

| 工作温度: | 0°C ~ 70°C |

| 安装类型: | 表面贴装 |

| 封装/外壳: | 16-SOIC(0.154",3.90mm 宽) |

| 供应商设备封装: | 16-SOIC |

| 包装: | 带卷 (TR) |

| 其它名称: | 9112BM-17LFT |

4

ICS9112-17

0051K—11/02/04

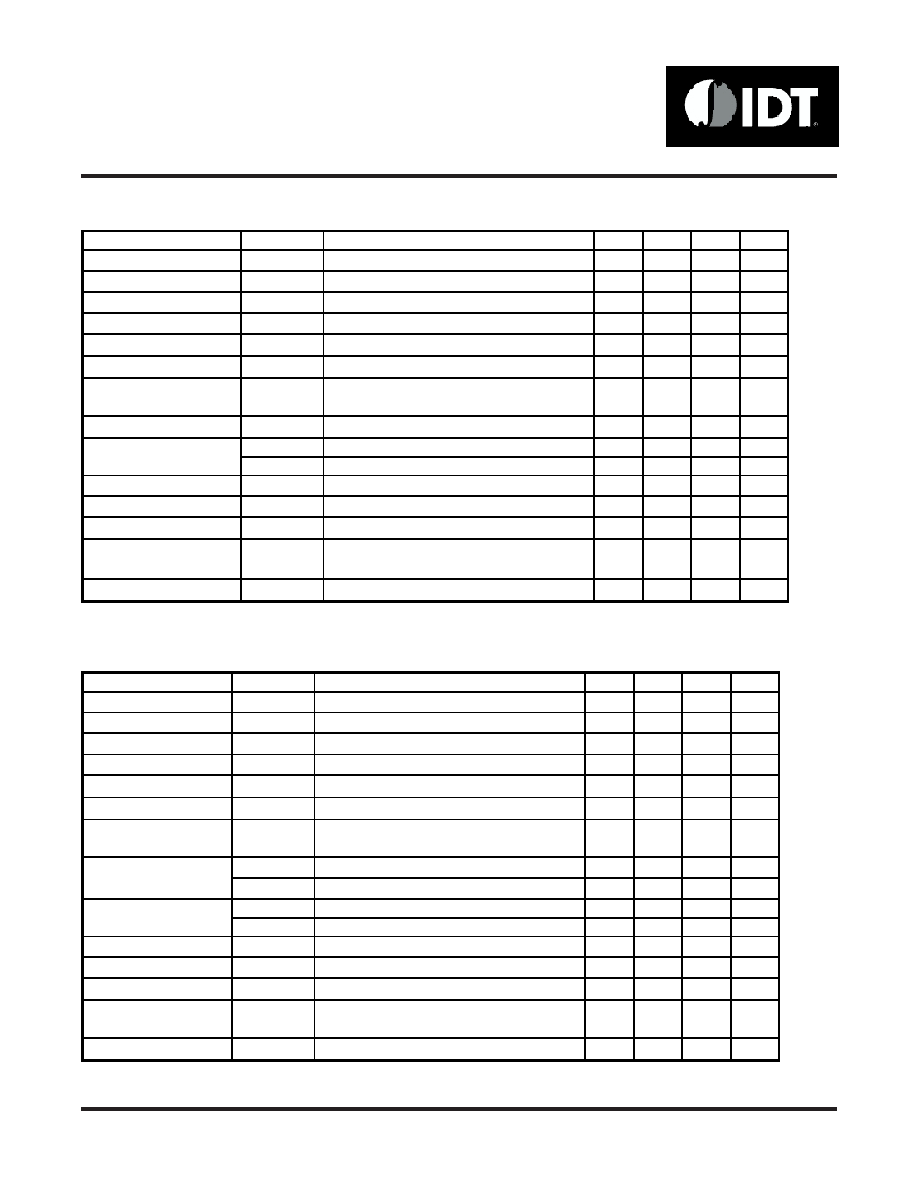

Electrical Characteristics - OUTPUT

TA = 0 - 70°C; VDD = VDDL = 3.3 V +/-10%; CL = 20 - 30 pF (unless otherwise stated)

PARAMETER

SYMBOL

CONDITIONS

MIN

TYP

MAX UNITS

Output Impedance

RDSP

VO = VDD*(0.5)

10

24

Output Impedance

RDSN

VO = VDD*(0.5)

10

24

Output High Voltage

VOH

IOH = -8 mA

2.4

2.9

3.3

V

Output Low Voltage

VOL

IOL = 8 mA

0.25

0.4

V

Rise Time

1

Tr

VOL = 0.8 V, VOH = 2.0 V

1.2

2.0

ns

Fall Time

1

Tf

VOH = 2.0 V, VOL = 0.8 V

1.2

2.0

ns

PLL Lock Time1

tLOCK

Stable power supply, valid clock

presented on REF pin

1.0

ms

Dt

VT = 1.4V;Cl=30pF

40

50

60

%

Dt

VT = Vdd/2; Fout <66.6MHz

45

50

55

%

Tcyc-cyc

at 66MHz , Loaded Outputs

250

ps

Tcyc-cyc

>66MHz , Loaded Outputs

200

ps

Absolute Jitter

1

Tjabs

10000 cycles; Cl=30pF

-100

70

100

ps

Jitter; 1-Sigma

1

Tj1s

10000 cycles; Cl=30pF

14

30

ps

Skew

1

Tsk

VT = 1.4 V (Window) Output to Output

250

ps

Device to Device Skew

1 Tdsk-Tdsk

Measured at VDD/2 on the CLKOUT

pins of devices

0700

ps

Delay Input-Output

1

DR1

VT = 1.4 V

0700

ps

1 Guaranteed by design, not 100% tested in production.

Cycle to Cycle jitter

1

Duty Cycle

1

Electrical Characteristics - OUTPUT

TA = 0 - 70°C; VDD = VDDL = 5.0 V +/-10%; CL = 20 - 30 pF (unless otherwise stated)

PARAMETER

SYMBOL

CONDITIONS

MIN

TYP

MAX UNITS

Output Impedance

RDSP

VO = VDD*(0.5)

10

24

Output Impedance

RDSN

VO = VDD*(0.5)

10

24

Output High Voltage

VOH

IOH = -8 mA

2.4

2.9

5.0

V

Output Low Voltage

VOL

IOL = 8 mA

0.25

0.4

V

Rise Time

1

Tr

VOL = 0.8 V, VOH = 2.0 V

0.8

1.5

ns

Fall Time

1

Tf

VOH = 2.0 V, VOL = 0.8 V

1.0

1.5

ns

PLL Lock Time

1

tLOCK

Stable power supply, valid clock

presented on REF pin

1.0

ms

Duty Cycle

1

Dt

VT = 1.4V;Cl=30pF

40

50

60

%

Tcyc-cyc

at 66MHz , Loaded Outputs

250

ps

Tcyc-cyc

>66MHz , Loaded Outputs

200

ps

Absolute Jitter

1

Tjabs

10000 cycles; Cl=30pF

-100

60

100

ps

Jitter; 1-Sigma

1

Tj1s

10000 cycles; Cl=30pF

14

30

ps

Skew

1

Tsk

VT = 1.4 V (Window) Output to Output

250

ps

Device to Device

Skew

1

Tdsk-Tdsk

Measured at VDD/2 on the CLKOUT

pins of devices

0

700

ps

Delay Input-Output

1

DR1

VT = 1.4 V

0

700

ps

1 Guaranteed by design, not 100% tested in production.

Cycle to Cycle jitter

1

相关PDF资料 |

PDF描述 |

|---|---|

| VI-J1N-MZ-F3 | CONVERTER MOD DC/DC 18.5V 25W |

| ICS9112BF-17LFT | IC BUFFER ZD HI PERFORM 16-SSOP |

| VI-J1N-MZ-F2 | CONVERTER MOD DC/DC 18.5V 25W |

| MK1705ALFTR | IC CLK GEN ATI LOW EMI 8-SOIC |

| VI-J1N-MZ-F1 | CONVERTER MOD DC/DC 18.5V 25W |

相关代理商/技术参数 |

参数描述 |

|---|---|

| ICS9112BM18 | 制造商:ICS 功能描述: |

| ICS9112BM-18 | 制造商:Integrated Device Technology Inc 功能描述:PLL BASED CLOCK DRIVER, 8 TRUE OUTPUT(S), 0 INVERTED OUTPUT(S), PDSO16 |

| ICS9112BM-18T | 制造商:ICS 制造商全称:ICS 功能描述:Zero Delay, Low Skew Buffer |

| ICS9112CM18 | 制造商:ICS 功能描述: |

| ICS9112M-06 | 制造商:Integrated Device Technology Inc 功能描述: |

发布紧急采购,3分钟左右您将得到回复。