- 您现在的位置:买卖IC网 > PDF目录65534 > ICS91309YFLF-T (INTEGRATED DEVICE TECHNOLOGY INC) PLL BASED CLOCK DRIVER, 8 TRUE OUTPUT(S), 0 INVERTED OUTPUT(S), PDSO16 PDF资料下载

参数资料

| 型号: | ICS91309YFLF-T |

| 厂商: | INTEGRATED DEVICE TECHNOLOGY INC |

| 元件分类: | 时钟及定时 |

| 英文描述: | PLL BASED CLOCK DRIVER, 8 TRUE OUTPUT(S), 0 INVERTED OUTPUT(S), PDSO16 |

| 封装: | 0.150 INCH, MO-137, LEAD FREE, SSOP-16 |

| 文件页数: | 5/9页 |

| 文件大小: | 106K |

| 代理商: | ICS91309YFLF-T |

5

ICS91309

0093G—02/11/04

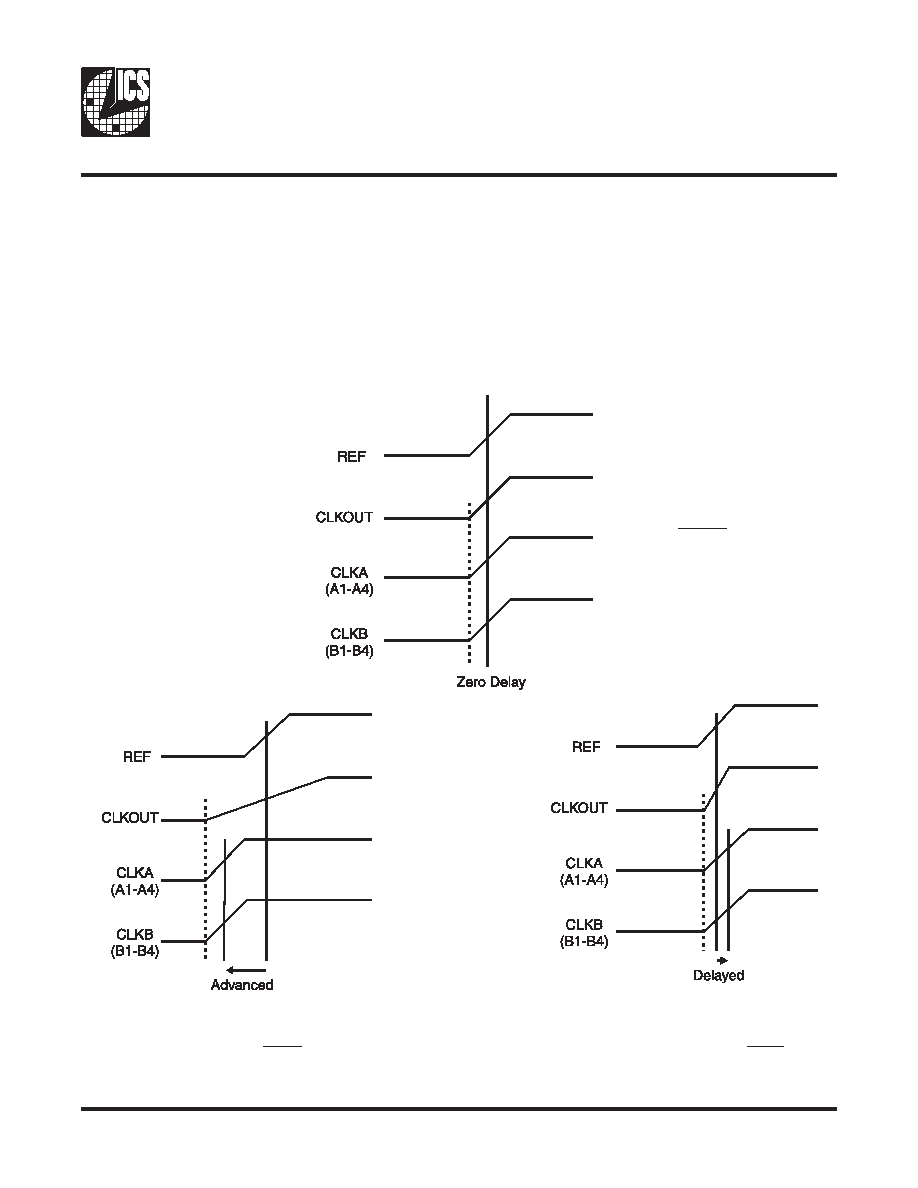

Output to Output Skew

The skew between CLKOUT and the CLKA/B outputs is not dynamically adjusted by the PLL. Since CLKOUT is one

of the inputs to the PLL, zero phase difference is maintained from REF to CLKOUT. If all outputs are equally loaded,

zero phase difference will maintained from REF to all outputs.

If applications requiring zero output-output skew, all the outputs must equally loaded.

If the CLKA/B outputs are less loaded than CLKOUT, CLKA/B outputs will lead it; and if the CLKA/B is more loaded

than CLKOUT, CLKA/B will lag the CLKOUT.

Since the CLKOUT and the CLKA/B outputs are identical, they all start at the same time, but different loads cause them

to have different rise times and different times crossing the measurement thresholds.

REF input and

all outputs

loaded Equally

REF input and CLKA/B

outputs loaded equally, with

CLKOUT loaded More.

REF input and CLKA/B

outputs loaded equally, with

CLKOUT loaded Less.

Timing diagrams with different loading configurations

相关PDF资料 |

PDF描述 |

|---|---|

| ICS91309YGLF-T | PLL BASED CLOCK DRIVER, 8 TRUE OUTPUT(S), 0 INVERTED OUTPUT(S), PDSO16 |

| ICS91309YM-T | PLL BASED CLOCK DRIVER, 8 TRUE OUTPUT(S), 0 INVERTED OUTPUT(S), PDSO16 |

| ICS91309YG-T | PLL BASED CLOCK DRIVER, 8 TRUE OUTPUT(S), 0 INVERTED OUTPUT(S), PDSO16 |

| ICS91309YMLF-T | PLL BASED CLOCK DRIVER, 8 TRUE OUTPUT(S), 0 INVERTED OUTPUT(S), PDSO16 |

| ICS9131M16LF | 80.19 MHz, PROC SPECIFIC CLOCK GENERATOR, PDSO16 |

相关代理商/技术参数 |

参数描述 |

|---|---|

| ICS9131 | 制造商:ICS 制造商全称:ICS 功能描述:32 KhZ Motherboard Frequency Generator |

| ICS9131-01CM | 制造商:未知厂家 制造商全称:未知厂家 功能描述:CPU System Clock Generator |

| ICS9131-01CN | 制造商:未知厂家 制造商全称:未知厂家 功能描述:CPU System Clock Generator |

| ICS9131-01CN16 | 制造商:ICS 制造商全称:ICS 功能描述:32 KhZ Motherboard Frequency Generator |

| ICS9131-01CS16 | 制造商:ICS 制造商全称:ICS 功能描述:32 KhZ Motherboard Frequency Generator |

发布紧急采购,3分钟左右您将得到回复。