- 您现在的位置:买卖IC网 > PDF目录61073 > ICS9148F-13 (INTEGRATED DEVICE TECHNOLOGY INC) 100 MHz, PROC SPECIFIC CLOCK GENERATOR, PDSO48 PDF资料下载

参数资料

| 型号: | ICS9148F-13 |

| 厂商: | INTEGRATED DEVICE TECHNOLOGY INC |

| 元件分类: | 时钟产生/分配 |

| 英文描述: | 100 MHz, PROC SPECIFIC CLOCK GENERATOR, PDSO48 |

| 封装: | SSOP-48 |

| 文件页数: | 1/7页 |

| 文件大小: | 347K |

| 代理商: | ICS9148F-13 |

Integrated

Circuit

Systems, Inc.

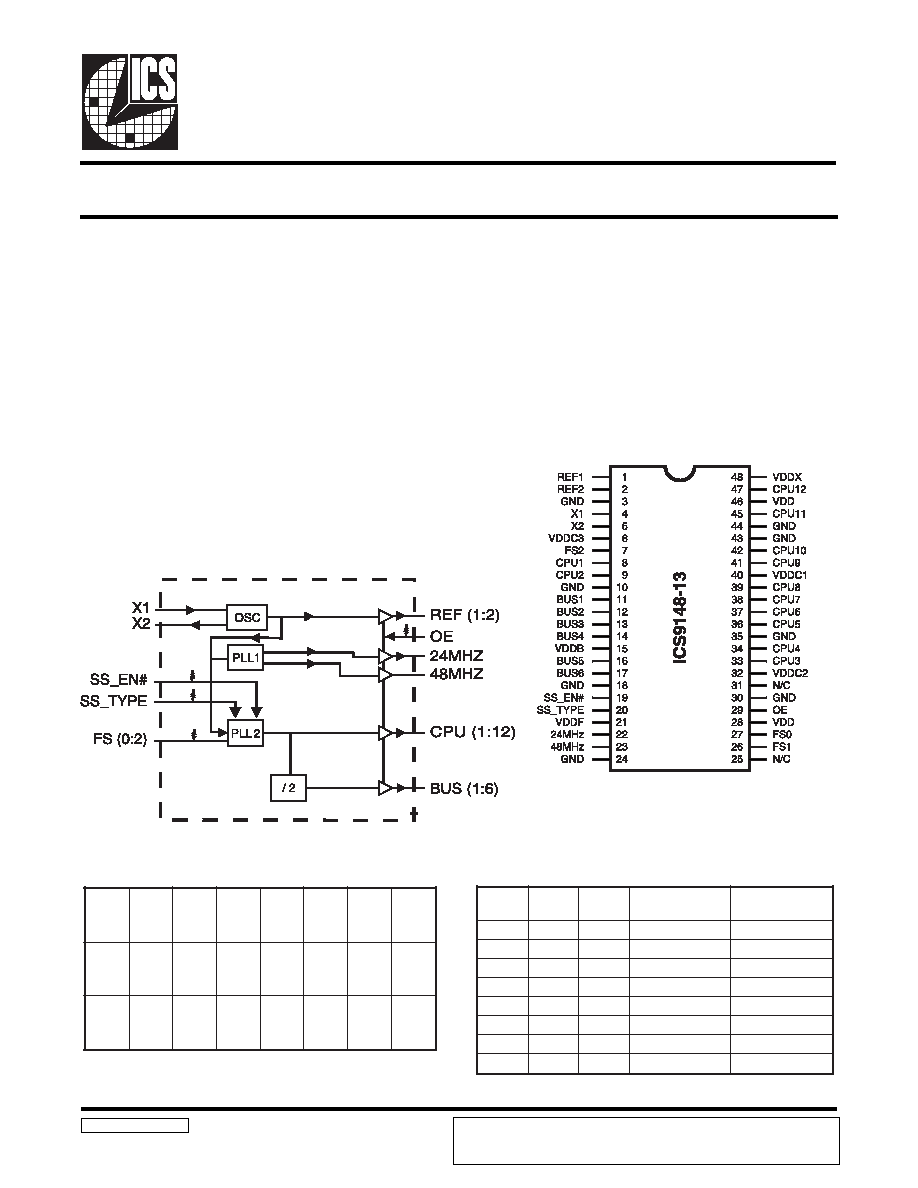

General Description

Features

ICS9148-13

Block Diagram

Pentium is a trademark of Intel Corporation

Frequency Generator & Integrated Buffers for PENTIUMTM

9148-13 Rev A 020398

Pin Configuration

The ICS9148-13 generates all clocks required for high speed

RISC or CISC microprocessor systems such as Intel Pentium

and PentiumPro. An output enable is provided for testability.

Spread Spectrum is available to modulate the CPU and BUS

PLL (leaving the REF, 24, 48 MHz operating normally). The

SS_EN# pin enables the spreading when low. The SS_TYPE

pin choses ±0.5% (nominally) center spread or +0, -2%

(nominally) downspread modulation.

High drive BUS outputs typically provide greater than 1V/ns

slew rate into 30 pF loads. CPU outputs typically provide

better than 1V/ns slew rate into 20 pF loads while maintaining

50 ± 5% duty cycle. The REF clock outputs typically provide

better than 0.8/ns slew rates.

Generates twelve processor, six bus, two

14.31818MHz, 24MHz and one 48MHz clock for

USB support.

Synchronous clocks skew matched to 250ps window

on CPUs and 500 ps window on BUSs

CPU to BUS skew, 3.0 to 5.0ns (CPU Early)

3.0V - 3.7V supply range

48-pin SSOP package

48-Pin SSOP

Functionality

2

S

F1

S

F0

S

F

n

i

)

2

1

:

1

(

U

P

C

z

H

M

n

i

)

6

:

1

(

S

U

B

z

H

M

000

5

75

.

7

3

00

1

0

13

.

3

01

0

5

70

.

0

3

01

1

3

.

3

85

6

.

1

4

10

0

55

2

10

1

0

60

3

11

0

7

6

.

6

63

3

.

3

111

5

55

.

7

2

E

OF

E

R

4

2

)

z

H

M

(

8

4

)

z

H

M

(

U

P

CS

U

BO

C

VC

S

O

1s

n

u

Rs

n

u

Rs

n

u

Rs

n

u

Rs

n

u

Rs

n

u

Rs

n

u

R

0

-

i

r

T

e

t

a

t

s

-

i

r

T

e

t

a

t

s

-

i

r

T

e

t

a

t

s

-

i

r

T

e

t

a

t

s

-

i

r

T

e

t

a

t

s

n

u

Rs

n

u

R

Output Enable

30K pullup resistor to VDD on OE, FS(0:2), SS_EN#, SS_TYPE

ICS reserves the right to make changes in the device data identified in this

publication without further notice. ICS advises its customers to obtain the latest

version of all device data to verify that any information being relied upon by the

customer is current and accurate.

相关PDF资料 |

PDF描述 |

|---|---|

| ICS9148F-PPP-LF | 100 MHz, PROC SPECIFIC CLOCK GENERATOR, PDSO48 |

| ICS9148F-49 | 100 MHz, PROC SPECIFIC CLOCK GENERATOR, PDSO28 |

| ICS9148F-49LF | 100 MHz, PROC SPECIFIC CLOCK GENERATOR, PDSO28 |

| ICS9148F-49LF | 100 MHz, PROC SPECIFIC CLOCK GENERATOR, PDSO28 |

| ICS9148YM-60 | 100 MHz, PROC SPECIFIC CLOCK GENERATOR, PDSO28 |

相关代理商/技术参数 |

参数描述 |

|---|---|

| ICS9148F-13T | 制造商:ICS 功能描述:9148F-13T |

| ICS9148F-17 | 制造商:未知厂家 制造商全称:未知厂家 功能描述:CPU System Clock Generator |

| ICS9148F-18 | 制造商:ICS 制造商全称:ICS 功能描述:Pentium/ProTM System Clock Chip |

| ICS9148F-20 | 制造商:ICS 制造商全称:ICS 功能描述:Pentium/ProTM System Clock Chip |

| ICS9148F25 | 制造商:未知厂家 制造商全称:未知厂家 功能描述:Industrial Control IC |

发布紧急采购,3分钟左右您将得到回复。