- 您现在的位置:买卖IC网 > PDF目录67705 > ICS9248F-20LF (INTEGRATED DEVICE TECHNOLOGY INC) 100 MHz, PROC SPECIFIC CLOCK GENERATOR, PDSO48 PDF资料下载

参数资料

| 型号: | ICS9248F-20LF |

| 厂商: | INTEGRATED DEVICE TECHNOLOGY INC |

| 元件分类: | 时钟产生/分配 |

| 英文描述: | 100 MHz, PROC SPECIFIC CLOCK GENERATOR, PDSO48 |

| 封装: | 0.300 INCH, SSOP-48 |

| 文件页数: | 7/11页 |

| 文件大小: | 427K |

| 代理商: | ICS9248F-20LF |

5

ICS9248-20

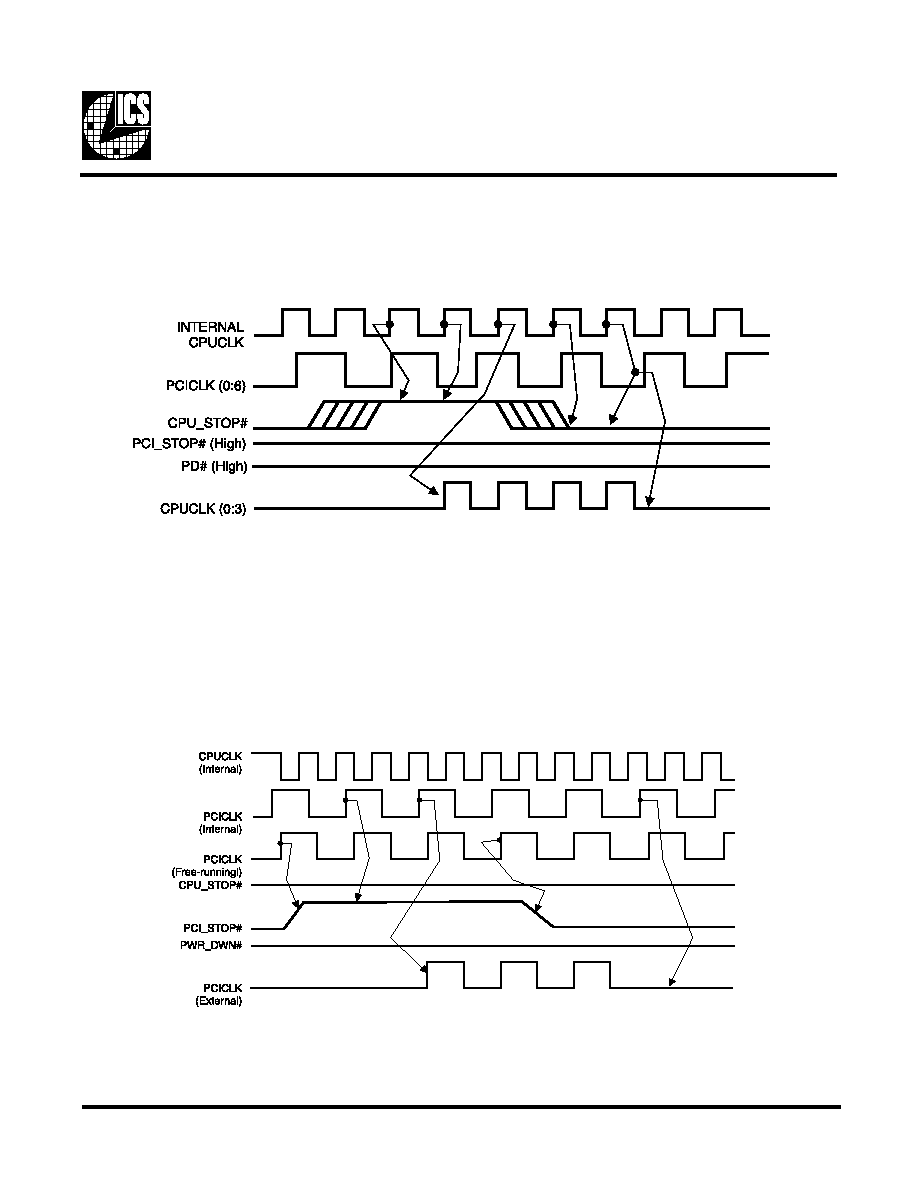

PCI_STOP# Timing Diagram

PCI_STOP# is an asynchronous input to the ICS9248-20. It is used to turn off the PCICLK (0:6) clocks for low power operation.

PCI_STOP# is synchronized by the ICS9248-20 internally. The minimum that the PCICLK (0:6) clocks are enabled

(PCI_STOP# high pulse) is at least 10 PCICLK (0:6) clocks. PCICLK (0:6) clocks are stopped in a low state and started with

a full high pulse width guaranteed. PCICLK (0:6) clock on latency cycles are only one rising PCICLK. Clock off latency is one

PCICLK clock.

CPU_STOP# Timing Diagram

CPUSTOP# is an asychronous input to the clock synthesizer. It is used to turn off the CPUCLKs for low power operation.

CPU_STOP# is synchronized by the ICS9248-20. The minimum that the CPUCLK is enabled (CPU_STOP# high pulse) is 100

CPUCLKs. All other clocks will continue to run while the CPUCLKs are disabled. The CPUCLKs will always be stopped in a

low state and start in such a manner that guarantees the high pulse width is a full pulse. CPUCLK on latency is less than 4

CPUCLKs and CPUCLK off latency is less than 4 CPUCLKs.

Notes:

1. All timing is referenced to the internal CPUCLK.

2. CPU_STOP# is an asynchronous input and metastable conditions may exist. This

signal is synchronized to the CPUCLKs inside the ICS9248-20.

3. All other clocks continue to run undisturbed.

4. PD# and PCI_STOP# are shown in a high (true) state.

Notes:

1. All timing is referenced to the Internal CPUCLK (defined as inside the ICS92 48 device.)

2. PCI_STOP# is an asynchronous input, and metastable conditions may exist. This signal is required to be synchronized

inside the ICS9248-20.

3. All other clocks continue to run undisturbed.

4. PD# and CPU_STOP# are shown in a high (true) state.

相关PDF资料 |

PDF描述 |

|---|---|

| ICS9248YF-101 | 137 MHz, PROC SPECIFIC CLOCK GENERATOR, PDSO48 |

| ICS9248YF-110LF | 115 MHz, PROC SPECIFIC CLOCK GENERATOR, PDSO48 |

| ICS9248YF-126-T | 150 MHz, PROC SPECIFIC CLOCK GENERATOR, PDSO48 |

| ICS9248YF-126LF | 150 MHz, PROC SPECIFIC CLOCK GENERATOR, PDSO48 |

| ICS9248YF-141LF-T | 166.66 MHz, PROC SPECIFIC CLOCK GENERATOR, PDSO48 |

相关代理商/技术参数 |

参数描述 |

|---|---|

| ICS9248F-56 | 制造商:未知厂家 制造商全称:未知厂家 功能描述:Peripheral IC |

| ICS9248F-61 | 制造商:ICS 制造商全称:ICS 功能描述:Frequency Timing Generator for Pentium II Systems |

| ICS9248G50 | 制造商:未知厂家 制造商全称:未知厂家 功能描述:Industrial Control IC |

| ICS9248YF-103 | 制造商:ICS 制造商全称:ICS 功能描述:Frequency Generator & Integrated Buffers for PENTIUM/ProTM |

| ICS9248YF-107 | 制造商:ICS 制造商全称:ICS 功能描述:Frequency Timing Generator for PENTIUM II Systems |

发布紧急采购,3分钟左右您将得到回复。