- 您现在的位置:买卖IC网 > PDF目录67112 > ICS9248YF-102LF-T 166.5 MHz, PROC SPECIFIC CLOCK GENERATOR, PDSO48 PDF资料下载

参数资料

| 型号: | ICS9248YF-102LF-T |

| 元件分类: | 时钟产生/分配 |

| 英文描述: | 166.5 MHz, PROC SPECIFIC CLOCK GENERATOR, PDSO48 |

| 封装: | 0.300 INCH, SSOP-48 |

| 文件页数: | 3/10页 |

| 文件大小: | 262K |

| 代理商: | ICS9248YF-102LF-T |

2

ICS9248-102

The ICS9248-102 is the single chip clock solution for

Desktop/Notebook designs using the SIS 540/630 style

chipset. It provides all necessary clock signals for such a

system.

Spread spectrum may be enabled through I

2C programming.

Spread spectrum typically reduces system EMI by 8dB to

10dB. This simplifies EMI qualification without resorting to

board design iterations or costly shielding. The ICS9248-

102

employs a proprietary closed loop design, which tightly

controls the percentage of spreading over process and

temperature variations.

Serial programming I

2C interface allows changing functions,

stop clock programming and frequency selection.

General Description

Power Groups

VDDREF = REF [1:0], X1, X2

VDDPCI = PCICLK_F, PCICLK [9:0]

VDDSDR = SDRAM [11:0], supply for PLL core,

VDD48 = 48MHz, 24MHz

VDDLIOAPIC = IOAPIC_F

VDDLCPU = CPUCLK_F [2:1]

Pin Configuration

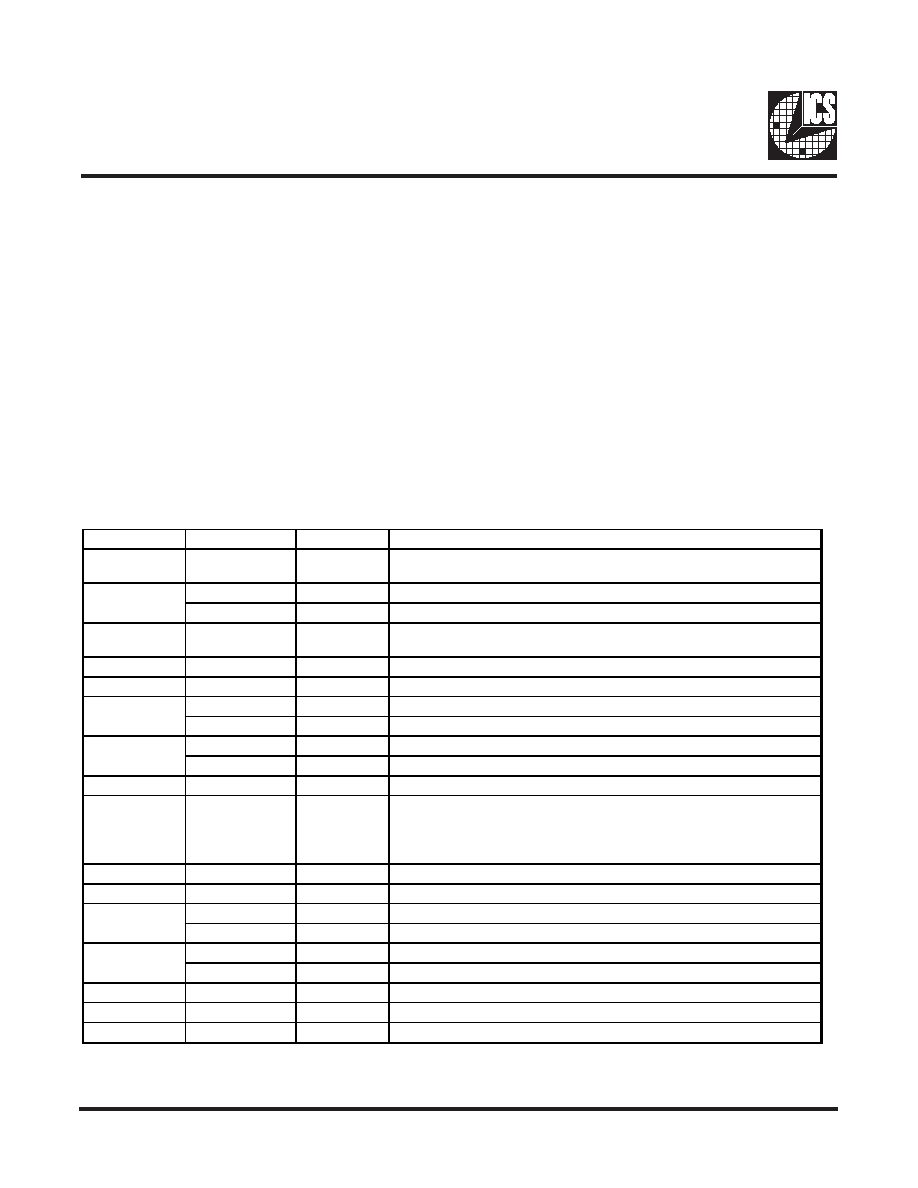

PIN NUMBER

PIN NAME

TYPE

DESCRIPTION

1, 6, 15, 19, 27,

30, 36, 42

VDD

PWR

3.3V Power supply for SDRAM output buffers, PCI output buffers,

reference output buffers and 48MHz output

REF0

OUT

14.318 MHz reference clock.

FS3

IN

Frequency select pin.

3, 10, 16, 22, 33,

39, 44

GND

PWR

Ground pin for 3V outputs.

4

X1

IN

Crystal input,nominally 14.318MHz.

5

X2

OUT

Crystal output, nominally 14.318MHz.

FS1

IN

Frequency select pin.

PCICLK0

OUT

PCI clock outputs.

FS2

IN

Frequency select pin.

PCICLK1

OUT

PCI clock outputs.

9, 11, 12, 13, 14

PCICLK [2:6]

OUT

PCI clock outputs.

41, 40, 38, 37,

35, 34, 32, 31,

29, 28, 21, 20,

18, 17

SDRAM

OUT

SDRAM clock outputs

23

SDATA

IN

Data input for I2C serial input, 5V tolerant input

24

SCLK

IN

Clock input of I2C input, 5V tolerant input

CPU2.5_3.3#

IN

Voltage select 2.5V when high - 3.3V when low

24_48MHz

OUT

Clock output for super I/O/USB default is 24MHz

FS0

IN

Frequency select pin.

48MHz

OUT

48MHz output clock

46, 45, 43

CPUCLK [0:2]

OUT

CPU clock outputs.

47

VDDLCPU

PWR

Power pin for the CPUCLKs. 2.5V

48

REF0

OUT

14.318 MHz reference clock.

26

2

7

8

25

相关PDF资料 |

PDF描述 |

|---|---|

| ICS9248YF-24LF | PLL BASED CLOCK DRIVER, 22 TRUE OUTPUT(S), 0 INVERTED OUTPUT(S), PDSO56 |

| ICS9248YF-24 | PLL BASED CLOCK DRIVER, 22 TRUE OUTPUT(S), 0 INVERTED OUTPUT(S), PDSO56 |

| ICS9248YF-24LF | PLL BASED CLOCK DRIVER, 22 TRUE OUTPUT(S), 0 INVERTED OUTPUT(S), PDSO56 |

| ICS9342YF-PPP-T-LF | 146.62 MHz, PROC SPECIFIC CLOCK GENERATOR, PDSO48 |

| ICS9342YF-PPP-T | 146.62 MHz, PROC SPECIFIC CLOCK GENERATOR, PDSO48 |

相关代理商/技术参数 |

参数描述 |

|---|---|

| ICS9248YF-103 | 制造商:ICS 制造商全称:ICS 功能描述:Frequency Generator & Integrated Buffers for PENTIUM/ProTM |

| ICS9248YF-107 | 制造商:ICS 制造商全称:ICS 功能描述:Frequency Timing Generator for PENTIUM II Systems |

| ICS9248YF-110 | 制造商:ICS 制造商全称:ICS 功能描述:AMD-K7TM System Clock Chip |

| ICS9248YF-112-T | 制造商:ICS 制造商全称:ICS 功能描述:Frequency Generator & Integrated Buffers for Celeron & PII/III⑩ |

| ICS9248YF-114-T | 制造商:ICS 制造商全称:ICS 功能描述:AMD - K7⑩ System Clock Chip |

发布紧急采购,3分钟左右您将得到回复。