- 您现在的位置:买卖IC网 > PDF目录67706 > ICS94201DF-T (INTEGRATED DEVICE TECHNOLOGY INC) 200 MHz, PROC SPECIFIC CLOCK GENERATOR, PDSO56 PDF资料下载

参数资料

| 型号: | ICS94201DF-T |

| 厂商: | INTEGRATED DEVICE TECHNOLOGY INC |

| 元件分类: | 时钟产生/分配 |

| 英文描述: | 200 MHz, PROC SPECIFIC CLOCK GENERATOR, PDSO56 |

| 封装: | 0.300 INCH, SSOP-56 |

| 文件页数: | 2/20页 |

| 文件大小: | 358K |

| 代理商: | ICS94201DF-T |

10

ICS94201

Preliminary Product Preview

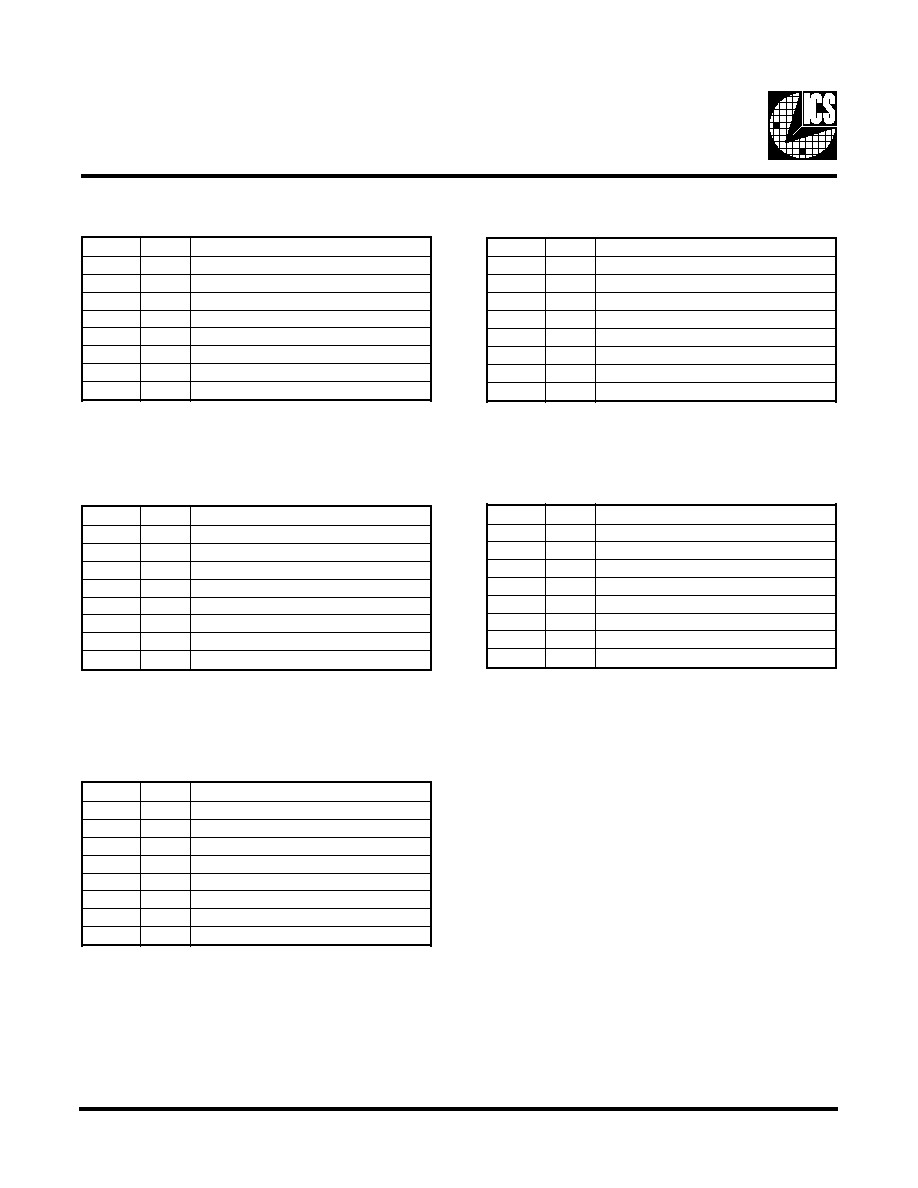

Byte 21: ICS Reserved Register

Byte 23: Group Skew Control Register

Byte 22: Group Skew Control Register

Note: Default 3V66 to PCI skew is 2.5ns bit [7:4]=1001.

Each increment or decrement of bit 4 to 7 will

introduce 100ps delay or advance on all PCI

clocks.

Notes:

1. PWD = Power on Default

Byte 24: Output Rise/Fall Time Select Register

Note: This is an unused register. Writing to this register will

not affect device performance or functionality.

Byte 20: Output Dividers Control Register

Note: Changing bits in these registers results in

frequency divider ratio changes. Incorrect

configuration of group gear ratio can cause

system malfunction.

Notes:

1. PWD = Power on Default

2. The power on default for byte 16-20 depends on the harware

(latch inputs FS[0:4]) or I2C (Byte 0 bit [1:7]) setting. Be sure

to read back and re-write the values of these 5 registers when

VCO frequency change is desired for the first pass.

3. If Byte 8 bit 7 is driven to "1" meaning programming is

intended, Byte 21-24 will lose their default power up value.

Note: Default 3V66 to IOAPIC skew is 2.5ns bit [3:0]=0111.

Each increment or decrement of bit 4 to 7 will introduce

100ps delay or advance on all IOAPIC clocks.

t

i

BD

W

Pn

o

i

t

p

i

r

c

s

e

D

7

t

i

BX

3

2

t

i

B

l

o

r

t

n

o

C

X

U

M

r

e

d

i

v

i

D

t

u

p

t

u

O

6

t

i

BX

2

t

i

B

l

o

r

t

n

o

C

X

U

M

r

e

d

i

v

i

D

t

u

p

t

u

O

5

t

i

BX

1

2

t

i

B

l

o

r

t

n

o

C

X

U

M

r

e

d

i

v

i

D

t

u

p

t

u

O

4

t

i

BX

0

2

t

i

B

l

o

r

t

n

o

C

X

U

M

r

e

d

i

v

i

D

t

u

p

t

u

O

3

t

i

BX

9

1

t

i

B

l

o

r

t

n

o

C

X

U

M

r

e

d

i

v

i

D

t

u

p

t

u

O

2

t

i

BX

8

1

t

i

B

l

o

r

t

n

o

C

X

U

M

r

e

d

i

v

i

D

t

u

p

t

u

O

1

t

i

BX

7

1

t

i

B

l

o

r

t

n

o

C

X

U

M

r

e

d

i

v

i

D

t

u

p

t

u

O

0

t

i

BX

6

1

t

i

B

l

o

r

t

n

o

C

X

U

M

r

e

d

i

v

i

D

t

u

p

t

u

O

t

i

BD

W

Pn

o

i

t

p

i

r

c

s

e

D

7

t

i

B

0)

d

e

v

r

e

s

e

R

(

6

t

i

B

0)

d

e

v

r

e

s

e

R

(

5

t

i

B

0)

d

e

v

r

e

s

e

R

(

4

t

i

B

0)

d

e

v

r

e

s

e

R

(

3

t

i

B

0)

d

e

v

r

e

s

e

R

(

2

t

i

B

0)

d

e

v

r

e

s

e

R

(

1

t

i

B

0)

d

e

v

r

e

s

e

R

(

0

t

i

B

0)

d

e

v

r

e

s

e

R

(

t

i

BD

W

Pn

o

i

t

p

i

r

c

s

e

D

7

t

i

B1

3

t

i

B

w

e

k

S

I

C

P

o

t

6

V

3

6

t

i

B0

2

t

i

B

w

e

k

S

I

C

P

o

t

6

V

3

5

t

i

B0

1

t

i

B

w

e

k

S

I

C

P

o

t

6

V

3

4

t

i

B1

0

t

i

B

w

e

k

S

I

C

P

o

t

6

V

3

t

i

B0

)

d

e

v

r

e

s

e

R

(

2

t

i

B0

)

d

e

v

r

e

s

e

R

(

1

t

i

B0

)

d

e

v

r

e

s

e

R

(

0

t

i

B0

)

d

e

v

r

e

s

e

R

(

t

i

BD

W

Pn

o

i

t

p

i

r

c

s

e

D

7

t

i

B0

)

d

e

v

r

e

s

e

R

(

6

t

i

B0

k

a

e

W

=

1

,

l

a

m

r

o

N

=

0

F

E

R

5

t

i

B0

k

a

e

W

=

1

,

l

a

m

r

o

N

=

0

z

h

M

8

4

,

4

2

4

t

i

B0

)

d

e

v

r

e

s

e

R

(

3

t

i

B0

k

a

e

W

=

1

,

l

a

m

r

o

N

=

0

I

C

P

2

t

i

B0

k

a

e

W

=

1

,

l

a

m

r

o

N

=

0

6

V

3

1

t

i

B0

k

a

e

W

=

1

,

l

a

m

r

o

N

=

0

M

A

R

D

S

0

t

i

B0

)

d

e

v

r

e

s

e

R

(

t

i

BD

W

Pn

o

i

t

p

i

r

c

s

e

D

7

t

i

B

0)

d

e

v

r

e

s

e

R

(

6

t

i

B

0)

d

e

v

r

e

s

e

R

(

5

t

i

B

0)

d

e

v

r

e

s

e

R

(

4

t

i

B

0)

d

e

v

r

e

s

e

R

(

3

t

i

B

03

t

i

B

w

e

k

S

C

I

P

A

O

I

o

t

6

V

3

2

t

i

B

12

t

i

B

w

e

k

S

C

I

P

A

O

I

o

t

6

V

3

1

t

i

B

11

t

i

B

w

e

k

S

C

I

P

A

O

I

o

t

6

V

3

0

t

i

B

10

t

i

B

w

e

k

S

C

I

P

A

O

I

o

t

6

V

3

相关PDF资料 |

PDF描述 |

|---|---|

| ICS94201DF-LF-T | 200 MHz, PROC SPECIFIC CLOCK GENERATOR, PDSO56 |

| ICS94201YFT | 200 MHz, PROC SPECIFIC CLOCK GENERATOR, PDSO56 |

| ICS94203YFLF-T | 200 MHz, PROC SPECIFIC CLOCK GENERATOR, PDSO56 |

| ICS94209YFLF-T | 200 MHz, PROC SPECIFIC CLOCK GENERATOR, PDSO48 |

| ICS94210YF-PPP-T-LF | 166.66 MHz, PROC SPECIFIC CLOCK GENERATOR, PDSO48 |

相关代理商/技术参数 |

参数描述 |

|---|---|

| ICS94201YFT | 制造商:ICS 制造商全称:ICS 功能描述:Programmable System Frequency Generator for PII/III⑩ |

| ICS94203 | 制造商:ICS 制造商全称:ICS 功能描述:Programmable System Frequency Generator for PII/III⑩ |

| ICS94203F-T | 制造商:ICS 制造商全称:ICS 功能描述:Peripheral IC |

| ICS94203YF-T | 制造商:ICS 制造商全称:ICS 功能描述:Programmable System Frequency Generator for PII/III⑩ |

| ICS94206 | 制造商:ICS 制造商全称:ICS 功能描述:Programmable System Frequency Generator for PII/III⑩ |

发布紧急采购,3分钟左右您将得到回复。