- 您现在的位置:买卖IC网 > PDF目录362809 > ICS94241 Programmable TCH⑩ for Differential PIII⑩ Processor PDF资料下载

参数资料

| 型号: | ICS94241 |

| 英文描述: | Programmable TCH⑩ for Differential PIII⑩ Processor |

| 中文描述: | 可编程清桦⑩⑩微分PIII处理器 |

| 文件页数: | 1/16页 |

| 文件大小: | 153K |

| 代理商: | ICS94241 |

Integrated

Circuit

Systems, Inc.

ICS94241

0453C—10/26/04

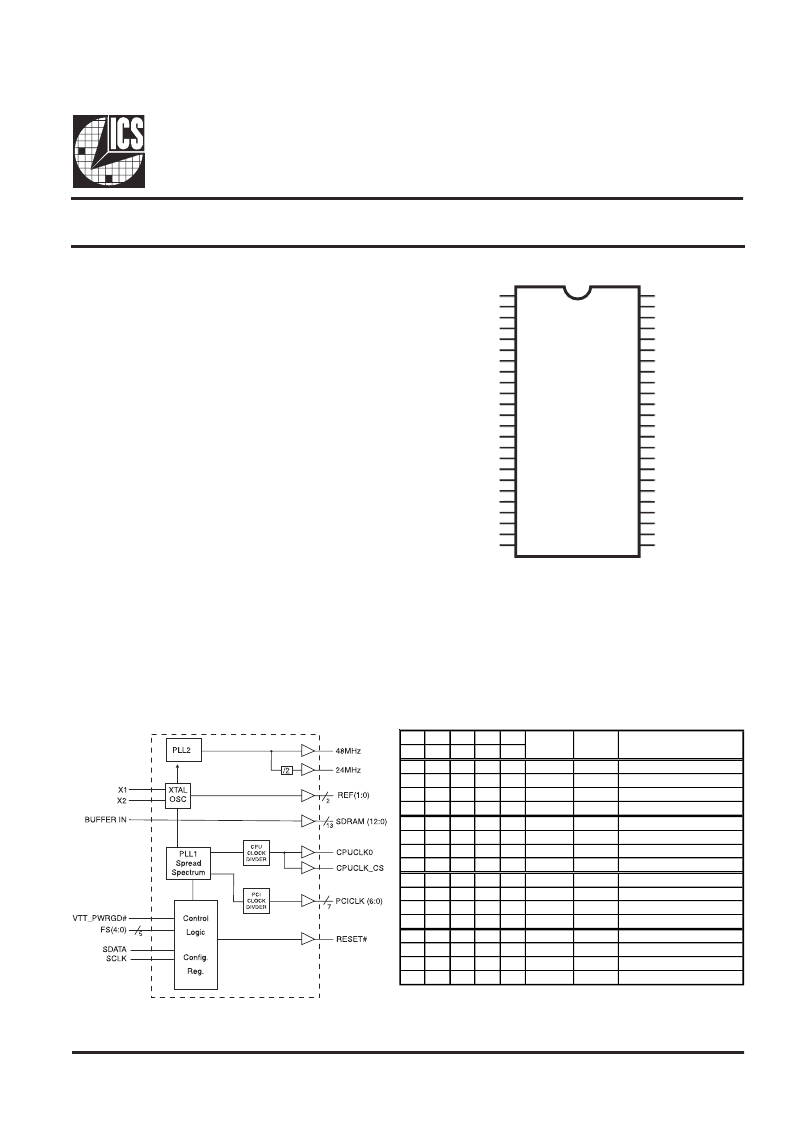

Pin Configuration

Recommended Application:

VIA PL133-T style chipset with Intel differential PIII

processor

Output Features:

2 - CPUs @2.5V

13 - SDRAM @ 3.3V

7 - PCI @3.3V,

1 - 48MHz, @3.3V

1 - 24MHz @ 3.3V

2 - REF @3.3V, 14.318MHz.

Features:

Programmable ouput frequency

Programmable ouput rise/fall time

Programmable output to output skew

Programmable spread spectrum for EMI control

Real time system reset output

Watchdog timer technology to reset system

if over-clocking causes malfunction

Uses external 14.318MHz crystal

Key Specifications:

CPU – CPU: <175ps

SDRAM - SDRAM: <500ps

PCI – PCI: <500ps

CPU-SDRAM: <500ps

CPU(early)-PCI: Min=1.0ns, Typ=2.0ns, Max=4.0ns

Programmable TCH for Differential PIII Processor

Block Diagram

48-Pin 300mil SSOP

* Internal Pull-up Resistor of 120K to VDD

** Internal Pull-down resistor of 120K to GND

1. This output has 1.5 to 2X drive strength

VDDREF

GNDREF

X1

X2

VDDPCI

*FS4/PCICLK0

*FS3/PCICLK1

GNDPCI

PCICLK2

PCICLK3

PCICLK4

PCICLK5

PCICLK6

VDDPCI

BUFFER_IN

GNDSDR

SDRAM12

SDRAM11

VDDSDR

SDRAM10

SDRAM9

GND48

SDATA

SCLK

VTT_PWRGD#

REF0

REF1/FS2**

GNDCPU

CPUCLK_CS

CPUCLK0

VDDLCPU

RESET#

SDRAM0

GNDSDR

SDRAM1

SDRAM2

VDDSDR

SDRAM3

SDRAM4

GNDSDR

SDRAM5

SDRAM6

VDDSDR

SDRAM7

SDRAM8

AVDD48

48MHz/FS0**

24MHz/FS1**

1

I

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

19

20

21

22

23

24

48

47

46

45

44

43

42

41

40

39

38

37

36

35

34

33

32

31

30

29

28

27

26

25

Functionality

For additional margin testing frequencies refer to pg 5

frequency table.

Bit2 Bit7 Bit6 Bit5 Bit4

FS4 FS3 FS2 FS1 FS0

0

0

0

0

0

0

0

0

0

0

0

0

0

1

0

0

1

0

0

1

0

0

1

0

1

0

0

1

0

0

1

0

0

1

0

0

1

1

0

1

1

0

1

1

0

1

1

0

0

0

1

1

0

0

1

1

0

0

1

1

0

0

1

1

0

1

0

1

0

1

0

1

0

1

0

1

0

1

0

1

66.67

66.67

68.67

71.34

100.00

100.00

103.00

107.00

200.00

200.00

206.00

214.00

133.33

133.33

137.33

142.67

33.33

33.33

34.33

35.66

33.33

33.33

34.33

35.67

33.33

33.33

34.33

35.67

33.33

33.33

34.33

35.67

+/- 0.25 Center Spread

0 to -0.5% Down Spread

± 0.25 Center Spread

+/- 0.25 Center Spread

+/- 0.25 Center Spread

0 to -0.5% Down Spread

+/- 0.25 Center Spread

+/- 0.25 Center Spread

+/- 0.25 Center Spread

0 to -0.5% Down Spread

+/- 0.25 Center Spread

+/- 0.25 Center Spread

+/- 0.25 Center Spread

0 to -0.5% Down Spread

+/- 0.25 Center Spread

+/- 0.25 Center Spread

Spread Percentage

CPUCLK PCICLK

相关PDF资料 |

PDF描述 |

|---|---|

| ICS94241FLF-T | Programmable TCH⑩ for Differential PIII⑩ Processor |

| ICS950218 | Programmable Timing Control Hub TM for P4 TM |

| ICS950218YFLF-T | Programmable Timing Control Hub TM for P4 TM |

| ICS951402 | Programmable Timing Control Hub for P4 processor |

| ICS951402YFLF-T | Programmable Timing Control Hub for P4 processor |

相关代理商/技术参数 |

参数描述 |

|---|---|

| ICS94241FLF-T | 制造商:ICS 制造商全称:ICS 功能描述:Programmable TCH⑩ for Differential PIII⑩ Processor |

| ICS948AI147L | 制造商:ICS 制造商全称:ICS 功能描述:LOW SKEW, 1-TO-12 DIFFERENTIAL-TO-LVCMOS/LVTTL FANOUT BUFFER |

| ICS950104 | 制造商:ICS 制造商全称:ICS 功能描述:Programmable System Clock Chip for PIII Processor |

| ICS950104YFT | 制造商:ICS 制造商全称:ICS 功能描述:Programmable System Clock Chip for PIII Processor |

| ICS950201 | 制造商:ICS 制造商全称:ICS 功能描述:Programmable Timing Control Hub⑩ for P4⑩ |

发布紧急采购,3分钟左右您将得到回复。