- 您现在的位置:买卖IC网 > PDF目录67707 > ICS950810YGLF-T (INTEGRATED DEVICE TECHNOLOGY INC) 200 MHz, PROC SPECIFIC CLOCK GENERATOR, PDSO56 PDF资料下载

参数资料

| 型号: | ICS950810YGLF-T |

| 厂商: | INTEGRATED DEVICE TECHNOLOGY INC |

| 元件分类: | 时钟产生/分配 |

| 英文描述: | 200 MHz, PROC SPECIFIC CLOCK GENERATOR, PDSO56 |

| 封装: | 6.10 MM, 0.50 MM PITCH, LEAD FREE, MO-153, TSSOP-56 |

| 文件页数: | 7/19页 |

| 文件大小: | 167K |

| 代理商: | ICS950810YGLF-T |

15

ICS950810

0472F—01/12/04

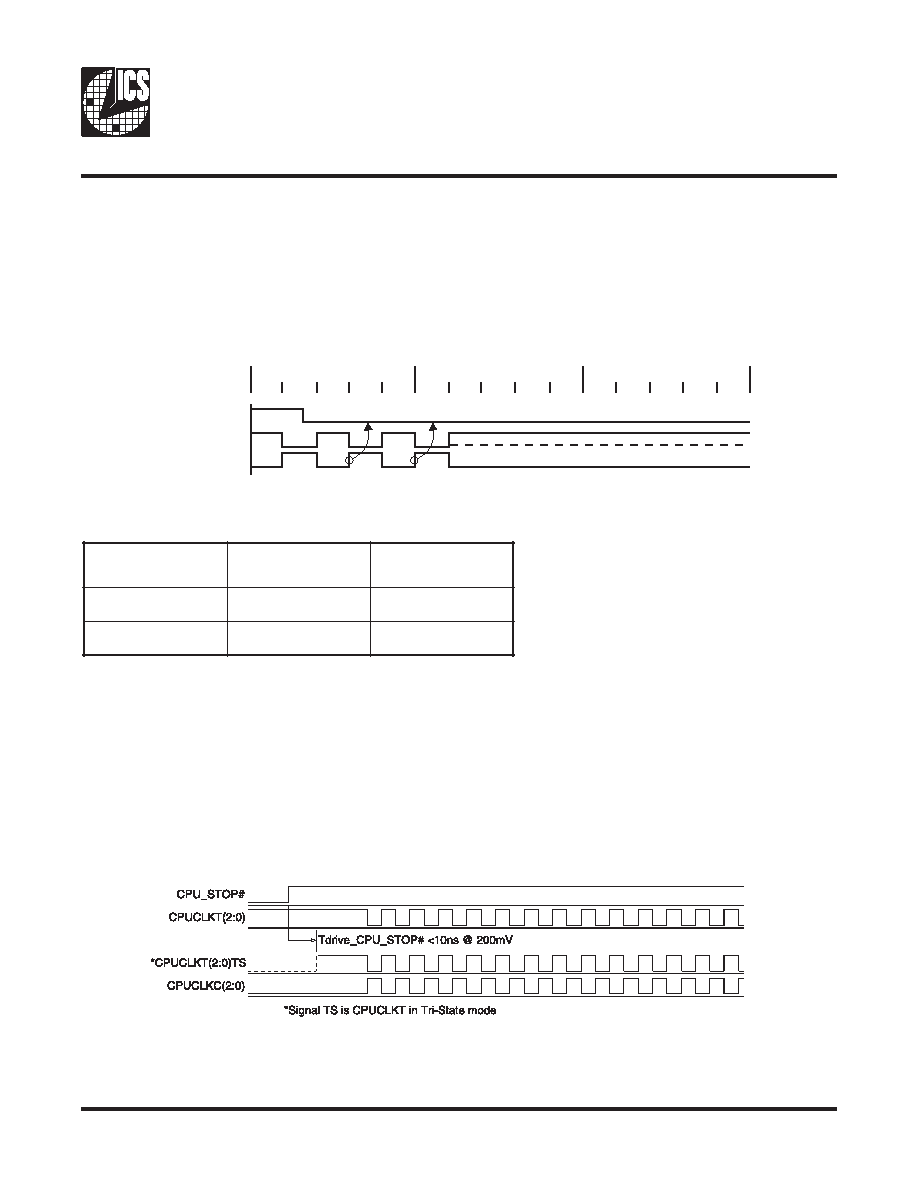

CPU_STOP# - Assertion (transition from logic "1" to logic "0")

Assertion of CPU_STOP# Waveforms

CPU_STOP# Functionality

#

P

O

T

S

_

U

P

CT

U

P

CC

U

P

C

1l

a

m

r

o

Nl

a

m

r

o

N

0t

l

u

M

*

f

e

r

it

a

o

l

F

The impact of asserting the CPU_STOP# pin is all CPU outputs that are set in the I

2C configuration to be stoppable via

assertion of CPU_STOP# are to be stopped after their next transition. When the I

2C Bit 6 of Byte 1 is programmed to '0'

the final state of the stopped CPU signals is CPU = High and CPU# = Low. There is to be no change to the output drive

current values. The CPU will be driven high with a current value equal to (Mult 0 'select') x (Iref), the CPU# signal will not

be driven . When the I

2C Bit 6 of Byte 1 is programmed to '1' then final state of the stopped CPU signals is Low, both CPU

and CPU# outputs will not be driven.

CPU_STOP#

CPUT

CPUC

CPU_STOP# - De-assertion (transition from logic "0" to logic "1")

De-assertion of CPU_STOP# Waveforms

All CPU outputs that were stopped are to resume normal operation in a glitch free manner. The maximum latency from the

de-assertion to active outputs is to be defined to be tetween 2 - 6 CPU clock periods (2 clocks are shown). If the I2C Bit

6 of Byte 1 is programmed to "1" then the stopped CPU outputs will be driven High within 3 nS of CPU_Stop# de-assertion.

相关PDF资料 |

PDF描述 |

|---|---|

| ICS950811YF-T | 200 MHz, PROC SPECIFIC CLOCK GENERATOR, PDSO56 |

| ICS950811YFLF-T | 200 MHz, PROC SPECIFIC CLOCK GENERATOR, PDSO56 |

| ICS950811YGLF-T | 200 MHz, PROC SPECIFIC CLOCK GENERATOR, PDSO56 |

| ICS950812YFT | 200 MHz, PROC SPECIFIC CLOCK GENERATOR, PDSO56 |

| ICS950813YFT | 200 MHz, PROC SPECIFIC CLOCK GENERATOR, PDSO56 |

相关代理商/技术参数 |

参数描述 |

|---|---|

| ICS950811 | 制造商:ICS 制造商全称:ICS 功能描述:Frequency Generator with 200MHz Differential CPU Clocks |

| ICS950811AGLFT | 功能描述:IC FREQ GEN 200MHZ CLK 56-TSSOP RoHS:是 类别:集成电路 (IC) >> 时钟/计时 - 专用 系列:- 标准包装:1 系列:- 类型:时钟/频率发生器,多路复用器 PLL:是 主要目的:存储器,RDRAM 输入:晶体 输出:LVCMOS 电路数:1 比率 - 输入:输出:1:2 差分 - 输入:输出:无/是 频率 - 最大:400MHz 电源电压:3 V ~ 3.6 V 工作温度:0°C ~ 85°C 安装类型:表面贴装 封装/外壳:16-TSSOP(0.173",4.40mm 宽) 供应商设备封装:16-TSSOP 包装:Digi-Reel® 其它名称:296-6719-6 |

| ICS950811YFLFT | 制造商:ICS 制造商全称:ICS 功能描述:Frequency Generator with 200MHz Differential CPU Clocks |

| ICS950812 | 制造商:ICS 制造商全称:ICS 功能描述:Frequency Generator with 200MHz Differential CPU Clocks |

| ICS950812CGLF | 功能描述:IC FREQ GEN 200MHZ CLK 56-TSSOP RoHS:是 类别:集成电路 (IC) >> 时钟/计时 - 专用 系列:- 标准包装:1,500 系列:- 类型:时钟缓冲器/驱动器 PLL:是 主要目的:- 输入:- 输出:- 电路数:- 比率 - 输入:输出:- 差分 - 输入:输出:- 频率 - 最大:- 电源电压:3.3V 工作温度:0°C ~ 70°C 安装类型:表面贴装 封装/外壳:28-SSOP(0.209",5.30mm 宽) 供应商设备封装:28-SSOP 包装:带卷 (TR) 其它名称:93786AFT |

发布紧急采购,3分钟左右您将得到回复。