- 您现在的位置:买卖IC网 > PDF目录65535 > ICS951601YFLF (INTEGRATED DEVICE TECHNOLOGY INC) 66.66 MHz, PROC SPECIFIC CLOCK GENERATOR, PDSO48 PDF资料下载

参数资料

| 型号: | ICS951601YFLF |

| 厂商: | INTEGRATED DEVICE TECHNOLOGY INC |

| 元件分类: | 时钟产生/分配 |

| 英文描述: | 66.66 MHz, PROC SPECIFIC CLOCK GENERATOR, PDSO48 |

| 封装: | 0.300 INCH, ROHS COMPLIANT, MO-118, SSOP-48 |

| 文件页数: | 5/10页 |

| 文件大小: | 137K |

| 代理商: | ICS951601YFLF |

4

ICS951601

Preliminary Product Preview

0663C—10/04/05

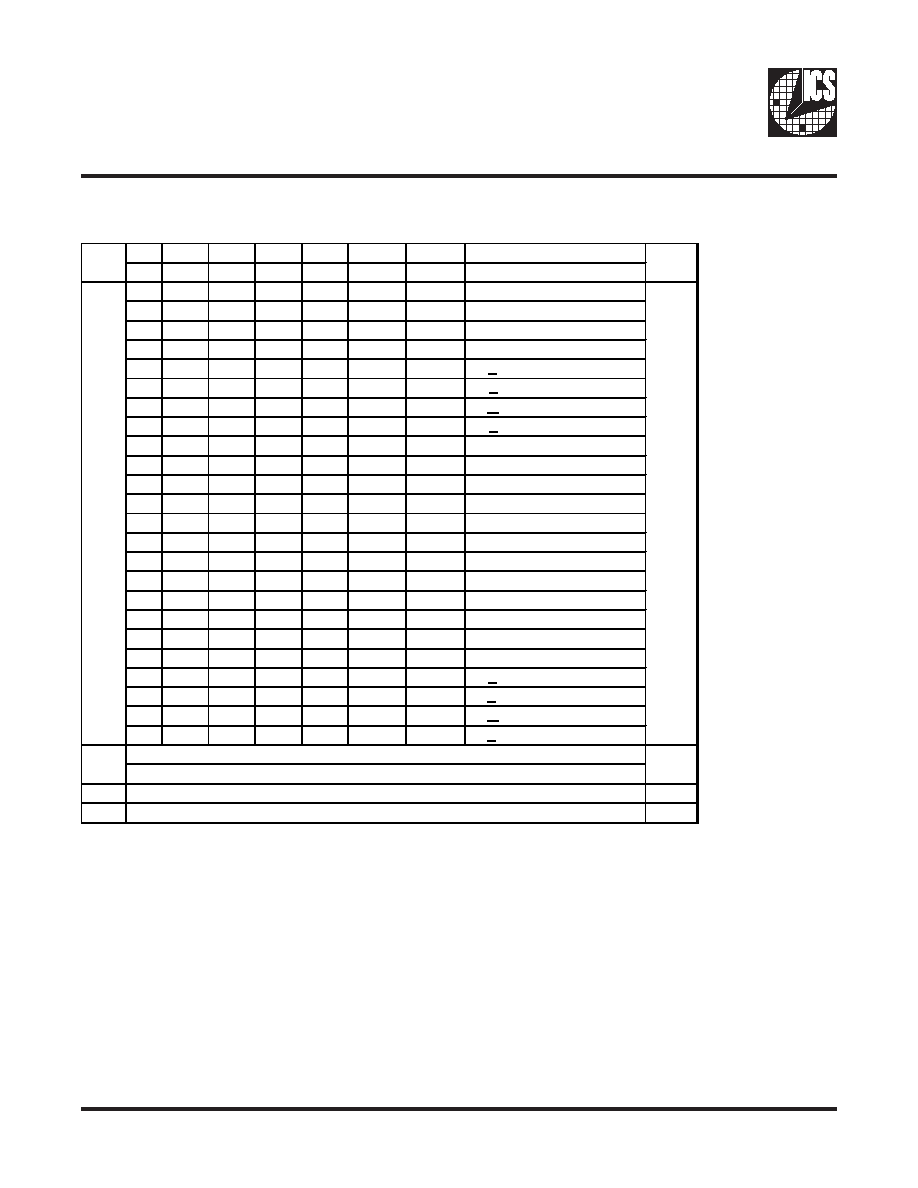

Byte 0: Functionality and frequency select register (Default = 0)

Serial Configuration Command Bitmap

Bit2 Bit7

Bit6

Bit5

Bit4

66MHZ 33MHz

FEATURES

FS4 FS3

FS2

FS1

FS0

0

0000

66

33

-0.25 % down spread

0

0001

66

33

-0.5 % down spread

0

0010

66

33

-1.0 % down spread

0

0011

66

33

-1.5 % down spread

0

0100

66

33

+ 0.25 % center spread

0

0101

66

33

+0.5 % center spread

0

0110

66

33

+ 1.0 % center spread

0

0111

66.6

33.3

+1.5 % center spread

0

1000

67.32

33.66

2% over-clocking

0

1001

68.64

34.32

4% over-clocking

0

1010

69.96

34.98

6% over-clocking

0

1011

72.6

36.3

10% over-clocking

0

1100

65.27

32.63

2% under- clocking

0

1101

63.96

31.97

2% under- clocking

0

1110

62.6

31.3

2% under- clocking

0

1111

60

30

2% under- clocking

1

0000

66.6

33.3

-1.4 % down spread

1

0001

66.6

33.3

-1.6 % down spread

1

0010

66.6

33.3

-1.8 % down spread

1

0011

66.6

33.3

-2.0 % down spread

1

0100

66.6

33.3

+ 1.4 % center spread

1

0101

66.6

33.3

+ 1.6 % center spread

1

0110

66.6

33.3

+ 1.8 % center spread

1

0111

66.6

33.3

+ 2.0 % center spread

Bit1

0-Normal

1-Spread spectrum Enabled

0

Bit0

0-Running 1-Tristate all outputs

0

Bit

PWD

00000

Bit

2,7:4

Bit3

0

0-Frequency and Spread is seleced by hardware select. Latched input

1-Frequency is seleced by Bit2, 7:4

相关PDF资料 |

PDF描述 |

|---|---|

| ICS95V157YGLF-T | PLL BASED CLOCK DRIVER, 10 TRUE OUTPUT(S), 0 INVERTED OUTPUT(S), PDSO48 |

| ICS95V157YG-T | PLL BASED CLOCK DRIVER, 10 TRUE OUTPUT(S), 0 INVERTED OUTPUT(S), PDSO48 |

| ICS95V842YF-T | 95V SERIES, PLL BASED CLOCK DRIVER, 1 TRUE OUTPUT(S), 0 INVERTED OUTPUT(S), PDSO16 |

| ICS95V842YFLF-T | 95V SERIES, PLL BASED CLOCK DRIVER, 1 TRUE OUTPUT(S), 0 INVERTED OUTPUT(S), PDSO16 |

| ICS95V857YG | PLL BASED CLOCK DRIVER, 10 TRUE OUTPUT(S), 0 INVERTED OUTPUT(S), PDSO48 |

相关代理商/技术参数 |

参数描述 |

|---|---|

| ICS951702 | 制造商:IDT 制造商全称:Integrated Device Technology 功能描述:PIII? System Clock Chip for DDR SDRAM |

| ICS951901 | 制造商:ICS 制造商全称:ICS 功能描述:Programmable Frequency Generator & Integrated Buffers for Pentium III Processor |

| ICS951901AF | 功能描述:IC FREQ GENERATOR/BUFFER 48-SSOP RoHS:否 类别:集成电路 (IC) >> 时钟/计时 - 专用 系列:- 标准包装:28 系列:- 类型:时钟/频率发生器 PLL:是 主要目的:Intel CPU 服务器 输入:时钟 输出:LVCMOS 电路数:1 比率 - 输入:输出:3:22 差分 - 输入:输出:无/是 频率 - 最大:400MHz 电源电压:3.135 V ~ 3.465 V 工作温度:0°C ~ 85°C 安装类型:表面贴装 封装/外壳:64-TFSOP (0.240",6.10mm 宽) 供应商设备封装:64-TSSOP 包装:管件 |

| ICS951901AFLF | 功能描述:IC FREQ GENERATOR/BUFFER 48-SSOP RoHS:是 类别:集成电路 (IC) >> 时钟/计时 - 专用 系列:- 标准包装:28 系列:- 类型:时钟/频率发生器 PLL:是 主要目的:Intel CPU 服务器 输入:时钟 输出:LVCMOS 电路数:1 比率 - 输入:输出:3:22 差分 - 输入:输出:无/是 频率 - 最大:400MHz 电源电压:3.135 V ~ 3.465 V 工作温度:0°C ~ 85°C 安装类型:表面贴装 封装/外壳:64-TFSOP (0.240",6.10mm 宽) 供应商设备封装:64-TSSOP 包装:管件 |

| ICS951901AFLFT | 功能描述:IC FREQ GENERATOR/BUFFER 48-SSOP RoHS:是 类别:集成电路 (IC) >> 时钟/计时 - 专用 系列:- 标准包装:28 系列:- 类型:时钟/频率发生器 PLL:是 主要目的:Intel CPU 服务器 输入:时钟 输出:LVCMOS 电路数:1 比率 - 输入:输出:3:22 差分 - 输入:输出:无/是 频率 - 最大:400MHz 电源电压:3.135 V ~ 3.465 V 工作温度:0°C ~ 85°C 安装类型:表面贴装 封装/外壳:64-TFSOP (0.240",6.10mm 宽) 供应商设备封装:64-TSSOP 包装:管件 |

发布紧急采购,3分钟左右您将得到回复。