- 您现在的位置:买卖IC网 > PDF目录362809 > ICS952623YFT Programmable Timing Control Hub for Next Gen P4 processor PDF资料下载

参数资料

| 型号: | ICS952623YFT |

| 英文描述: | Programmable Timing Control Hub for Next Gen P4 processor |

| 中文描述: | 可编程定时控制中心,为下一代P4处理器 |

| 文件页数: | 16/27页 |

| 文件大小: | 329K |

| 代理商: | ICS952623YFT |

第1页第2页第3页第4页第5页第6页第7页第8页第9页第10页第11页第12页第13页第14页第15页当前第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页

16

Integrated

Circuit

Systems, Inc.

ICS952623

Advance Information

0758—02/08/05

The PCI_STOP# signal is on an active low input controlling PCI and SRC outputs. If PCIF (2:0) and SRC clocks can be set to

be free-running through I2C programming. Outputs set to be free-running will ignore both the PCI_STOP pin and the

PCI_STOP register bit.

PCI Stop Functionality

#

P

O

T

S

_

C

P

U

P

C

#

U

P

C

C

R

S

#

C

R

S

6

6

V

3

I

C

P

/

C

P

T

O

D

/

B

S

U

F

E

R

e

o

N

1

l

m

r

N

l

m

r

N

l

m

r

N

l

m

r

N

z

H

M

6

6

z

H

M

3

3

z

H

M

8

4

z

H

M

8

1

3

1

0

l

m

r

N

l

m

r

N

6

*

f

r

t

o

w

o

L

z

H

M

6

6

w

o

L

z

H

M

8

4

z

H

M

8

1

3

1

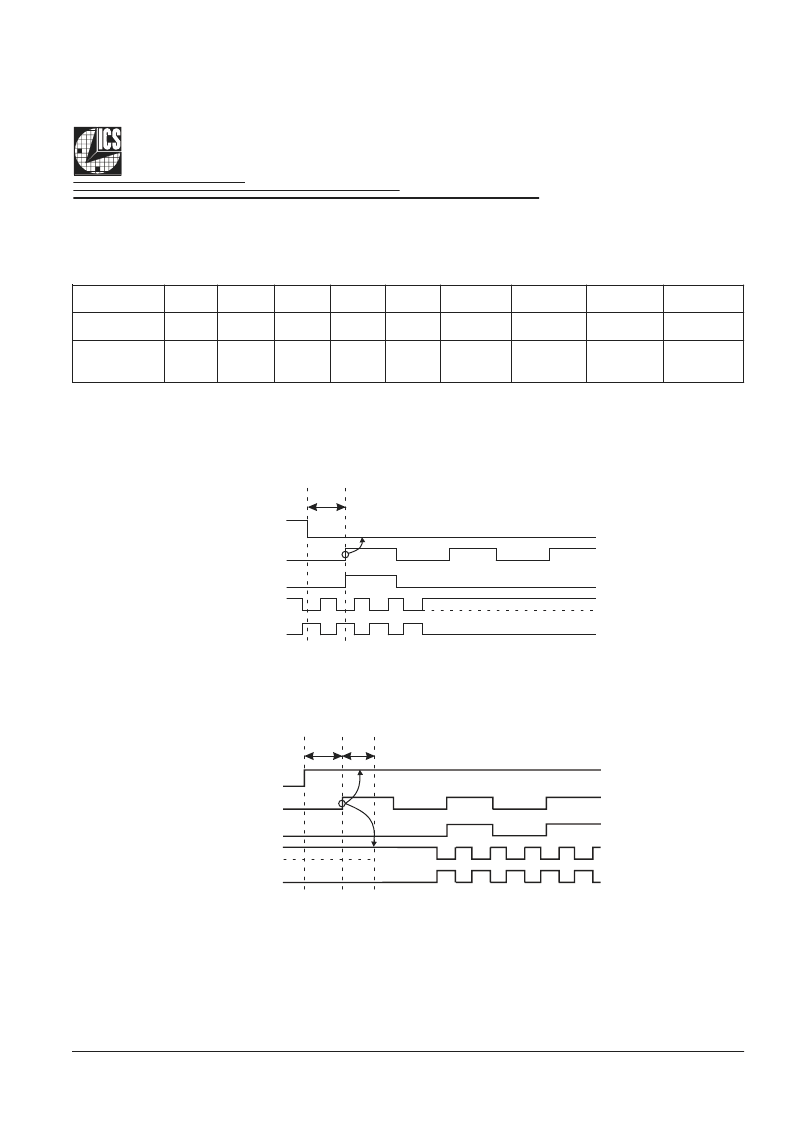

The clock samples the PCI_STOP# signal on a rising edge of PCIF clock. After detecting the PCI_STOP# assertion low, all

PCI[6:0] and stoppable PCIF[2:0] clocks will latch low on their next high to low transition. After the PCI clocks are latched low,

the SRC clock, (if set to stoppable) will latch high at Iref * 6 (or tristate if Byte 2 Bit 6 = 1) upon its next low to high transition and

the SRC# will latch low as shown below.

PCI_STOP#

Tsu

PCIF[2:0] 33MHz

PCI[6:0] 33MHz

SRC 100MHz

SRC# 100MHz

PCI_STOP# Assertion (transition from '1' to '0')

The de-assertion of the PCI_Stop# signal is to be sampled on the rising edge of the PCIF free running clock domain. After

detecting PCI_Stop# de-assertion, all PCI[6:0], stoppable PCIF[2:0] and stoppable SRC clocks will resume in a glitch free

manner.

PCI_STOP#

Tsu

Tdrive_SRC

PCIF[2:0] 33MHz

PCI[6:0] 33MHz

SRC 100MHz

SRC# 100MHz

PCI_STOP# - De-assertion

相关PDF资料 |

PDF描述 |

|---|---|

| ICS952623YGT | Programmable Timing Control Hub for Next Gen P4 processor |

| ICS95V847 | 2.5V Wide Range Frequency Clock Driver (45MHz - 233MHz) |

| ICS95V847YGLF-T | 2.5V Wide Range Frequency Clock Driver (45MHz - 233MHz) |

| ICS95V847 | 2.5V Wide Range Frequency Clock Driver (45MHz - 233MHz) |

| ICS95V847YGLF-T | 2.5V Wide Range Frequency Clock Driver (45MHz - 233MHz) |

相关代理商/技术参数 |

参数描述 |

|---|---|

| ICS952623YGT | 制造商:ICS 制造商全称:ICS 功能描述:Programmable Timing Control Hub for Next Gen P4 processor |

| ICS952702 | 制造商:ICS 制造商全称:ICS 功能描述:Programmable Timing Control Hub for K7 System |

| ICS952702YFLF-T | 制造商:ICS 制造商全称:ICS 功能描述:Programmable Timing Control Hub for K7 System |

| ICS952703 | 制造商:ICS 制造商全称:ICS 功能描述:Programmable Timing Control Hub for K7 System |

| ICS952703BF | 功能描述:IC TIMING CTRL HUB K7 48-SSOP RoHS:否 类别:集成电路 (IC) >> 时钟/计时 - 专用 系列:TCH™ 标准包装:28 系列:- 类型:时钟/频率发生器 PLL:是 主要目的:Intel CPU 服务器 输入:时钟 输出:LVCMOS 电路数:1 比率 - 输入:输出:3:22 差分 - 输入:输出:无/是 频率 - 最大:400MHz 电源电压:3.135 V ~ 3.465 V 工作温度:0°C ~ 85°C 安装类型:表面贴装 封装/外壳:64-TFSOP (0.240",6.10mm 宽) 供应商设备封装:64-TSSOP 包装:管件 |

发布紧急采购,3分钟左右您将得到回复。