- 您现在的位置:买卖IC网 > PDF目录67708 > ICS954204YGT 400 MHz, PROC SPECIFIC CLOCK GENERATOR, PDSO56 PDF资料下载

参数资料

| 型号: | ICS954204YGT |

| 元件分类: | 时钟产生/分配 |

| 英文描述: | 400 MHz, PROC SPECIFIC CLOCK GENERATOR, PDSO56 |

| 封装: | 6.10 MM, 0.50 MM PITCH, MO-153, TSSOP-56 |

| 文件页数: | 5/16页 |

| 文件大小: | 199K |

| 代理商: | ICS954204YGT |

13

Integrated

Circuit

Systems, Inc.

ICS954204

0933D—03/16/05

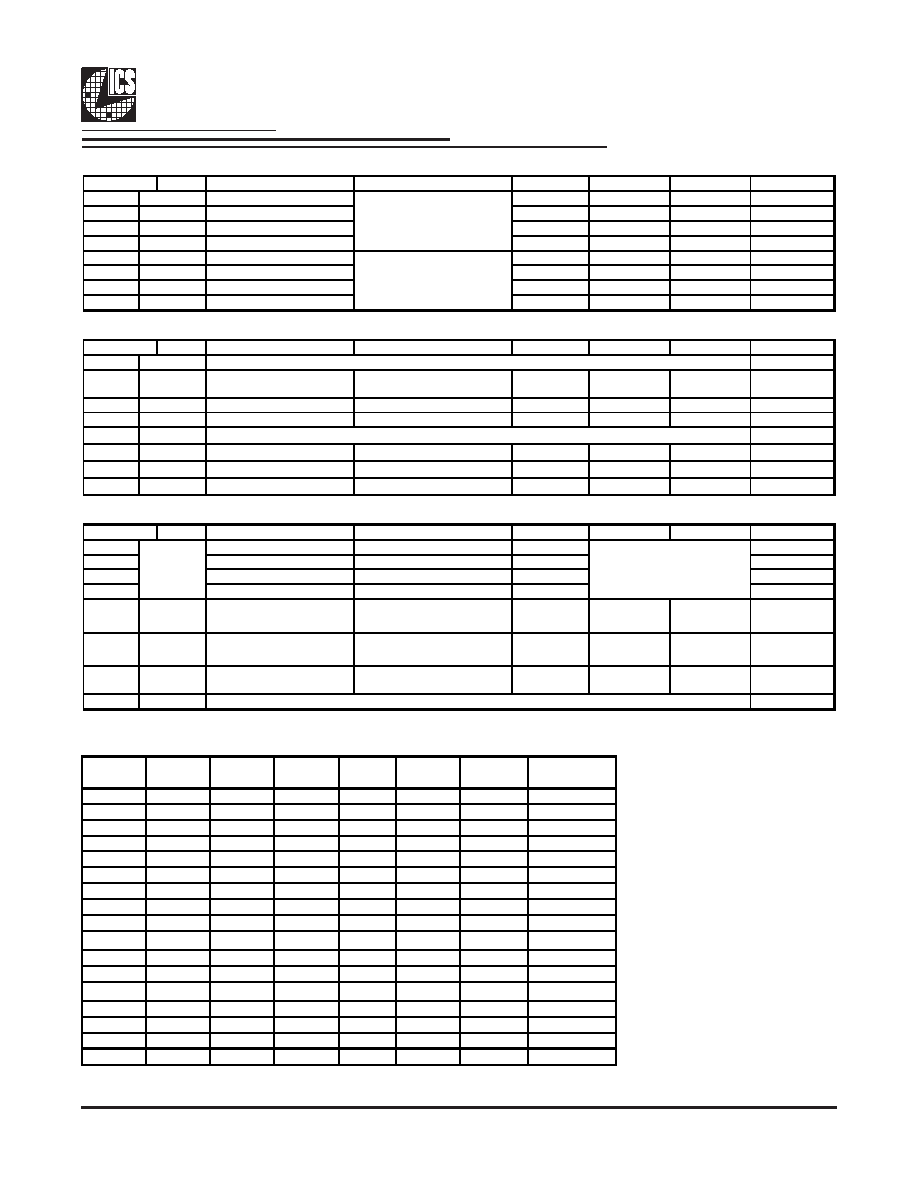

SMBus Table: Vendor & Revision ID Register

Pin #

Nam e

Control Function

Type

0

1

PWD

Bit 7

RID3

R

-

x

Bit 6

RID2

R

-

x

Bit 5

RID1

R

-

x

Bit 4

RID0

R

-

x

Bit 3

VID3

R

-

0

Bit 2

VID2

R

-

0

Bit 1

VID1

R

-

0

Bit 0

VID0

R

-

1

SMBus Table: Clock Request Control Register

Pin #

Nam e

Control

Type

0

1

PWD

Bit 7

-

Bit 6

CLKREQ B# Control

SRCCLK5 is controlled

RW

Not Controlled

Controlled

1

Bit 5

CLKREQ B# Control

SRCCLK3 is c ontrolled

RW

Not Controlled

Controlled

0

Bit 4

CLKREQ B# Control

SRCCLK1 is c ontrolled

RW

Not Controlled

Controlled

0

Bit 3

-

Bit 2

CLKREQ A# Control

SRCCLK4 is controlled

RW

Not Controlled

Controlled

1

Bit 1

CLKREQ A# Control

SRCCLK2 is c ontrolled

RW

Not Controlled

Controlled

0

Bit 0

CLKREQ A# Control

SRCCLK0 is c ontrolled

RW

Not Controlled

Controlled

0

SMBus Table: LCDCLK_SS Control Register

Pin #

Nam e

Control

Type

0

1

PWD

Bit 7

LCDCLK_SS3

Bit S3

RW

0

Bit 6

LCDCLK_SS2

Bit S2

RW

1

Bit 5

LCDCLK_SS1

Bit S1

RW

1

Bit 4

LCDCLK_SS0

Bit S0

RW

1

Bit 3

*SEL SRC_LCDCLK#

Select

LCDCLK_SS/SRCCLK0

R

LCDCLK

SRCCLK0

-

Bit 2

LCDCLK_SS/SRCCLK0

Enable

O utput Enable

RW

Dis able (HiZ)

Enable

1

Bit 1

LCDCLK_SS Spread

Enable

Enable SS

RW

O FF

O N

1

Bit 0

0

Res erv ed

REVISIO N ID

33

-

Byte 8

-

VENDO R ID

-

32

-

Byte 7

-

Byte 9

See LCDCLK_SS Frequenc y

Selec t Table 2

17,18

Res erv ed

9

17, 18

-

Byte9/

bit1

S3

S2

S1

S0

Pin 17/18

MHz

Spread % Spread Type

0

X

100.00

-

1000

0

100.00

0.8

Down

1000

1

100.00

1

Down

1001

0

100.00

1.25

Down

1001

1

100.00

1.5

Down

1010

0

100.00

1.75

Down

1010

1

100.00

2

Down

1011

0

100.00

2.5

Down

1011

1

100.00

3

Down

1100

0

100.00

+/-0.3

Center

1100

1

100.00

+/-0.4

Center

1101

0

100.00

+/-0.5

Center

1101

1

100.00

+/-0.6

Center

1110

0

100.00

+/-0.8

Center

1110

1

100.00

+/-1.0

Center

1111

0

100.00

+/-1.25

Center

1111

1

100.00

+/-1.5

Center

Table 2: LCDCLK_SS Frequency Select

相关PDF资料 |

PDF描述 |

|---|---|

| ICS954321YG-T | 400 MHz, PROC SPECIFIC CLOCK GENERATOR, PDSO64 |

| ICS954321YGLF-T | 400 MHz, PROC SPECIFIC CLOCK GENERATOR, PDSO64 |

| ICS95V2F857AG-130T | PLL BASED CLOCK DRIVER, 10 TRUE OUTPUT(S), 0 INVERTED OUTPUT(S), PDSO48 |

| ICS95V847AG-T | 95V SERIES, PLL BASED CLOCK DRIVER, 5 TRUE OUTPUT(S), 0 INVERTED OUTPUT(S), PDSO24 |

| ICS95V847AGLF-T | 95V SERIES, PLL BASED CLOCK DRIVER, 5 TRUE OUTPUT(S), 0 INVERTED OUTPUT(S), PDSO24 |

相关代理商/技术参数 |

参数描述 |

|---|---|

| ICS954206AG | 功能描述:IC TIMING CTRL HUB P4 56-TSSOP RoHS:否 类别:集成电路 (IC) >> 时钟/计时 - 专用 系列:PCI Express® (PCIe) 标准包装:1,500 系列:- 类型:时钟缓冲器/驱动器 PLL:是 主要目的:- 输入:- 输出:- 电路数:- 比率 - 输入:输出:- 差分 - 输入:输出:- 频率 - 最大:- 电源电压:3.3V 工作温度:0°C ~ 70°C 安装类型:表面贴装 封装/外壳:28-SSOP(0.209",5.30mm 宽) 供应商设备封装:28-SSOP 包装:带卷 (TR) 其它名称:93786AFT |

| ICS954206AGLF | 功能描述:IC TIMING CTRL HUB P4 56-TSSOP RoHS:是 类别:集成电路 (IC) >> 时钟/计时 - 专用 系列:PCI Express® (PCIe) 标准包装:1,500 系列:- 类型:时钟缓冲器/驱动器 PLL:是 主要目的:- 输入:- 输出:- 电路数:- 比率 - 输入:输出:- 差分 - 输入:输出:- 频率 - 最大:- 电源电压:3.3V 工作温度:0°C ~ 70°C 安装类型:表面贴装 封装/外壳:28-SSOP(0.209",5.30mm 宽) 供应商设备封装:28-SSOP 包装:带卷 (TR) 其它名称:93786AFT |

| ICS954206AGLFT | 功能描述:IC TIMING CTRL HUB P4 56-TSSOP RoHS:是 类别:集成电路 (IC) >> 时钟/计时 - 专用 系列:PCI Express® (PCIe) 标准包装:28 系列:- 类型:时钟/频率发生器 PLL:是 主要目的:Intel CPU 服务器 输入:时钟 输出:LVCMOS 电路数:1 比率 - 输入:输出:3:22 差分 - 输入:输出:无/是 频率 - 最大:400MHz 电源电压:3.135 V ~ 3.465 V 工作温度:0°C ~ 85°C 安装类型:表面贴装 封装/外壳:64-TFSOP (0.240",6.10mm 宽) 供应商设备封装:64-TSSOP 包装:管件 |

| ICS954206AGT | 功能描述:IC TIMING CTRL HUB P4 56-TSSOP RoHS:否 类别:集成电路 (IC) >> 时钟/计时 - 专用 系列:PCI Express® (PCIe) 标准包装:1,500 系列:- 类型:时钟缓冲器/驱动器 PLL:是 主要目的:- 输入:- 输出:- 电路数:- 比率 - 输入:输出:- 差分 - 输入:输出:- 频率 - 最大:- 电源电压:3.3V 工作温度:0°C ~ 70°C 安装类型:表面贴装 封装/外壳:28-SSOP(0.209",5.30mm 宽) 供应商设备封装:28-SSOP 包装:带卷 (TR) 其它名称:93786AFT |

| ICS954206BF | 功能描述:IC TIMING CTRL HUB P4 56-SSOP RoHS:否 类别:集成电路 (IC) >> 时钟/计时 - 专用 系列:TCH™, PCI Express® (PCIe) 标准包装:1,500 系列:- 类型:时钟缓冲器/驱动器 PLL:是 主要目的:- 输入:- 输出:- 电路数:- 比率 - 输入:输出:- 差分 - 输入:输出:- 频率 - 最大:- 电源电压:3.3V 工作温度:0°C ~ 70°C 安装类型:表面贴装 封装/外壳:28-SSOP(0.209",5.30mm 宽) 供应商设备封装:28-SSOP 包装:带卷 (TR) 其它名称:93786AFT |

发布紧急采购,3分钟左右您将得到回复。