- 您现在的位置:买卖IC网 > PDF目录79612 > ICS95V157AGI (INTEGRATED DEVICE TECHNOLOGY INC) 95V SERIES, PLL BASED CLOCK DRIVER, 10 TRUE OUTPUT(S), 0 INVERTED OUTPUT(S), PDSO48 PDF资料下载

参数资料

| 型号: | ICS95V157AGI |

| 厂商: | INTEGRATED DEVICE TECHNOLOGY INC |

| 元件分类: | 时钟及定时 |

| 英文描述: | 95V SERIES, PLL BASED CLOCK DRIVER, 10 TRUE OUTPUT(S), 0 INVERTED OUTPUT(S), PDSO48 |

| 封装: | 0.240 INCH, MO-153, TSSOP-48 |

| 文件页数: | 7/11页 |

| 文件大小: | 235K |

| 代理商: | ICS95V157AGI |

5

ICS95V157

0501B—12/02/03

Notes:

1.

Refers to transition on noninverting output in PLL bypass mode.

2.

While the pulse skew is almost constant over frequency, the duty cycle error

increases at higher frequencies.This is due to the formula: duty cycle=twH/tc, where

the cycle (tc) decreases as the frequency goes up.

3.

Switching characteristics guaranteed for application frequency range.

4.

Static phase offset shifted by design.

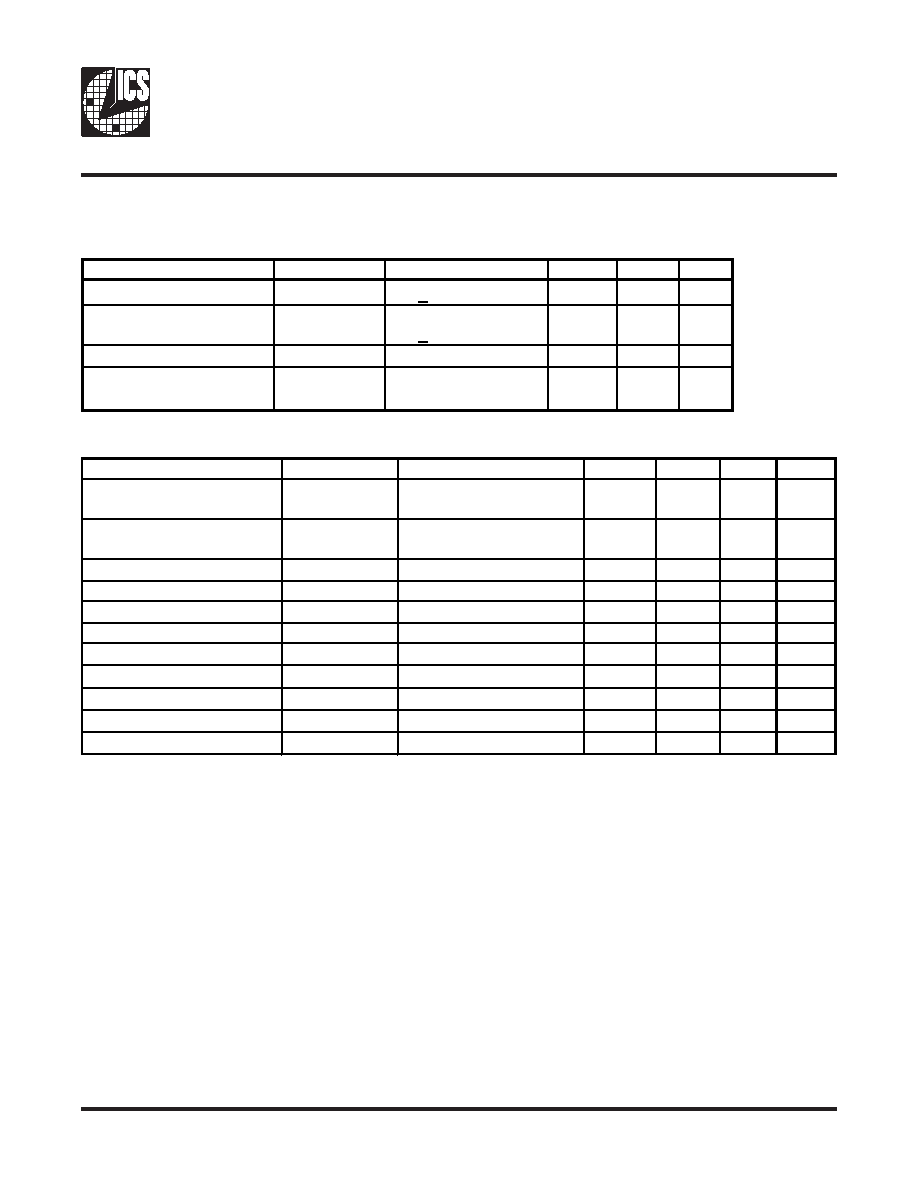

Timing Requirements

TA = 0 - 85°C; Supply Voltage AVDD, VDD = 2.5 V +/- 0.2V (unless otherwise stated)

PARAMETER

SYMBOL

CONDITIONS

MIN

MAX

UNITS

Max clock frequency

freqop

2.5V+0.2V @ 25

oC

45

233

MHz

Application Frequency

Range

freqApp

2.5V+0.2V @ 25

oC

95

210

MHz

Input clock duty cycle

dtin

40

60

%

CLK stabilization

TSTAB

15

s

Switching Characteristics (see note 3)

PARAMETER

SYMBOL

CONDITION

MIN

TYP

MAX

UNITS

Low-to high level

propagation delay time

tPLH

1

CLK_IN to any output

5.5

ns

High-to low level propagation

delay time

tPLL

1

CLK_IN to any output

5.5

ns

Output enable time

tEN

PD# to any output

5

ns

Output disable time

tdis

PD# to any output

5

ns

Period jitter

Tjit (per)

100MHz to 200MHz

-30

30

ps

Half-period jitter

t(jit_hper)

100MHz to 200MHz

-75

30

ps

Input clock slew rate

tsl(i)

14

V/ns

Output clock slew rate

tsl(o)

12.5

V/ns

Cycle to Cycle Jitter

1

Tcyc-Tcyc

100MHz to 200MHz

60

ps

Phase error

t(phase error)

4

-50

0

50

ps

Output to Output Skew

Tskew

60

ps

相关PDF资料 |

PDF描述 |

|---|---|

| ICS95V2F857AGT | 95V SERIES, PLL BASED CLOCK DRIVER, 10 TRUE OUTPUT(S), 0 INVERTED OUTPUT(S), PDSO48 |

| ICS95V857AGI-T | PLL BASED CLOCK DRIVER, 10 TRUE OUTPUT(S), 0 INVERTED OUTPUT(S), PDSO48 |

| ICS95VLP857AK-T | PLL BASED CLOCK DRIVER, 10 TRUE OUTPUT(S), 0 INVERTED OUTPUT(S), PQCC40 |

| IDT9DB801CGLFT | 9DB SERIES, PLL BASED CLOCK DRIVER, 8 TRUE OUTPUT(S), 0 INVERTED OUTPUT(S), PDSO48 |

| ICS95V857CG | 95V SERIES, PLL BASED CLOCK DRIVER, 10 TRUE OUTPUT(S), 0 INVERTED OUTPUT(S), PDSO48 |

相关代理商/技术参数 |

参数描述 |

|---|---|

| ICS95V157AGIT | 功能描述:IC CLK BUFF 1:10 233MHZ 48-TSSOP RoHS:否 类别:集成电路 (IC) >> 时钟/计时 - 时钟缓冲器,驱动器 系列:- 标准包装:1 系列:HiPerClockS™ 类型:扇出缓冲器(分配),多路复用器 电路数:1 比率 - 输入:输出:2:18 差分 - 输入:输出:是/无 输入:CML,LVCMOS,LVPECL,LVTTL,SSTL 输出:LVCMOS,LVTTL 频率 - 最大:250MHz 电源电压:2.375 V ~ 3.465 V 工作温度:0°C ~ 70°C 安装类型:表面贴装 封装/外壳:32-LQFP 供应商设备封装:32-TQFP(7x7) 包装:- 其它名称:800-1923-6 |

| ICS95V157AGLF | 功能描述:IC CLK BUFF 1:10 233MHZ 48-TSSOP RoHS:是 类别:集成电路 (IC) >> 时钟/计时 - 时钟缓冲器,驱动器 系列:- 标准包装:74 系列:- 类型:扇出缓冲器(分配) 电路数:1 比率 - 输入:输出:1:10 差分 - 输入:输出:是/是 输入:HCSL, LVCMOS, LVDS, LVPECL, LVTTL 输出:HCSL,LVDS 频率 - 最大:400MHz 电源电压:3 V ~ 3.6 V 工作温度:-40°C ~ 85°C 安装类型:表面贴装 封装/外壳:32-VFQFN 裸露焊盘 供应商设备封装:32-QFN(5x5) 包装:管件 |

| ICS95V157AGLFT | 功能描述:IC CLK BUFF 1:10 233MHZ 48-TSSOP RoHS:是 类别:集成电路 (IC) >> 时钟/计时 - 时钟缓冲器,驱动器 系列:- 标准包装:74 系列:- 类型:扇出缓冲器(分配) 电路数:1 比率 - 输入:输出:1:10 差分 - 输入:输出:是/是 输入:HCSL, LVCMOS, LVDS, LVPECL, LVTTL 输出:HCSL,LVDS 频率 - 最大:400MHz 电源电压:3 V ~ 3.6 V 工作温度:-40°C ~ 85°C 安装类型:表面贴装 封装/外壳:32-VFQFN 裸露焊盘 供应商设备封装:32-QFN(5x5) 包装:管件 |

| ICS95V157AGT | 功能描述:IC CLK BUFF 1:10 233MHZ 48-TSSOP RoHS:否 类别:集成电路 (IC) >> 时钟/计时 - 时钟缓冲器,驱动器 系列:- 标准包装:74 系列:- 类型:扇出缓冲器(分配) 电路数:1 比率 - 输入:输出:1:10 差分 - 输入:输出:是/是 输入:HCSL, LVCMOS, LVDS, LVPECL, LVTTL 输出:HCSL,LVDS 频率 - 最大:400MHz 电源电压:3 V ~ 3.6 V 工作温度:-40°C ~ 85°C 安装类型:表面贴装 封装/外壳:32-VFQFN 裸露焊盘 供应商设备封装:32-QFN(5x5) 包装:管件 |

| ICS95V2F857AGLF | 功能描述:IC CLK DVR 2.5V 48-TSSOP RoHS:是 类别:集成电路 (IC) >> 时钟/计时 - 专用 系列:- 标准包装:1,500 系列:- 类型:时钟缓冲器/驱动器 PLL:是 主要目的:- 输入:- 输出:- 电路数:- 比率 - 输入:输出:- 差分 - 输入:输出:- 频率 - 最大:- 电源电压:3.3V 工作温度:0°C ~ 70°C 安装类型:表面贴装 封装/外壳:28-SSOP(0.209",5.30mm 宽) 供应商设备封装:28-SSOP 包装:带卷 (TR) 其它名称:93786AFT |

发布紧急采购,3分钟左右您将得到回复。