- 您现在的位置:买卖IC网 > PDF目录9543 > ICS97ULP877BH (IDT, Integrated Device Technology Inc)IC CLOCK DRIVER 1.8V LP 52-BGA PDF资料下载

参数资料

| 型号: | ICS97ULP877BH |

| 厂商: | IDT, Integrated Device Technology Inc |

| 文件页数: | 1/14页 |

| 文件大小: | 0K |

| 描述: | IC CLOCK DRIVER 1.8V LP 52-BGA |

| 产品变化通告: | Product Discontinuation 09/Dec/2011 |

| 标准包装: | 325 |

| 类型: | 时钟缓冲器/驱动器,零延迟缓冲器,多路复用器 |

| PLL: | 是 |

| 主要目的: | 存储器,DDR2 |

| 输入: | 时钟 |

| 输出: | SSTL-18 |

| 电路数: | 1 |

| 比率 - 输入:输出: | 1:10 |

| 差分 - 输入:输出: | 是/是 |

| 频率 - 最大: | 410MHz |

| 电源电压: | 1.7 V ~ 1.9 V |

| 工作温度: | 0°C ~ 70°C |

| 安装类型: | 表面贴装 |

| 封装/外壳: | 52-VFBGA |

| 供应商设备封装: | 52-CABGA(4.5x7.0) |

| 包装: | 托盘 |

| 其它名称: | 97ULP877BH |

Integrated

Circuit

Systems, Inc.

ICS97ULP8 77B

0981C—04/05/05

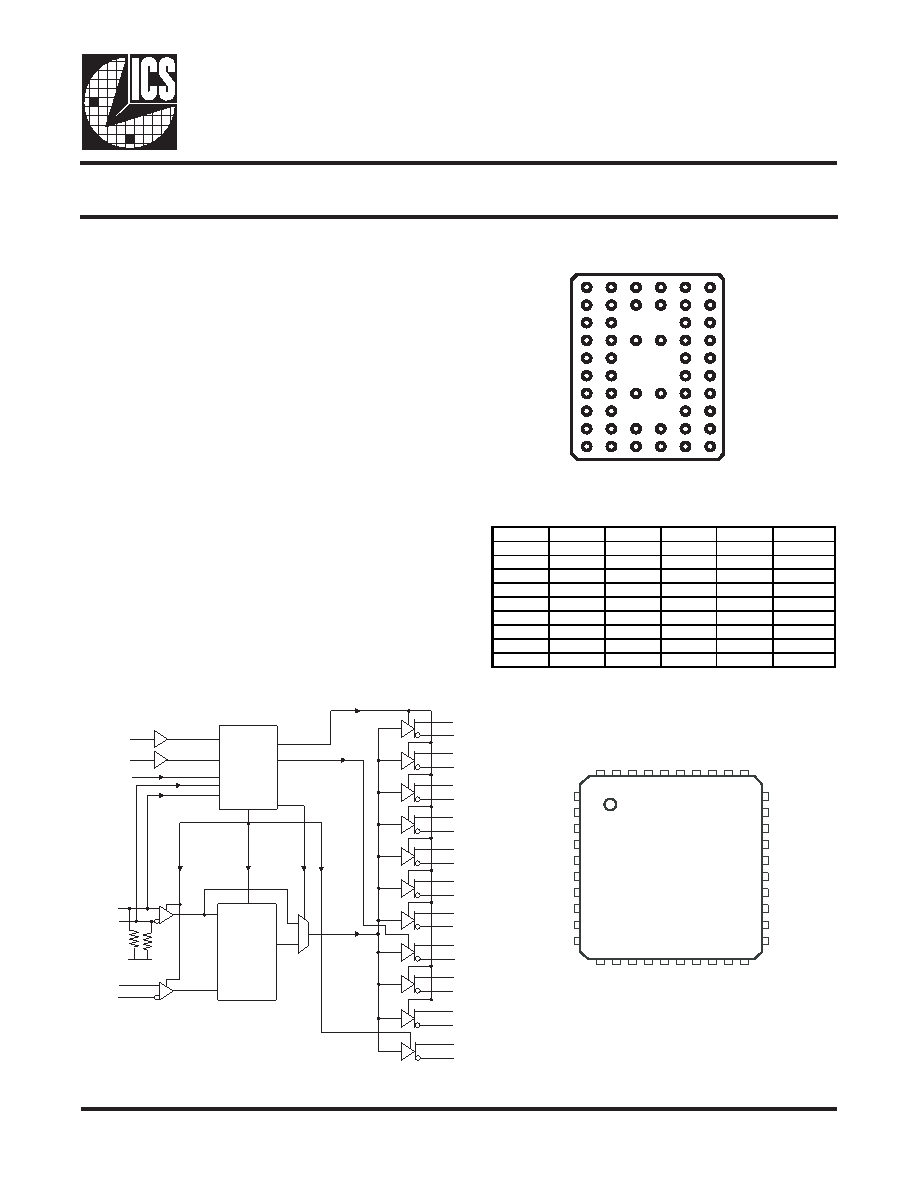

Block Diagram

1.8V Low-Power Wide-Range Frequency Clock Driver

Pin Configuration

40-Pin MLF

Recommended Application:

DDR2 Memory Modules / Zero Delay Board Fan Out

Provides complete DDR DIMM logic solution with

ICSSSTU32864/SSTUF32864/SSTUF32866/

SSTUA32864/SSTUA32866/SSTUA32S868/

SSTUA32S865/SSTUA32S869

Product Description/Features:

Low skew, low jitter PLL clock driver

1 to 10 differential clock distribution (SSTL_18)

Feedback pins for input to output synchronization

Spread Spectrum tolerant inputs

Auto PD when input signal is at a certain logic state

Switching Characteristics:

Period jitter: 40ps (DDR2-400/533)

30ps (DDR2-667/800)

Half-period jitter: 60ps (DDR2-400/533)

50ps (DDR2-667/800)

OUTPUT - OUTPUT skew: 40ps (DDR2-400/533)

30ps (DDR2-667/800)

CYCLE - CYCLE jitter 40ps

A

B

123456

C

D

E

F

G

H

J

K

52-Ball BGA

Top View

CLKT0

CLKC0

CLKT1

CLKC1

CLKT2

CLKC2

CLKT3

CLKC3

CLKT4

CLKC4

CLKT5

CLKC5

CLKT6

CLKC6

CLKT7

CLKC7

CLKT8

CLKC8

CLKT9

CLKC9

FB_OUTT

FB_OUTC

AV

DD

FB_INT

CLK_INT

CLK_INC

FB_INC

PLL

Powerdown

Control and

Test Logic

OE

LD* or OE

PLL bypass

LD*

LD*, OS or OE

OS

GND

10K-100k

* The Logic Detect (LD) powers down the device when a

logic low is applied to both CLK_INT and CLK_INC.

VDDQ

CLKC2

CLKT2

CLK_INT

CLK_INC

VDDQ

AGND

AVDD

VDDQ

GND

CLKC7

CLKT7

VDDQ

FB_INT

FB_INC

FB_OUTC

FB_OUTT

VDDQ

OE

OS

CLKT3

CLKC3

CLKC4

CLKT4

VDDQ

CLKT

9

CLKC

9

CLKC8

CLKT8

VDDQ

CLKC1

CLKT1

CLKT0

CLKC0

VDDQ

CLKC5

CLKT5

CLKT6

CLKC6

VDDQ

1

10

11

20

21

31

30

40

ICS97ULP877B

1234

5

6

A

CLKT1

CLKT0

CLKC0

CLKC5

CLKT5

CLKT6

B

CLKC1

GND

CLKC6

C

CLKC2

GND

NB

GND

CLKC7

D

CLKT2

VDDQ

OS

CLKT7

E

CLK_INT

VDDQ

NB

VDDQ

FB_INT

F

CLK_INC

VDDQ

NB

OE

FB_INC

G

AGND

VDDQ

FB_OUTC

H

AVDD

GND

NB

GND

FB_OUTT

J

CLKT3

GND

CLKT8

K

CLKC3

CLKC4

CLKT4

CLKT9

CLKC9

CLKC8

相关PDF资料 |

PDF描述 |

|---|---|

| CS3100A-22-77P | CONN RCPT 14POS WALL MNT W/PINS |

| D38999/26KJ4PA | CONN PLUG 56POS STRAIGHT W/PINS |

| ICS97ULP877AHLFT | IC CLOCK DRIVER 1.8V LP 52-BGA |

| ICS97ULP877AHLF | IC CLOCK DRIVER 1.8V LP 52-BGA |

| CS3106A-22-84P | CONN PLUG 9POS STRAIGHT W/PINS |

相关代理商/技术参数 |

参数描述 |

|---|---|

| ICS97ULP877BHLF | 功能描述:IC CLK DVR 1.8V LP WIDE 52-BGA RoHS:是 类别:集成电路 (IC) >> 时钟/计时 - 专用 系列:- 标准包装:1 系列:- 类型:时钟/频率发生器,多路复用器 PLL:是 主要目的:存储器,RDRAM 输入:晶体 输出:LVCMOS 电路数:1 比率 - 输入:输出:1:2 差分 - 输入:输出:无/是 频率 - 最大:400MHz 电源电压:3 V ~ 3.6 V 工作温度:0°C ~ 85°C 安装类型:表面贴装 封装/外壳:16-TSSOP(0.173",4.40mm 宽) 供应商设备封装:16-TSSOP 包装:Digi-Reel® 其它名称:296-6719-6 |

| ICS97ULP877BHLFT | 功能描述:IC CLOCK DRIVER 1.8V LP 52-BGA RoHS:是 类别:集成电路 (IC) >> 时钟/计时 - 专用 系列:- 标准包装:28 系列:- 类型:时钟/频率发生器 PLL:是 主要目的:Intel CPU 服务器 输入:时钟 输出:LVCMOS 电路数:1 比率 - 输入:输出:3:22 差分 - 输入:输出:无/是 频率 - 最大:400MHz 电源电压:3.135 V ~ 3.465 V 工作温度:0°C ~ 85°C 安装类型:表面贴装 封装/外壳:64-TFSOP (0.240",6.10mm 宽) 供应商设备封装:64-TSSOP 包装:管件 |

| ICS97ULP877BHT | 功能描述:IC CLOCK DRIVER 1.8V LP 52-BGA RoHS:否 类别:集成电路 (IC) >> 时钟/计时 - 专用 系列:- 标准包装:1,500 系列:- 类型:时钟缓冲器/驱动器 PLL:是 主要目的:- 输入:- 输出:- 电路数:- 比率 - 输入:输出:- 差分 - 输入:输出:- 频率 - 最大:- 电源电压:3.3V 工作温度:0°C ~ 70°C 安装类型:表面贴装 封装/外壳:28-SSOP(0.209",5.30mm 宽) 供应商设备封装:28-SSOP 包装:带卷 (TR) 其它名称:93786AFT |

| ICS97ULP877BKLF | 功能描述:IC CLOCK DRIVER 1.8V LP 40VFQFPN RoHS:是 类别:集成电路 (IC) >> 时钟/计时 - 专用 系列:- 标准包装:1,500 系列:- 类型:时钟缓冲器/驱动器 PLL:是 主要目的:- 输入:- 输出:- 电路数:- 比率 - 输入:输出:- 差分 - 输入:输出:- 频率 - 最大:- 电源电压:3.3V 工作温度:0°C ~ 70°C 安装类型:表面贴装 封装/外壳:28-SSOP(0.209",5.30mm 宽) 供应商设备封装:28-SSOP 包装:带卷 (TR) 其它名称:93786AFT |

| ICS97ULP877BKLFT | 功能描述:IC CLOCK DRIVER 1.8V LP 40VFQFPN RoHS:是 类别:集成电路 (IC) >> 时钟/计时 - 专用 系列:- 标准包装:1,500 系列:- 类型:时钟缓冲器/驱动器 PLL:是 主要目的:- 输入:- 输出:- 电路数:- 比率 - 输入:输出:- 差分 - 输入:输出:- 频率 - 最大:- 电源电压:3.3V 工作温度:0°C ~ 70°C 安装类型:表面贴装 封装/外壳:28-SSOP(0.209",5.30mm 宽) 供应商设备封装:28-SSOP 包装:带卷 (TR) 其它名称:93786AFT |

发布紧急采购,3分钟左右您将得到回复。